- No category

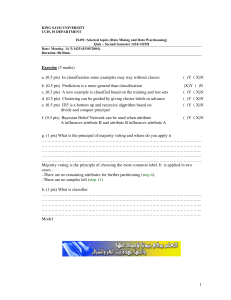

VLSI PD Commands & Scripts: Encounter & ICC2 Tools

advertisement

03/01/2024, 00:15

VLSI PD

More

shivashivakumar81@gmail.com

Dashboard

Sign Out

VLSI PD

WEDNESDAY, JANUARY 22, 2020

ABOUT ME

swamy

View my complete profile

ENCOUNTER COMMANDS

BLOG ARCHIVE

▼ 2020 (1)

To select all the ports in the design

selectIOPin *

▼ January (1)

ENCOUNTER COMMANDS To select

all the por...

To display all the contents in the shell window

enc_tcl_return_display_limit value

► 2019 (3)

► 2018 (2)

To get the direction of ports

get_attribute [get_pins *] direction

To get the output ports name

all_outputs

get_attribute [get_pins * -filter "direction==out"] name

To get the input ports name

all_inputs

get_attribute [get_pins * -filter "direction==in"] name

To filter weather a port is signal or clock port

To select all the instances in the design

selectInst *

To get the instance names in the design

get_cells *

get_cells * -hierarchical

get_attribute [get_cells * -hierarchical] hierarchical_name

To get all the net names in the design

get_nets *

get_nets * -hierarchical

To get all the combinational cells in the design

get_attribute [get_cells * -hierarchical -filter "is_combinational==true"] hierarchical_name

To check weather a cell is combinational or not

get_attribute [get_cells tem_mbist4/l_releasclk_reg/g16] is_combinational

To get all the sequential cells in the design

get_attribute [get_cells * -hierarchical -filter "is_sequential==true"] hierarchical_name

get_attribute [get_cells tem_mbist4/l_releasclk_reg/g16] is_sequential

To get the no. of pins of an instance

get_attribute [get_cells tem_mbist4/l_releasclk_reg/g16] pin_count

To get the library cell name of an instance

get_attribute [get_cells tem_mbist4/l_releasclk_reg/g16] ref_lib_cell_name

To get only sequential cells excluding memories

get_attribute [get_cells * -hierarchical -filter "is_memory_cell==false && is_sequential==true"] hierarchial_name

Posted by swamy at 11:34 PM

No comments:

WEDNESDAY, SEPTEMBER 4, 2019

Scripts for ICCII:

Below all commands are for ICC2 tool so u can replace that commands with your tool commands.

Script for dump all cell ref name in the design.

set fp [open spacer_create.tcl w]

foreach A $AA {

set cell [get_attribute [get_cell $A] full_name ]

set ref [get_attribute [get_cell $A] ref_name]

puts $fp "create_cell $cell */$ref"

close $fp

}

Script for to change instance name of cells in the design

set fp [open spacer_create_new.tcl w]

set i 1

https://vlsipdforfreshers.blogspot.com

1/7

03/01/2024, 00:15

VLSI PD

foreach A $AA {

set cell [get_attribute [get_cell $A] full_name ]

puts $fp "change_names -instance $cell -new_name inst_pad_spacer_sp$i"

incr i

}

close $fp

For to draw a net along with on one ESD cell:

First create logical connectivy before sourcing this command

VSS

foreach bbox [get_attribute [get_shapes -of_objects [get_pins -of_objects VSS -filter "port_type == ground"] -filter "layer.name == M9"] bbox] {

create_shape -net VSS -boundary $bbox -layer M10 -shape_type rect

create_pg_vias -allow_parallel_objects -from_layers M9 -to_layers M10 -nets VSS -within_bbox $bbox

}

POWER

foreach bbox [get_attribute [get_shapes -of_objects [get_pins -of_objects VDD netname -filter "port_type == power"] -filter "layer.name == M9"] bbox] {

create_shape -net VDD netname -boundary $bbox -layer M10 -shape_type rect

create_pg_vias -allow_parallel_objects -from_layers M9 -to_layers M10 -nets VDD netname -within_bbox $bbox

}

To get ref names & orientation

set cell [get_cells {<instance names>}]

foreach_in_collection cells [get_cells $cell] {

set ref [get_attribute $cells ref_name]

set ori [get_attribute $cells orientation]

puts "$ref$ori"

} > filename.tcl

Tcl file for logical connectivity.

change_selection [get_cells *BUMP*]

set r [get_object_name [get_pins -of_objects [get_selection ]]]

foreach i $r {

set b [get_object_name [get_nets -of_objects $i]]

puts "$i $b"

}

For to dump [net name] [pin name] [no of pins] [pins layer name] to a tcl file

set values {net names}

puts "net name\t pin_name\t\t\t\t\t\t\t\t\t\t\t\t\t\t\t\t\t no.of_pins\t\t\t\t layer_name"

foreach x $values {

set p [get_object_name [get_pins -of_objects [get_nets $x]]]

set q [sizeof_collection [get_pins -of_objects [get_nets $x]]]

set r [get_attribute [get_pins -of_objects [get_nets $x]] layer_name]

puts " $x\t $p\t $q\t\t $r"

} > filename.tcl

Posted by swamy at 2:15 AM

1 comment:

MONDAY, AUGUST 5, 2019

Xterm terminal basic commands

sh xterm -bg black &---->for to change terminal background color

sh xterm -fg white -bg black &------>for to change terminal text and color

Tkdiff 1st tcl file 2nd tcl file ------------>for to compare 2 file parlelly

:set hls----------------->for to highlight error

:3,8w filename------>it will dump from line 3 to line 8 in a new a file

-c "100,200w new_file.txt" -c wq original_file.txt----->it will dump from line 3 to line 8 in a new a file

cd $WARD ------------------>for to know the word area

df -kh--------------------------->for to know disk size and disk area

Df -hs--------------->

:se nu----> for to give number

:se nonu---->for to remove number

:set nowrap ---->for to separate the word with space

grep -h /PAD filepath ------>will give PAD word all line in that file

sh gvim +10 net_names.tcl------>it will open the file and point the 10 th line onwards

:r filename t1---->if u want to dump t1 file data in t2 file use this one.u have to use this cmnd in by opening t2 file

Shift+up arrow---->goto line home position

Shift+$---------> goto line End position

ls -R | grep .filetype(.spef,.rpt)------------------->it will list specific type of files

ls -l -R | grep .filetype(.spef,.rpt)------------------->it will list specific type of files with file permissions

Explain CHMODE:

In chmod total 10 hifuns( symbol - )----->will be there

In that 1st hifun indicate file

Next 3 hifun indicate user

How to insert something in line on before first word ?

First open that file then go to that line keep ur cursor on first word of that line

https://vlsipdforfreshers.blogspot.com

2/7

03/01/2024, 00:15

VLSI PD

then press ESC now press CNTL+V

now press down arrow up to which line u required

then press Shift+I now type the word u required then press Esc.

Posted by swamy at 2:35 AM

No comments:

ICC2 Tool Commands

How to add ndms in ref_libs

Open block.tcl file

Report_ref_libs information dump in a new tcl file

Now go to icc2shell

set_ref_libs -add missed ndm file---> from block.tcl file

set_ref_libs -rebind

link_block -force

report_ref_libs

save_block

save_lib

How to resolve upf error ?

commit_upf

save_block

save_lib

How to move ESD cell with origin coordinates ?

move_objects [get_selection ] -to {7486.0965 3288.0000}

How to select all the cells which have net name VDD_1V2_IO ?

change_selection [get_cells -of_objects [get_net VDD_1V2_IO]]

Cmd for to check shorts

check_lvs -max_error 0 -checks short----->for to check shorts

How to add buffers

add_buffer -lib_cell ec0cbf000an1n20x5 -new_cell_names 01122019_cell -new_net_names 01122019_net [get_pins

lgcio_pch/giolgcpchtop/lgciopchdig/chaitanya_fix_3/clk]

For to check open nets for a specific net

check_lvs -checks open -nets {biss_bg_vref_out} -open_reporting detailed------>for to check opens of a specific net

How to load bumps

read_def -add_def_only_objects {cells nets ports} def file path

How to prepare Empty db

change_selection [get_cells *BUMP*]

remove_objects [get_selection ]

change_selection [get_shapes -of_objects -filter "layer_name==AP"]

change_selection [get_shapes -filter "layer_name==AP"]

change_selection [get_shapes -filter "layer_name==M11"]

change_selection [get_vias -filter "upper_layer_name==M11 || upper_layer_name==AP "]

remove_objects [get_selection ]

How to get def file?

Select whatever u need in tool then use below command

write_def -objects [get_selection] filename.def

How to load def?

First create empty db

Then use below command

read_def -add_def_only_objects {cells nets ports} def path

To create cell

create_cell inst_TMS_SWDIO */io_sndwire_fs_1v2_1v8_n1

move_objects [get_cell inst_1V8_SUP1V8_1 ] -to {4250.0000 0.0000}

To get cells

change_selection [get_cells -of_objects [get_nets VDD_DIG_BIS]]

sizeof_collection [get_cells]

To select all cells

lsort -u [get_attribute [get_selection ] object_class ]

Remove_cells [get_selection]

getting particular pins

get_pins par_opio/*xx*

connecting and disconnecting nets

Connect_net -net name pin name

Disconnect_net -net name pin name

cs [gp -of [gn vccvdd2_rpll_hv]]

get_nets -of_objects [gs]

How to remove terminals?

change_selection [get_terminals *]

remove_objects [get_selection]

https://vlsipdforfreshers.blogspot.com

3/7

03/01/2024, 00:15

VLSI PD

How to take routes with tcl

Off terminal,ports,cells

First select nets

Give get selection

Then take that net names and paste in this cmnd on braces

1.change_selection [get_shapes -of_objects [get_nets netname]] then u will get that net nets shapes

2.change_selection

[get_viass -of_objects [get_nets netname ]] -add

3. lsort -u [get_attribute [get_selection ] object_class ]

4.write_routes -objects [get_selection ] -output filename

To know width of the layer

ga [get_layer m9] min_width

For to remove cells from design

Remove_cellls [get_selection]

For to select that net shapes in specific Layer

change_selection [get_shapes -of_objects [get_net VDD_1V2_IO] -filter "layer_name==M10"]

For to know cell count

sizeof_collection [get_selection]

How to drop Vias in a perticular place by using commands.

By using bound option first create bound on that area

Next by using this command u can create vias for specific nets by selecting that bound

get_attribute [get_selection ] bbox

How to remove vias from a particular location

Here I am removing m10 vias

First draw bound on the area where u required.

Next use below commands

get_attribute [get_selection ] bbox

change_selection [get_vias -within {give bbox coordinates} -filter "upper_layer_name==M11 || upper_layer_name==M10"]

Posted by maddileti swamy at 1:56 AM

5 comments:

TUESDAY, OCTOBER 23, 2018

How to take route as a tcl file in ICC2.

first switch of pin,ports,terminal,cells.

then select all route in gui.

then come to chell and use this command

lsort -unique [get_attribute [get_selection] object_class]

shapes vias

Then it will show Shapes if u have any vias in ur route then it will show shapes and Vias

Then next use this command

write_routes -objects [get_selection] -output filename.tcl

now routes are generated as tcl file.

Posted by maddileti swamy at 12:19 AM

No comments:

SUNDAY, OCTOBER 7, 2018

Types of DRC's

The layout of a design must be in accordance with a set of predefined technology rules given by the foundry for manufacturability. After

completion of the layout and its physical connection, an automatic program will check each and every polygon in the design against these design

rules and report any violations. This whole process is called Design Rule Checking (DRC). There are many design rules at different technology

nodes, a few of which are mentioned below.

Types of DRCs:

Minimum width and spacing for metal

Minimum width and spacing for via

Fat wire Via keep out Enclosure

End of Line spacing

Minimum area

Over Max stack level

Wide metal jog

Misaligned Via wire

Different net spacing

Special notch spacing

Shorts violation

Different net Via cut spacing

Less than min edge length

Here are some of the practical problems and their solution for different types of DRCs and their solutions.

CASE A: Shorts violation

Description: In short violation, two or more different net segments of the same layer were crossing each other. Here is a practical problem of two

different nets in same metal layer crossing to each other as seen in the following pic.

https://vlsipdforfreshers.blogspot.com

4/7

03/01/2024, 00:15

VLSI PD

Solution:

To fix this type of short violation, different net segments on same layer has to be placed away so that they will not cross each other. In this case,

net adjusted net will not cross each other and also meet the spacing requirement in the same layer.

CASE B: Different Spacing violation

Description : In some cases, the via enclosure is quite large compared to metal width due to large via enclosure. Thee other long net passing

each other and dropped in via will create a different spacing violation.

Solution:

To fix this type of spacing violation, the net needs to be placed away from the via, or different size vias need to be inserted so it will meet the

same net spacing requirement. In above case, routing taken in reverse U shape will meet the spacing requirements as below.

CASE C: Same layer spacing with net and cell geometry blockage

Description: In this case, there is same layer spacing with the cell blockage and via enclosure

Highlighted in pic using white marker. Same net spacing in red color.

Solution:

In this case, to fix violation, the net is routed in non-preferred direction in green color inserted via so spacing is increased between cell blockage

and a net.

https://vlsipdforfreshers.blogspot.com

5/7

03/01/2024, 00:15

VLSI PD

CASE D: Minimum area requirement

Description: There is a minimum area requirement for every segment in a layout.

Solution:

To meet this minimum area requirement, we need to increase the area of the segment that will not violate the other design rule (spacing, short).

For this case I have increase the area where I was getting the violation shown below.

CASE E: VIA Misalignment

Description: This type violation pops up when two different layer of same logical net connected by inserting the VIA. If inserted via is not aligning

with the metal crossing we are seeing the VIA misalignment.

Solution:

Proper VIA instance need to insert so the VIA enclosure align layer in its direction properly and if needed we need to stretch the net and insert

the VIA.

After fixing the all DRC again we need to verify drc with different tool Caliber,Quartz before releasing to foundary because while fixing the drc

there may be a chances of populating the new DRC violation.

Posted by maddileti swamy at 9:45 AM

https://vlsipdforfreshers.blogspot.com

1 comment:

6/7

03/01/2024, 00:15

VLSI PD

Home

Subscribe to: Posts (Atom)

Picture Window theme. Powered by Blogger.

https://vlsipdforfreshers.blogspot.com

7/7

0

0

advertisement

Download

advertisement

Add this document to collection(s)

You can add this document to your study collection(s)

Sign in Available only to authorized usersAdd this document to saved

You can add this document to your saved list

Sign in Available only to authorized users