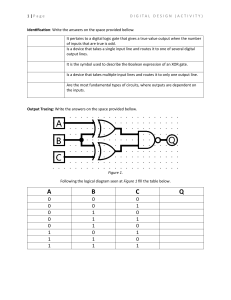

1)Design a 4 bit binary to gray code converters 2)Design of 4 bit binary to bcd converter 3)Design of 4 bit BCD to Excess-3 code converter 4)Design a full adder using NAND gates 5)Design a full adder using NOR gates 6)Design a combinational logic circuit with three input variables that will produce logic 1 output when more than one input variables are logic 0 7)Realize the Boolean expression f(A,B.C.D ) = Σm(4 5 7 8 10 12 15) using a 4-to-1 line multiplexer and external gates. 8)We have an eight-line to three-line priority encoder circuit with D0 , D1, D2 , D3 , D4 , D5 , D6 , and D7 as the data input lines, the output bits are A( MSB ), B and C( LSB ). Higher order data bits have been assigned a higher priority, with D7 having the highest priority. If the data inputs and outputs are active when LOW, determine the logic status of output bits for the following logic status of data inputs : (a) All inputs are in logic ‘0’ state. (b) D1 to D4 are in logic ‘1’ state and D5 to D7 are in logic ‘0’ state. (c) D7 is in logic ‘0’ state. The logic status of the other inputs is not known. Sol) (a) Since all inputs are in logic ‘0’ state, it implies that all inputs are active. Since D7 has the highest priority and all inputs and outputs are active when LOW, the output bits are A = 0, B = 0, and C = 0. (b) Inputs D5 to D7 are the ones that are active; among these, D7 has the higher priority. Therefore, the output bits are A = 0, B = 0 , and C = 0. (c) D7 is active. Since D7 has the highest priority, it will be encoded irrespective of the logic status of other inputs. Therefore, the output bits are A = 0, B = 0, and C = 0. 9)Implement the Boolean function F = Σm( 0,2,5,6,7) with a suitable decoder and an external OR/NOR gate having the minimum number of inputs. 10)Design a logic circuit with 4 inputs A, B, C , D that will produce output ‘1’ only whenever two adjacent input variables are 1’s. A and D are also to be treated as adjacent. Implement it using universal logic. 11)You are given a 2:4 decoder, a 2 input OR gate and a 3 input OR gate. Using these components design a system which takes A & B as inputs and generates the following four outputs: AB, (AB)' , A+B, (A+B)'. 12)Implement A+b`C` by using 3*8 line decoder 13)Design "OR" gate using HA's? The HA equations are, Cout = AB and Sum = A XOR B = AB’ + A’B Sum XOR Cout = Sum’ Cout + Cout’ Sum = (AB+A’B’) AB + (A’+B’) (A’B+AB’) = AB + A’B + AB’ = A + B So to get OR gate we need two HA. The Sum and Cout of fist HA are given as inputs to second HA. The Sum of second HA gives the A OR B. 14)Using DFFs and minimum no. of 2×1 Mux, implement the following XYZ flip-flop. X Y Z Q(t+1) 0001 0010 0100 0111 1 0 0 Q(t) 1 0 1 Q(t)` 1 1 0 Q(t)` 1 1 1 Q(t) Sol)From the given characteristic table, it is clear that if X=0, Q(t+1) = Y XNOR Z. If X =1 and if (Y XNOR Z), Q(t+1) = Q(t), else Q(t)’. So we need two 2:1 mux to generate Y XNOR Z. One to select Q(t) and Q(t)’ and one more to select between X=0 case and X=1 case. Total we need 4 2:1 mux. The design is shown here except the generation of Z’. 15) a)A AB flip flop has 4 operations: clear to 0, no change, compliment and set to 1, when inputs A and B are 00, 01, 10 and 11 respectively. Derive the characteristic equation? Sol)The characteristic table is shown below: A 0 0 1 1 B 0 1 0 1 Q(t+1) 0 Q(t) Q(t)` 1 The characteristic equation can be derived as, Q(t+1) = A Q(t)’ + B Q(t) b)Give the excitation table for the AB flip flop Sol)The excitation table for AB flip flop is, Q(t) Q(t+1) A B 0 0 0 X 0 1 1 X 1 0 X 0 1 1 X 1 c)Show how the AB flip-flop can be converted to a D flip-flop? Sol)To get D from flip-flop from AB flop, just connect A=B=D. We can prove this from the characteristic equation , Q(t+1) = D Q(t)’ + D Q(t) = D (1) = D 16)Design a 3-bit shift register using 2:1 Mux and D Flip Flops which shifts right if the control input, C = 0 and shifts left if C = 1? Sol)The shift register is shown below. If C = 0, the circuit shifts from IN -QA - QB - QC and If C = 1, the circuit shifts from IN -QC – QB-QA 17)A four bit shift register, which shifts data right Q0 -Q1 - Q2 - Q3, is shown in the above figure. The initial value for Q0, Q1, Q2, Q3 is 1000. (a) Write the 4 bit values for Q0, Q1, Q2 and Q3 after each clock pulse until the pattern 1000 reappears. (b) To what values should the shift register be initialized so that the pattern 1000 occurs after 2 clock pulses? Sol) 18)Design a counter using DFF that counts in the sequence: 0,4,2,7,0,4,2,7,0,4……?