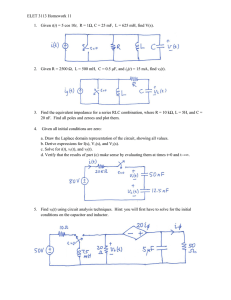

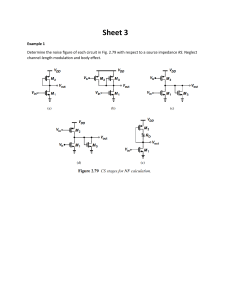

بسم هللا الرحمن الرحیم طراحی بردهای دیجیتال پرسرعت محتوای آموزشی – 14اصول تمامیت توان در شبکه توزیع توان دانشگاه صنعتی اصفهان نسرین رضائی 1 Engineering the Power Delivery Network 2 WHAT IS THE POWER DELIVERY NETWORK (PDN) AND WHY SHOULD I CARE? A typical computer motherboard with multiple VRMs (voltage regulator modules) and active devices. The PDN includes all the interconnects from the pads of the VRMs to the circuits on the die. Generally, these include the power and ground planes in the boards, cables, 3 connectors, and all the capacitors associated with the power supply. >>>>The purpose of the PDN is to • Distribute low-noise DC voltage and power to the active devices doing all the work. • Provide a low-noise return path for all the signals (minimize ground bounce). • Mitigate electromagnetic interference (EMI) problems without contributing to radiated emissions. سوال :چرا نویز روی خطوط تغدیه منجر به خطا در بیت دریافتی میشود؟ پاسخ :نویز روی خطوط تغذیه هم در دامنه داده ارسالی توسط فرستنده و هم در اندازه ولتاژ مرجع در گیرنده موثر هست. همچنین نویز روی خطوط تغذیه می تواند بحثهای زمانبندی ( )setup/hold timeخراب کند و از این جهت هم منجر به افزایش خطا می شود .حتی اگر دامنه نویز آنقدر نباشد که منجر به دریافت داده اشتباه شود ،حتما بودجه نویز مجاز و قابل قبول برای سایر بخشها را کاهش میدهد سوال :چرا نویز روی خطوط تغدیه منجر به تغییر تاخیر مدارها می شود؟ پاسخ :تاخیر یک کیت و مقاومت معادل ترانزیستور با اندازه ولتاژ تغییر میکند طراحی صحیح PDNمنجر به کاهش خطا در بیت دریافتی و نیزکاهش نویز جیتر میشود. 4 ENGINEERING THE PDN In some applications, such as analog-to-digital converters (ADCs) or phase locked loops (PLLs), performance is very sensitive to voltage noise and the PDN noise must be kept below 1%. The voltage noise must be kept below the limits from DC all the way up to the bandwidth of the signals, which might be as high as 5 GHz to 10 GHz. As with all signal integrity problems, the first step in eliminating them is to identify the root cause. At low frequency, the voltage noise across the PDN is usually due to the voltage noise from the VRM and so the first step in PDN design is selecting a VRM with low enough voltage noise under a suitable load current. However, even with the world’s most stable VRM, voltage noise still exists on the pads of the die. This arises from the voltage drop across the impedance of the entire PDN from transient power currents through the gates on the die. Between the pads of the VRM and the pads on the die are all the interconnects associated with the PDN. We refer to this entire network as the PDN ecology. 5 ENGINEERING THE PDN The PDN ecology is the entire series of interconnects from the pads on the die to the pads of the VRM. These all interact to create the impedance profile applied to the die and influence PDN noise. Example of an impedance profile of the entire PDN ecology, as applied to the pads of the die. 6 ENGINEERING THE PDN Left Side: PDN impedance profile and transient current spectrum result in acceptable voltage noise. Right Side: Slight change in current spectrum gives unacceptable voltage noise. 7 The actual voltage noise generated by the transient current through the impedance profile depends on the overlap of the current frequency components and the peaks in the impedance profile. If the voltage noise is below a specified level, PDN induced errors will not occur. If the microcode changes resulting current amplitude peaks and frequency component changes, their overlap with impedance peaks might create more voltage noise and product failure. “WORKING” OR “ROBUST” PDN DESIGN The variability in performance due to the specific microcode driving the switching of on-die gates makes testing a product for adequate PDN design difficult. A product might work just fine at boot up, or when running a specific software test suite if the combination of current spectral peaks and impedance peaks results in less than the specified transient noise. The product design may “pass” this test and be stamped as “working.” However, if another software suite were to run that drives more gates and causes them to switch at a different dominant loop frequency, which coincidently overlaps a peak in the PDN impedance profile, larger instantaneous voltage drops might result and the same product could fail. Although having the product boot up, run a test suite and apparently work is encouraging, it does not guarantee “robust” operation. Products often “work” in evaluation but have field failures when driven by a broad range of customer software. 8 “WORKING” OR “ROBUST” PDN DESIGN The combination of the worst-case transient current and the voltage noise specification work together to set a limit for the maximum allowable PDN impedance such that the voltage noise will never exceed the specification. If either ΔVnoise or Imax-transient is a function of frequency, then Ztarget is a function of frequency. In principle, the combination of the entire spectral distribution of currents and the entire impedance profile is what creates the worst-case peak voltage noise. Unfortunately, this can only be determined with a transient simulation including the details of the transient current waveform and the impedance profile of the entire PDN. In practice, the target impedance is a useful approximation as a figure of merit to help focus the design of the PDN on a good starting place. 9 “WORKING” OR “ROBUST” PDN DESIGN Top: The impedance profile of the PDN ecology engineered to be below the target impedance from DC up to a very high bandwidth. Bottom: The resulting Vdd rail noise under large transient current load showing the noise is always below the 5% spec limit. The square wave trace is the transient current as driven by a clock. It is plotted on a relative scale. 10 Balance the trade-offs between the cost of implementing the PDN impedance compared to the target impedance, and the risk of a field failure. Generally, achieving a lower impedance PDN, and consequently a lower risk ratio, costs more either due to more components required, tighter assembly design rules impacting yield, more layers in the board or package, increased area for die capacitance, or the use of more expensive materials. SCULPTING THE PDN IMPEDANCE PROFILE The goal in PDN design is to engineer an acceptable impedance profile from DC to the highest frequency component of any power rail currents. 12 Top: Simplified schematic of the PDN ecology showing the major elements. This includes the on-die capacitance, the possibility of on-package capacitors, the package lead inductance, the circuit board vias, the power and ground planes in the circuit board, decoupling capacitor, bulk capacitors, and VRM.Bottom: Resulting impedance profile identifying how specific design features contribute to specific impedance features. On the horizontal scale “x” is MHz. SCULPTING THE PDN IMPEDANCE PROFILE In the journey ahead, we explore each of these elements that make up the PDN and how they interact to result in a robust and cost-effective PDN design. Ultimately, the power integrity engineer is responsible for finding an acceptable balance between cost, risk, performance, and schedule. The more we know about the details of the specific PDN elements, the more quickly we can reach an acceptable solution. 13 Essential Principles of Impedance for PDN Design 15 CALCULATING OR SIMULATING IMPEDANCE The sine wave output voltage of the AC constant current source is always related to the sine wave current through it by The figure illustrates the circuit for a simple impedance analyzer and the resulting impedance plots for a few ideal elements. Many simulators require a DC path to ground to each node. This resistor provides a DC path to the output of the constant current source even when the output is open or has a capacitive load. It limits the highest impedance we can simulate to 1 GΩ, perfectly adequate for all PDN applications. 17 REAL CIRCUIT COMPONENTS VS. IDEAL CIRCUIT ELEMENTS Do not confuse real circuit elements, which are the only thing that can be measured, with ideal circuit elements, which are the only thing that can be simulated. The impedance of many complicated, real structures can be described by simple combinations of ideal RLC circuit elements. Measured impedance of a real MLCC (multilayer ceramic chip) capacitor and the simulated 18 impedance of an ideal 182 nF capacitor. Comparing the measured impedance of a 0603 MLCC capacitor and an ideal series RLC circuit. Most structures associated with the PDN can be described by two simple RLC circuits and their combinations: a series combination of R, L, and C elements, and a parallel combination of R, L, and C elements. THE SERIES RLC CIRCUIT 19 Simulated impedance profile of the series RLC circuit. The circuit element values are R = 0.01 Ω, L = 1 nH, and C = 1 nF. THE SERIES RLC CIRCUIT Impedance profile of the RLC circuit as the capacitance is changed from 1 nF to 100 nF in four steps. Only the impedance at low frequency is affected. L = 1 nH. Impedance profile of RLC circuit as the value of L is changed from 1 nH to 100 nH in three steps. As the L changes, only the impedance on the high-frequency side is affected. C=1 uF. In a series RLC circuit, the low-frequency impedance is determined only by the capacitor whereas the high-frequency impedance is determined only by the inductor. 20 THE SERIES RLC CIRCUIT At the frequency where the inductive and capacitive reactances cross, their series combination of impedance goes to zero and the impedance of the series RLC circuit is dominated by the impedance of the ideal resistor element. We can calculate the angular frequency at which the magnitude of the capacitive and inductance reactances cross and are equal from The frequency at which the minimum impedance occurs is called the self or series resonance frequency (SRF), which we derive with At this resonant frequency, we get the capacitive and inductive reactances alone with 21 This impedance is often referred to as the characteristic impedance of the RLC circuit. THE PARALLEL RLC CIRCUIT parallel resonant frequency (PRF) At low frequency, the impedance is dominated by the parallel inductor. At high frequency, the impedance is dominated by the impedance of the capacitor, which decreases at higher frequency. The peak impedance occurs when the parallel impedance of the L and C is a maximum and the circuit’s impedance is limited by the impedance of the resistor element. Peaks in an impedance profile are almost always created by parallel RLC circuits. 22 Parallel RLC circuit and the impedance behavior with R = 1k Ω, L = 10 nH, and C = 1 nF. THE RESONANT PROPERTIES OF A SERIES AND PARALLEL RLC CIRCUIT In a series or parallel RLC circuit, three features describe the impedance properties: • The resonant frequency • The min or max impedance at the resonance • The broadness of the dip or peak (L = the inductance in nH C = the capacitance in nF) 23 Impedance profile of a series RLC circuit with three different values of Rseries with L = 10 nH and C = 10 nF. THE RESONANT PROPERTIES OF A SERIES AND PARALLEL RLC CIRCUIT In an RLC series circuit, the q-factor is For example, with L = 10 nH and C = 10 nF, Rseries = 1 Ω, the q-factor is 1. We can also see that the minimum impedance of the dip in a series RLC circuit, the resistance Rseries, is related to the q-factor by 24 THE RESONANT PROPERTIES OF A SERIES AND PARALLEL RLC CIRCUIT The value of the impedance peak at the parallel resonance is roughly related to the q-factor of the circuit and the characteristic impedance of the circuit, calculated with Two of the important figures of merit for a series or parallel RLC circuit are the characteristic impedance and q-factor. The peak impedance in a parallel circuit is related to Z0 × q-factor and the minimum impedance in a series circuit is related to Z0/q-factor. 25 Impedance profile of parallel RLC circuit with L = 10 nH, C = 10 nF, and three different q-factor values. THE RESONANT PROPERTIES OF A SERIES AND PARALLEL RLC CIRCUIT Example 1: A large tantalum capacitor. This is modeled as a series RLC circuit with typical values of C = 1000 μF = 106 nF L = 8 nH R = 0.05 Ω In this example we see that the very large tantalum capacitor has a low q-factor and we expect a flat impedance profile. 26 THE RESONANT PROPERTIES OF A SERIES AND PARALLEL RLC CIRCUIT Example 2: A typical large MLCC (multilayer ceramic chip) capacitor in a 1206 body using X5R dielectric material C = 10 μF = 10,000 nF L = 3 nH Rseries = 0.003 Ω 27 For this large value MLCC capacitor the q-factor is relatively large so we expect a sharp resonance. This is due to the very low series R. THE RESONANT PROPERTIES OF A SERIES AND PARALLEL RLC CIRCUIT A small value MLCC capacitor, 0402 body, X7R dielectric type C = 1 nF L = 1 nH Rseries = 0.16 Ω مقایسهشودqبااسالیدقبلیمقادیرمقاومتو For the small value capacitor the resistance element is about 50 times larger than the large capacitor’s due primarily to fewer conductor plates in parallel. However, the higher characteristic impedance results in a q-factor value that is still comparable. 28 THE PDN AS VIEWED BY THE CHIP OR BY THE BOARD A typical PDN circuit appears differently depending on the perspective from where we look The same circuit describing the on-die capacitance and package lead inductance viewed from two different perspectives. From the board, the impedance will have a dip. From the die, the impedance will have a peak. The on-die metallization of the PDN rails is a resistance in series with the on-die capacitance. The lead resistance of the package leads and the vias to the circuit board is a resistance in series with the package lead inductance. 30 THE PDN AS VIEWED BY THE CHIP OR BY THE BOARD For a small die, typical values might be Cdie = 50 nF Lpackage = 0.5 nH Rleads = 0.01 Ω Rmetalization = 0.005 Ω Requivalent = 0.015 Ω We expect these figures of merit to be: 31 Circuit topology for the PDN, viewed from two different sides, appearing as a parallel or series circuit. The impedance profiles of these two circuits are very different, even though they are composed of the same elements. TRANSIENT RESPONSE When a frequency component of the current flows through the impedance, the voltage generated at that frequency is related to the current amplitude and the impedance Note that when we do a frequency domain analysis we are evaluating only the steadystate time-invariant response. We are effectively assuming each frequency component of the current has been on forever and the voltage response is the steady-state response. This is often the desired response; however, there are a few cases, where the transient response reveals new behavior not apparent in the frequency domain. The frequency domain response is a good first-order estimate and can assist in quick estimates of the voltage response of the PDN. However, it is not the complete response, especially when the current source has complicated behavior. This is why analyzing a transient response is also important. 32 TRANSIENT RESPONSE the impedance profile of a voltage regulator module (VRM). Two real decoupling capacitors Impedance profile for the circuit in the earlier example, with the VRM model added. Note the parallel resonance at about 25 MHz. 33 TRANSIENT RESPONSE a current waveform rise time of 10 nsec gives a bandwidth of For a 10 nsec rise time current step we expect to see frequency components up to 35 MHz but not much beyond. If this current step were to pass through the circuit of Figure (in the pervious slide) with its PRF at 25 MHz, we expect to see ringing at 25 MHz from the high impedance. If we increase the rise time of the current step to 30 nsec, the bandwidth decreases to about 10 MHz. The amplitude of the current component at 25 MHz is less and the voltage noise we expect to see is reduced. The amplitude of the ringing depends on the relative energy in the current step at the ringing frequency. The longer the rise time, the less energy at 25 MHz and the lower the amplitude of the noise. 34 THE IMPEDANCE MATRIX The principles of impedance, while initially defined for a two-terminal device, can be extended to many more terminals. The matrix formalism is important to minimize the complexity as the number of terminals increases. For all passive interconnect circuits: 35 The circuit elements inside the box do not change. No new connections are being created and the circuit is fixed. The impedance of any element is completely independent of the voltage or current associated with any terminal. This is the case for all interconnect structures except some ferrites. THE IMPEDANCE MATRIX In the impedance matrix, the diagonal elements (called the self-impedance) relate to the impedance seen at each port. The off-diagonal elements (called the transfer impedance) relate to the coupling between each port. A small value of transfer impedance means very little coupling. 36 THE IMPEDANCE MATRIX For example, we can easily simulate the impedance matrix elements for two RLC circuits with a common lead inductance using the circuits shown in Figure The self-impedances are each due to the RLC circuit, with the common lead inductance in series in each circuit. The transfer impedance, from either side, is the impedance associated with the common lead inductance. In this example, the two RLC circuits have the same value of L and R, being 5 nH and 0.005 Ω, respectively. The C of the capacitor attached to port 1 is 1000 nF and 100 nF for the capacitor on port 2. The common lead inductance is 5 nH. 37 Measuring Low Impedance The design of a robust power distribution network is really about designing to a target impedance profile across a wide frequency range, from DC to the bandwidth of the highest frequency signals. Among different applications, this target impedance may range from higher than 1 Ω to a value in some applications to lower than 1 mΩ. The challenge is to measure the impedance of structures as low as 1 mΩ and low impedances up to frequencies exceeding 1 GHz. One fundamental definition of impedance is based on the ratio of the voltage across and the current through a device under test (DUT). This approach has an upper frequency limit based on the highest practical frequency to directly measure the current through the DUT. At frequencies above 100 MHz measuring impedance based on another definition of impedance is often more cost effective. 38 Measuring Low Impedance: MEASURING IMPEDANCE BASED ON THE REFLECTION OF SIGNALS A reflected signal is created whenever a signal encounters a change in the instantaneous impedance. This relationship represents a reflection method of defining impedance that is different from, but equivalent to, the ratio of voltage and current. 39 Inductance and PDN Design 43 Practical Multi-Layer Ceramic Chip Capacitor Integration 56 EQUIVALENT CIRCUIT MODELS Simulated impedance profile of ten identical series RLC circuits with one RLC circuit, two RLC circuits, and ten identical RLC circuits in parallel. The scaled values of the equivalent RLC model that has the equivalent behavior as the single RLC circuit are Measured impedance of a real 0603 Multi-Layer Ceramic Chip (MLCC) capacitor (thick line), mounted to a test board, compared to the simulated impedance of an ideal series RLC circuit model 57 Note also that the SRF & q factor of multiple, identical capacitors in parallel does not change. EQUIVALENT CIRCUIT MODELS THE PARALLEL RESONANCE FREQUENCY BETWEEN TWO DIFFERENT CAPACITORS Combining two series RLC circuits in parallel causes a new behavior to emerge and creates a peak impedance. This is due to the resonance of the two series RLC circuits excited in parallel and is referred to as a parallel resonance. Parallel resonant peaks are the most important feature of any PDN. 58 Note the SRF of the circuit with the larger capacitance is at a lower frequency than the SRF of the circuit with the smaller capacitance. EQUIVALENT CIRCUIT MODELS THE PARALLEL RESONANCE FREQUENCY BETWEEN TWO DIFFERENT CAPACITORS The peak impedance occurs at the parallel resonant frequency (PRF), where the reactances of the impedances of these two RLC circuits are equal and cross. This condition is 59 THE PEAK IMPEDANCE AT THE PRF The peak value of the impedance at the PRF is difficult to accurately calculate analytically but we can simulate it. When the two capacitors have a large difference in values, but their ESL (equivalent series inductance) values are the same, the peak impedance varies, related to the following three groups of terms: 60 The most important goal in robust PDN design is to reduce the peak impedances below the target impedance. We do this by leveraging the three design knobs when using multiple capacitors in parallel: closer distribution of capacitor values, lower mounting ESL, and larger capacitor ESR. EQUIVALENT CIRCUIT MODELS Our simple model suggests that when the ESL is the same for the two capacitors, the peak impedance is also related to the sum of the series equivalent resistances. We obtain a lower peak impedance with a higher value of the ESR of either series RLC circuit. Peak impedance as either R1 or R2 is changed, keeping all other circuit elements constant. We achieve lower peak impedance if we increase the ESR of either or both 64 capacitors. This is a strong driving force for using controlled ESR capacitors, which have higher ESR than normally found. EQUIVALENT CIRCUIT MODELS When we use two different capacitor values, with two different SRFs, the three most important ways to reduce the peak impedance are by • Bringing the capacitors’ values closer together • Increasing the ESR of each RLC circuit • Decreasing the ESL of both capacitors These are the most important driving forces in optimizing the capacitor values and integrating them into the PDN ecology. 66 ENGINEERING THE CAPACITANCE OF A CAPACITOR Fundamentally, a capacitor is nothing more than two conductors with a dielectric between them. A multilayer ceramic chip (MLCC) capacitor is actually multiple layers of conductors separated by dielectric in parallel. n = the number of dielectric layers between the parallel plates We achieve the high capacitance density in MLCC capacitors by using high Dk materials and thin spacing between the plates relative to printed circuit board parameters. This means there can be very high electric fields in the materials. Some of the high Dk materials are ferroelectric and show non-linear polarizability. Generally, higher fields reduce the DK value. 67 The Dk is also temperature sensitive. CAPACITOR TEMPERATURE AND VOLTAGE STABILITY Capacitors fall into three classes based on the sensitivity of their capacitance to voltage and temperature. • Class 1 capacitors are the most stable. They are generally composed of magnesium niobates and have Dk values ranging from 20 to 40. The Dk and resulting capacitance is stable over temperature and over voltage. One common material designation is NP0, referring to a temperature coefficient of capacitance that is less than 30 ppm/degK. Because the Dk is not very high, getting large value capacitance in class 1 capacitors is difficult. They are most suited for filter applications where the SRF needs to be quite stable. • Class 2 capacitors are most often selected for decoupling applications. Made with dielectric materials they have a Dk typically from 200 to 14,000. The materials are usually barium titanate with various additives. This enables a large capacitance in a small volume, but because of their ferroelectric properties, they have a larger sensitivity to temperature and voltage. 68 • Class 3 capacitors are made with materials that have a very high effective Dk value, but are not suitable for multilayer capacitors. Decoupling applications do not use this class of capacitor. CAPACITOR TEMPERATURE AND VOLTAGE STABILITY EIA (Electronics Industries Alliance) labeling format for class 2 capacitor materials based on the capacitance stability over temperature. X5R means a stable capacitance over the temperature range from –55 °C to +85 °C with a ±15% change over this range. The X7R material extends the temperature range to +125 °C. Both X5R and X7R materials are commonly used MLCC capacitor materials. 69 CAPACITOR TEMPERATURE AND VOLTAGE STABILITY Example of the temperature stability of various materials used in MLCCs. Example of voltage sensitivity of some material examples. 70