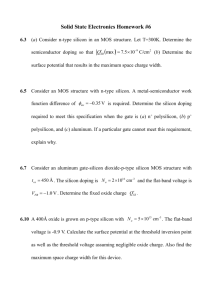

Device Physics – Basics and Process Overview Nguyen Minh Hieu Hanoi University of Science, VNU 1. Semiconductor materials - basics 2. Semiconductor device physics 3. MOSFET and CMOS process flows 1 1. Semiconductor materials - basics 1.1 Silicon 1.2 Finite Temperatures - intrinsic material 1.3 Doping of Silicon - Extrinsic Material 1.4 Doped Silicon Resistivity (300 K) 1.5 Band Diagrams 1.6 Band Diagram – Doping 1.7 Carrier Concentration – Temperature 1.8 Fermi Distribution Function 1.9 Mass Action Law 1.10 Important Formulas 1.11 Recombination - Generation 2 1.1. Silicon dopants (1s2)(2s2)(2p6)(3s2)(3p2) covalent bond Valence: 4 Si has four electrons in its outermost shell (valance electrons) GaAs : Ga(column III) As (Column V) => Semiconductors 3 1.2. Finite Temperatures - intrinsic material * T > absolute zero => thermal energy can break some of Si-Si bonds. * n = p = ni ni exp(Ea/kT) Si 300 K ni = 1.4 1010 cm-3 * At room temp. ni~1.4x1010 * Fewer than 1 in 1012 bonds are broken at Troom * Pure silicon is a very poor conductor 4 1.3. Doping of Silicon - Extrinsic Material Donor electron rich negative charge Acceptor hole rich positive charge Conductivity of Si is very poor at room temperature Positively, Si can be doped (n-type or p-type) Column V elements is N-type dopants(donor) => n-type semiconductor Column III elements is P-type dopants(acceptor)=>p-type semiconductor Modern technique is ion implantation => easily to control doping profile 5 Doped Silicon Resistivity (300 K) 1 qn n qp p N- -or P- -: ND or NA < 1014 cm-3 N- or P-: 1014 cm-3 < ND or NA <1016 cm-3 N or P : 1016 cm-3 < ND or NA <1018 cm-3 N+ or P+: 1018 cm-3 < ND or NA <1020 cm-3 N++ or P++: ND or NA > 1020 cm-3 Normally doping concentration < 1% Lattice density in Si: 5 x 1022 cm-3 6 Band Diagram Free electron Conduction band gap Bonding electron Valence band •Valid for perfect crystals •EV, EC, and EG •This model is the same with the bond model 7 Band Diagram - Doping As B As+ + n B- + p As: (1s2)(2s2)(2p6)(3s2)(3p3) ni2=n*p 8 Carrier Concentration - Temperature T<100K freezeout of As donor 100K<T<600K As dopant is dominated. T>600K intrinsic carriers are dominated ND = 1015 cm-3 9 Fermi Distribution Function Intrinsic n-type p-type 1 F (E) E EF 1 exp kT 10 Mass Action Law n EC EF F ( E ) N ( E ) dE N exp C E kT C E EF p (1 F ( E )) N ( E )dE NV exp V kT EV E n p ni2 N C NV exp g kT 11 Important Formulas n p n 2 i Ei EF p ni exp kT Mass action Boltzmann statistics EF Ei n ni exp kT Bán dẫn pha tạp N D p N A n Charge neutrality 1 n [( N D N A ) ( N D N A ) 2 4ni2 ] 2 1 p [( N A N D ) ( N A N D ) 2 4ni2 ] 2 12 Recombination - Generation Minority carrier lifetime: 1 R vth NT NT is the density of traps per cm3. Νth is thermal velocity σ is the capture cross section of the trap Traps with energy level near Ei are most important (Fe, Ni, Au, Pt) 13 2. Semiconductor devices physics 2.1. PN Diode 2.2. Bipolar transistor 2.3. MOSFET 14 2.1. P/N Diode 2.1.1. Introduction to junction diode 2.1.2. Junction in equilibrium 2.1.3. Energy diagram 2.1.4. Forward and reverse biased junctions 2.1.5. V-A Characteristic 2.1.6. Junction breakdown 15 2.1.1. Introduction to junction diode pn junction diode Cathode Anode Heavily doped p region Heavily doped n region Metal contact p- Substrate - p/n junction is the most common one in microelectronics. - Junction can be made of dissimilar semiconductor materials. This class of devices is called “Hetero Junctions”. 16 2.1.2. Junction in equilibrium p n bi • There are diffusion of carries (e from n-side to p-side; h from p-side to n-side). • Doped atoms are ionized at the junction 1 kT N D N A bi ( E F (n) E F ( p)) ln q q ni2 17 2.1.3. Energy diagram in equilibrium p EC n EC EF EFi EF EV Efi E E EV EC EFi EF EV qVbi - Two sides are not connected E F Ei EC EV kT N ln( V ) 2 2 NC ND ) NC NA EF EV kT ln( ) NV EF ED kT ln( - The bands are bended at the junction 18 2.1.4. Forward and reverse biased junctions V Vbi Forward biasing EC EFi EF EV Vbi p EF n EC EFi EF EV V Vbi EC Reverse biasing EFi EF EV EF 19 2.1.4. V-A Characteristic (1) qV A n p ( x dp ) n p 0 exp( ) KT qV pn ( xdn ) pn 0 exp( A ) KT np is electrons at the p-side pn is holes at the n-side For the electron diffusion current at x=xdp qVa x d J n qDn qDn n p 0 exp( ) n p 0 dx exp( ) dx KT Ln dn p J ( J p ) diff ( J P ) drift ( J n ) diff ( J n ) drift 1 Dn qVA 1 D p exp( I total A( J n J p ) Aqn ) 1 KT N A Ln N D LP qV I Io exp( A ) 1 KT 2 i 20 2.1.4. V-A Characteristic (2) qVA I Io exp( ) 1 KT +I Forward bias curve 120 100 80 60 40 Junction voltage 20 -V +V Breakdown voltage .4 Leakage current .8 1.2 1.6 Reverse bias curve -I 21 2.1.4. V-A Characteristic (3) Effect of temperature on the V- I o 10 T=22 C o T=55 C o T=110 C o T=153 C o T=200 C o T=253 C IF[mA] 1 0.1 0.01 0.001 0 200 400 600 800 VF[mV] Diode as temp. sensor 22 1000 2.1.5 Junction breakdown (1) I Avalanche Breakdown •At critical value of electric field , the carries accelerate to large enough energy. VBR V •The carrier collide with atom the crystal lattice, they free an electron-hold pair. 23 2.1.5 Junction breakdown (2) Zener Breakdown (or Tunneling Breakdown) -Zener breakdown occurs in p-n junction that are heavily doped both side - The barrier thickness is lower than 10nm Tunneling Homogenous doping W x dn x dp 2 s 1 1 ( )bi q NA ND 24 2.2. Bipolar transistor 2.2.1. Introduction to bipolar transistor 2.2.2. Energy diagram and basic operation 2.2.3 Static characteristics of bipolar transistors 25 2.2.1. Introduction to bipolar transistor (1) 1947 Bardeen and Brattain (Transistor) The transistor was built on germanium. Transistor “analog” switch 26 2.2.1. Introduction to bipolar transistor (2) • NPN BJT shown • 3 terminals: emitter, base, and collector • 2 junctions: emitter-base junction (EBJ) and collector-base junction (CBJ) – These junctions have capacitance (high-frequency model) • Depending on the biasing across each of the junctions, different modes of operation are obtained – cutoff, active, and saturation MODE EBJ CBJ Cutoff Reverse Reverse Active Forward Reverse Saturation Forward Forward 27 2.2.2. Energy diagram and basic operation (1) • In equilibrium – No current flow – Back-to-back PN diodes n+ Emitter p n Base Collector Ec Ef Ev N P N 28 2.2.2. Energy diagram and basic operation (2) IC IE n+ n p OUTPUT IB VE VB B Emitter C Base Collector Ec Ef Ev N P N Active Mode • EBJ forward biased – Barrier reduced and so electrons diffuse into the base – Electrons get swept across the base into the collector • CBJ reverse biased – Electrons roll down the hill (high E-field) 29 2.2.2. Energy diagram and basic operation (3) • Two external voltage sources set the bias conditions for active mode – EBJ is forward biased and CBJ is reverse biased • Operation – Forward bias of EBJ injects electrons from emitter into base (small number of holes injected from base into emitter) – Most electrons shoot through the base into the collector across the reverse bias junction (think about band diagram) 30 – Some electrons recombine with majority carrier in (P-type) base region 2.2.2. Energy diagram and basic operation (3) iE p n+ iEn n JEn JEp JCn iEp (JEn-JCn) iCp JBB iB Important parameters: iE=iEn+iEp iC=iCn+iCp iB=iE-iC=(iEn-iCn)+ (iEp-iCp) iC iCn JCp Hole flow and hole current Electron flow Electron current 0=iCn/iE =iEn/(iEn+iEp)=iEn/iE T=iCn/iEn 0= T iC=iCn+iCp=0iE+iCp 0 is common base current gain; γ is emitter efficiency ; T is transport factor 31 2.2.3 Static characteristics of bipolar transistors (1) B E p C n W n 1 DE N B W 1 . . DE N E LE 2 W T 1 2 2 LL 0= T -To improve γ, NB/NE should be decreased (much heavy doping in the emitter). - To impove T , W (depth of base) should be reduced 32 2.2.3 Static characteristics of bipolar transistors (2) Regimes of operation: BJT = two neighbouring pn junctions back-to-back: • close enough for minority carriers to interact (can diffuse quickly through base) • far apart enough for depletion regions not to interact (prevent ”punchthrough”) 33 2.2.3 Static characteristics of bipolar transistors (2) I-V Characteristics IC IB + n p IC + VBE VCE n IE IB ACTIVE • Collector current vs. VCB shows the BJT looks like a current source (ideally) – Plot only shows values where BCJ is reverse biased and so BJT in active region 34 2.4. MOSFET 2.4.1. Introduction to MOS device 2.4.2. The ideal MOS diode 2.4.3. The SiO2-Si MOS diode 2.4.4. The MOSFET: Basic characteristics 2.4.5. Types of MOSFET 2.4.6. Short channel effect and process scaling 2.4.7. Complementary MOS (CMO) technology 2.4.8. Silicon on Insulator (SOI) Technology 2.4.9. Process steps in IC manufacturing 2.4.10. Microfabricated process – MOSFET 2.4.11. Modern CMOS process flow 35 2.4.1. Introduction to MOS device MOS structure Typical MOS capacitors and transistors in ICs today employ – heavily doped polycrystalline Si (“poly-Si”) film as the gate electrode material • n+-type, for “n-channel” transistors (NMOS) • p+-type, for “p-channel” transistors (PMOS) – SiO2 as the gate dielectric • band gap = 9 eV • εr,SiO2 = 3.9 – Si as the semiconductor material • p-type, for “n-channel” transistors (NMOS) • n-type, for “p-channel” transistors (PMOS) 36 2.4.2. The ideal MOS diode (1) V=0 (1) qms V ≠0 Eg qm qs qm q qb 0 2 (2) Charges on the metal surface are equal but opposite sign in semiconductor. 37 (3) There is no carrier transport through oxide under biasing. 2.4.2. The ideal MOS diode (2) The Surface Depletion Region n p ni e q ( B ) kT p p ni e q ( B ) kT SURFACE SEMICONDUCTOR qψm qψS Ψs>0 qψB qψ EC Note: ψ =0 in bulk semiconductor ψ = ψs at the surface Ei E Ψ>0 when the band is bent downward F SEMICONDUCTOR EV OXIDE x ns ni e q ( B ) kT ps ni e q ( B ) kT Ψs<0 Accumulation of holes (bands bent upward) Ψs=0 Flat-band condition ψB> ψs>0 Depletion of holes (bands bent downward) Ψs= ψB Midgap with ns=np=ni (intrinsic concentration Ψs> ψB Inversion (bands bent downwards) 38 2.4.2. The ideal MOS diode (2) Ideal MOS – Capacitor Co Cj (ns=NA) C0C j V=V0 + Ψs Qs d Qs V0 E0 d ox C0 V0 is potential across the oxide C C C0 C j C0 Cj=εs/W 1 2 02xV 1 qN A s d 2 39 2.4.2. The ideal MOS diode (3) The Threshold Voltage ns N A ni e s 2 B qN AW 2 2kT N A s 2 b ln 2 s q ni q B / kT The strong inversion takes place 2 s qN A (2 B ) qN AWm VG VT s (inv) 2 B C0 C0 Cmin ox d ( ox / s )Wm C0 C0 Cj Cj VT 0 Cmin V 40 2.4.3. The SiO2-Si MOS diode The work function difference: Interface traps & oxide charge -Work function different, qфms is not zero. -There are various charges in Si-SiO2 interface. -q фms=q фm- qфs => depending on the doping of semiconductor -The equilibrium is affected by charges in the oxide and traps in the interface. -Qot is oxide trapped charge -Qf is fixed oxide charges -Qit is interface trapped charges -Qm is is mobile ionic charges VACUUM LEVEL qфm qфs EF qфs EC VFB qфm EF METAL Oxide Trapped Charge p-Si SiO2 VFB= фm- фs VFB is called flat-band voltage EC Mobile Ionic Na+ Charge K+ EF Interface Trapped Charge Fixed Oxide Charge VFB= фms- (Qf+Qm+Qot)/C0 41 2.4.4. The MOSFET: Basic Characteristics (1) Structure Description - 3 terminal device (gate, source, drain) - Additional body (or bulk) terminal (generally at DC and not used for signals) - Two types: nMOS and pMOS Important parameters L is the channel length W is the channel width d is the oxide thickness 42 2.4.4. The MOSFET: Basic Characteristics (1) NMOSFET - Operation No gate voltage (VGS = 0) – Two back to back diodes both in reverse bias – no current flow between source and drain when voltage between source and drain is applied (VDS >0) – There is a depletion region between the p (substrate) and n+ source and drain regions Apply a voltage on VGS > 0 – Positive potential on gate node pushes free holes away from the region underneath the gate and leave behind a negatively charged carrier depletion region • transistor in depletion mode – As VGS increases, electrons start to gather at the surface underneath the gate (onset of inversion) – When VGS is high enough, a n-type channel is induced underneath the gate oxide where there are more electrons than holes (strong inversion) • This induced region is called an inversion layer (or channel) and forms when VGS > some threshold voltage Vt and current can flow between S & D • Transistor is in inversion mode • When VDS = 0, no current flows between source and drain 43 2.4.4. The MOSFET: Basic Characteristics (1) NMOSFET – Operation (next) Si t ox VT 2 B ox 4qN A o Si B VG>VT VG > VT VDS = VG -VT V V W off Cox GS T L 2 I DS 2 I DS W eff Cox VG VT VDS L VG > VT, VG – VT > VDS I DS 2 VDS W eff Cox VG VT Vds 44 L 2 2.4.5 Types of MOSFETs MOSFET Type Mode nMOS Enhancement Standby VGG Switching Condition Requirements Off Physical Structure Drain n+ n+ p-type silicon substrate Depletion On Off ID Drain n+ n+ p-type silicon substrate p-type silicon substrate Enhancement 0 VTn Gate - Source pMOS ID Gate + Source nMOS ID VTp0 Gate Source p+ VTn0 Drain p+ n-type silicon substrate pMOS Depletion On Gate + Source p+ Drain 0 VTp p+ n-type silicon substrate 45 2.4.6. Short channel effect and process scaling (1) Sitox VT VBF 2B ox B Ion Implantation 4qN A o Si B NA n+ n+ VT increases VT reduces -VT can be adjusted by channel ion implantation -Additionally, VT can be controlled by varying oxide thickness 46 2.4.6. Short channel effect and process scaling (2) Short-Channel Effects Lightly Doped Drain Structure (LDD) -As channel length is reduced, the depletion layers become comparable -The short channel effect can be reduced by LDD 47 2.4.6. Short channel effect and process scaling (2) Transistor Scaling Scaling rules Roadmap Metallisation 48 2.4.6. Short channel effect and process scaling (1) Device Scaling Scenarios Scale dimensions (L, W, tox, dj, .....) with factor (typical 0.7) Scale potentials with factor 49 Scaling Factors Physical Parameter Expression Scaling Factor Lin. Dimension W, L, tox, dj 1/ Potential Vds, Vdd, VT 1/ NA, ND E (W/L)Cox(Vgs-VT)Vds WCox(Vgs-VT)vdr 1/ ID.VD ID.VD/A 22 CL VDD / ID 1/ ID VD tD 1/2 L/A A Cox, ACj 1/ Current density Id/A RC constant RiCi 1 Impurity concentration Electric Field Current (linear) Current (sat. limited) Power Power Density Gate Delay Power-Delay product Line resistance Capacitance 50 Scaling Scenarios 1. Constant E-Field scaling CE (R. Dennard et al. IBM) L L V V issues: VT does not scale (subthreshold leakage) very good for power dissipation and reliability 2. Constant Voltage scaling CV (system people) L L V = constant (5 V, 3.3 V) Issues: Reliability and power dissipation 3. Quasi-Constant Voltage scaling (P. Chatterjee et al. TI) L L V V constant hot carrier reliability 51 Constant Field Scaling From 250 nm CMOS on constant field (CE) scaling has been used Main reasons: power dissipation, reliability Drawback: threshold voltage does not scale (stand-by current goes up) 52 43 nm Gate Length MOSFET Excellent device behaviour down to 43 nm gate length Toshiba (H. Iwai et al.) 53 ITRS Roadmap International Technology Roadmap for Semiconductors Provide guidelines for semiconductor industry, equipment makers system people, ..... (takes care that everything happens at the right time!) Target for semiconductor companies Has proven to be quite realistic October 1999 - third version IC Industry motto: to beat the roadmap 54 ITRS 1997 Roadmap 55 Technology Requirements - Gate Dielectric SIA_L Gate dielectric SIA_H CE Eq. Oxide Thickness (nm) 5.0 4.0 Thin gate oxide main contributor to high device performance tox < 1.5 nm ? High- SiO2 has too high direct tunnelling current (Ig > 1A/cm2) 3.0 2.0 SiO2 needs to be replaced by “high”- gate dielectric 1.0 (Si3N4, ZrO2, HfO2, Ta2O5) 0.0 0 0.05 0.1 0.15 0.2 0.25 0.3 Tech. gen. (um) Down to 1.6 nm no roadblocks, “leaky” oxide is accepted, below 1.5 nm new materials 56 Drain-Extension Depth SIA_L S/D extension SIA_H CE S/D extension depth (nm) 100.0 90.0 80.0 70.0 Elevated S/D ??? 60.0 50.0 40.0 30.0 20.0 10.0 0.0 0 0.05 0.1 0.15 0.2 0.25 0.3 Tech. gen. (um) Ion implantation: Especially difficult for PMOS - Dj below 40 nm Alternatives: diffusion, selective EPI for elevated S/D 57 Channel Doping 1,E+19 Vt=0.36 Channel Doping (cm-3) SIA Assumptions: VT = 0.36 V Uniform doping conc. No quantum effects No gate depletion 1,E+18 1,E+17 0 100 200 300 Tech. Generation (nm) Channel doping extremely high Quantum effects + VT fluctuation tunnel breakdown high diode leakage Super Steep Retro Profile and/or Pockets 58 Technology Requirements - Supply Voltage SIA_L Voltage Scaling SIA_H CE Supply Voltage (V) 2.5 2.0 Constant Field Scaling CE - (by Dennard IBM) L = L / Vdd = Vdd/ Supply voltage scaling dominated by powerdensity 1.5 1.0 0.5 0.0 0 0.05 0.1 0.15 0.2 0.25 0.3 Supply voltage below 1V for (sub) 100 nm technology Tech. gen. (um) Low Vdd limits circuit performance (esp. for mixed signal IC’s ) 59 Current Drive Capability NMOS Ion (A/um) Exp SIA Simul. 1.E-03 9.E-04 8.E-04 7.E-04 6.E-04 5.E-04 4.E-04 3.E-04 2.E-04 1.E-04 0.E+00 Simulation includes: Gate depletion Quantum effect on VT SSR profile S/D as in SIA Ioff according SIA Simulation artefacts: QM inversion layer thickness Series resistance too low 0 0.1 0.2 0.3 Tech. gen. (um) Down to 70 nm SIA spec is reasonable For 50 nm technology Vt has to be reduced dual Vt or Vt modulation 60 Gate delay Metric CV/I (NCH) Metric 25.0 Gate Delay Metric (ps) TI + INTEL IEDM 20.0 SIA Linear (TI + INTEL) 15.0 10.0 5.0 0.0 0 0.1 0.2 0.3 Tech. gen. (um) Trend in transistor performance metric observed down to 100 nm technology 61 Trends - Cutt-Off Frequency 62 Trends - Ringoscillator Delay 63 Interconnect 1. Interconnect capacitance does not scale down 2. Resistance of lines increases (width ) 3. Current density increases (reliability) Interconnect R,C dominates circuit performance 64 Interconnect Delay 65 Summary 1. Constant field scaling is the scenario used for 250 nm CMOS and beyond 2. Scaling goes down to 30 nm CMOS or even further. 3. Transistor performance increases strongly. 4. Gate dielectric (< 1.5 nm) and junction depth are considered to be the major roadblocks for further scaling 5. Interconnect parasitics will dominate circuit performance. 66 2.4.7. Complementary MOS (CMOS) technology 1. Driver: large digital circuits (microprocessor, memory) 2. Low power consumption (stand-by) 3. Low supply voltage (<1V) 4. Fast also used for analog (mixed signal) and RF (?) 67 2.4.8. Silicon on Insulator (SOI) Technology Transistors are fabricated in a thin single-crystal Si layer on top of an electrically insulating layer of SiO2 • Simpler device isolation savings in circuit layout area • Low junction capacitances faster circuit operation • Better soft-error immunity • No body effect • Higher cost 68 2.4.9. Process steps in IC manufacturing 69 IC manufacturing Process steps: • Oxidation • Photolithography • Diffusion • Implantation • Deposition • Etching • Cleaning • Polishing (CMP) Complete process: 300 - 500 process steps 20 - 50 lithography steps Repeated application of process steps 70 Basic process step: silicon oxidation Oxide • Clean silicon wafer • Grow silicon-oxide - 150 nm furnace, O2 ambient, 1000°C Temperature and time determine layer thickness Silicon 71 Basic process step: lithography UV-light • Spin-on photoresist • Expose locally with UV light • Develop photoresist mask photo-resist silicon oxide silicon substrate 72 Basic process step: ion implantation • Ion implantation • Very precise dosimetry • Energy determines depth Accelerated ion Question: why ions, not atoms? • A subsequent heat treatment is required to position the ions in the silicon lattice 73 Basic process step: deposition Si3N4 • Physical deposition (e.g. sputtering) • Chemical vapour deposition (CVD) (e.g. epitaxy) Silicon 74 Basic process step: etching mask SiO2 Silicon substrate • Immerse in HF bath (HF+H2O) • Etch SiO2 (do not etch silicon) • Dry wafer 75 Process complexity Complexity of Si-technology increases Silicon silicon nitride silicon oxide aluminum 1960s low k dielectrics copper metallization ferro-electric materials Chemical Mechanical Polishing Rapid Thermal Processing low-temperature epi selective deposition Multilevel metallization SiGe Thin (<3 nm) dielectrics new alloys (AlCu) Silicon on Insulator silicides ONO layers cleaning 1985-1995 Time 1995-2000 76 2.4.10. Microfabricated process – MOSFET 77 Preparation 78 Thermal Oxidation 79 80 81 82 83 84 2.4.11. Modern CMOS process flow Vin Vout Vss Vdd n-well p-substrate 85 Present CMOS 0.18 m CMOS is now produced by all major manufacturers. This process features: • 0.12-0.18 m gate length, 0.4-0.5 m pitch • 3-3.5 nm gate oxide (regular SiO2) • 5-6 levels of metal interconnect • About 107 transistors on a 1 cm2 chip • 1.2 GHz on-chip clock frequency 86 Terminology: front-end and back-end Back-end Contact Transistor Front-end STI p-well n-well Front-end-of-line includes substrate, isolation, wells, transistor, salicide Back-end includes contacts, metal lines, and the intermetal dielectrics 87 Shallow Trench Isolation (STI) formation Photolithography + oxidation + deposition + polishing Purpose: To create “isolated” silicon islands at the surface Sacrificial oxide on top of silicon: to avoid contamination 88 Shallow trench isolation (STI) Trench etch Oxidation Trench fill Stack removal (deposition & CMP) Photos: Philips Research Stack deposition 89 Retrograde N-well formation Photolithography + ion implantation n-well 90 Retrograde P-well formation p-well n-well 91 Gate oxide growth + poly deposition oxidation + deposition poly Gate oxide 92 Photos: G. Timp et al., IEDM 1999 TEM cross section thin oxide (TEM = transmission electron microscope) 93 Photo: Ronald Roes, Philips Research After polysilicon deposition 94 After gate etch - S/D formation Photolithography + ion implantation 95 PMOS S/D extension implant 96 Spacer formation Deposition + reactive ion etch thin oxide + nitride 97 NMOS - S/D implant Photolithography + ion implantation Simultaneous source, drain and gate doping, and well contact doping 98 PMOS - S/D implant 99 Photo: Philips Research After S/D implants 100 Shallow junction annealing Photo: Sematech • Furnace anneals: > 0.25 m typically 2+-hour runs, slow ramp up and down – too much TED – too much diffusion 0.13 - 0.25 m • Rapid thermal anneals • Spike RTA anneals < 0.13 m • Laser anneals 101 Salicidation Deposition + anneal + etch TiSi2 or CoSi2 (sub-0.18 m technologies) 102 TEM cross-section after salicidation TiSi2 Poly gate TiSi2 Photo: Intel Spacer 103 Contact formation Photolithography + reactive ion etch 104 Contact fill and metal-1 formation input input 105 Planarization Why do we need planarization? 1) depositions are easier (easier means better, cheaper, less defects) 2) Denser patterns are possible 3) Lithography has a limited depth of focus (typically: < 1 m) 106 Where is the transistor? Photo: UMC 0.25 m CMOS after Metal 6 107 MOS technology Further reading • The Technology roadmap for semiconductors: http://public.itrs.net • A dictionary of semiconductors: http://www.sematech.org/public/publications/dict/index.htm • Nice 3D view of transistor fabrication and operation: http://www.micro.magnet.fsu.edu/electromag/java/transistor/index.html http://entcweb.tamu.edu/zoghi/semiprog/INDEX1.HTM • Many interesting links at www.casetechnology.com/links.html 108