Lecture 8

Number representation:

Three systems are used for representing numbers:

Sign-and-magnitude ·

1' s-complement ·

2' s-complement

In all three systems, the leftmost bit is 0 for positive numbers

and 1 for negative numbers.

1. Positive values have identical representations in all systems

Ex: 5

Sign-and-magnitude

1' s-complement

2' s-complement

0101

0101

0101

2. Negative values have different representations.

In

the sign-and-magnitude system, change the most

significant bit from 0 to 1 of the corresponding positive

value.

In 1 's-complement representation, complement each bit of

the corresponding positive number but keep the sign bit

unchanged.

in the 2 's-complement system, subtract that number from

2^n or by adding 1 to the 1 's-complement of that number.

Ex: -5

Sign-and-magnitude

1' s-complement

2' s-complement

1101

1010

1011

Note:

There are distinct representations for +0 and -0 in both the

sign-and- magnitude and 1 's-complement systems, but the 2'scomplement system has only one representation for 0.

For 4-bit numbers, the value -8 is representable in the 2 's-

complement system but not in the other systems.

Question:

Represent the decimal values 5, -2, 14, -10, 26, -19, 51, and

-43, as signed, 7-bit numbers in the following binary

formats:

(a) Sign-and-magnitude

(b)1 's-complement

(c) 2's-complement

Machine Instruction Characteristics

The operation of the processor is determined by the instructions

it executes, referred to as machine instructions or computer

instructions

The collection of different instructions that the processor can

execute is referred to as the processor’s instruction set

Each instruction must contain the information required by the

processor for execution

Elements of an Instruction

Operation code (Op code) Do this

Specifies the operation to be performed (e.g., ADD, I/O). The operation is

specified by a binary code, known as the operation code, or opcode.

Source Operand reference: To this

The operation may involve one or more source operands, that is, operands

that are inputs for the operation.

Result Operand reference: Put the answer here

The operation may produce a result.

Next Instruction Reference

When you have done that, do this...[i.e. the next instruction to fetch, often

is the immediately follow the current instruction, only explicit reference is

needed when need to jump else where].

Operand

fetch

Instruction

fetch

Operand

store

Multiple

operands

Instruction

address

calculation

Instruction

operation

decoding

Operand

address

calculation

Instruction complete,

fetch next instruction

Multiple

results

Data

Operation

Operand

address

calculation

Return for string

or vector data

Figure 12.1 Instruction Cycle State Diagram

Where have all the Operands Gone?

Main memory (or virtual memory or cache)

CPU registers

I/O device (in case of memory mapped I/O the reading the

operands are fetched by the same way as the fetching the

operands from memory.

Types of Operands

Addresses

Numbers

Integer/floating point

Characters

ASCII etc.

Logical Data

Bits or flags

Pentium Data Types

8 bit Byte

16 bit word

32 bit double word

64 bit quad word

Addressing is by 8 bit unit

A 32 bit double word is read at addresses divisible by 4

Numbers

All machine languages include numeric data types

Numbers stored in a computer are limited:

Limit to the magnitude of numbers representable on a machine

In the case of floating-point numbers, a limit to their precision

Packed decimal

Each decimal digit is represented by a 4-bit code with two digits stored

per byte

To form numbers 4-bit codes are strung together, usually in multiples of 8

bits

the code for 246 is 0000 0010 0100 0110

Characters

A common form of data is text or character strings. Textual data in

character form cannot be easily stored or transmitted by data processing

and communications systems because they are designed for binary data

Most commonly used character code is the International Reference

Alphabet (IRA). the IRA bit pattern 011XXXX, the digits 0 through 9 are

represented by their binary equivalents, 0000 through 1001, in the

rightmost 4 bits.

Referred to in the United States as the American Standard Code for

Information Interchange (ASCII)

Another code used to encode characters is the Extended Binary Coded

Decimal Interchange Code (EBCDIC). In the case of EBCDIC, the codes

11110000 through 11111001 represent the digits 0 through 9.

EBCDIC is used on IBM mainframes

Logical Data

Normally, each word or other addressable unit (byte, halfword,

and so on) is treated as a single unit of data.

It is sometimes useful, however, to consider an n-bit unit as

consisting of n 1-bit items of data, each item having the value 0

or 1.

When data are viewed this way, they are considered to be

logical data.

Byte unsigned integer

7

0

Word unsigned integer

15

0

Doubleword unsigned integer

31

0

Quadword unsigned integer

63

0

sign bit

twos comp

7

0

sign bit

15

0

sign bit

31

0

sign bit

63

0

sign bit

signif.

exp

15

9

0

sign bit

exp

31

significand

22

0

sign bit

exp

63

sign bit

51

0

Word signed integer

(twos complement)

Doubleword signed integer

(twos complement)

Quadward usigned integer

(twos complement)t

Half precision

floating point

Single precision

floating point

Double precision

floating point

integer bit

exponent

79

significand

Byte signed integer

(twos complement)

significand

63

0

Double extended precision

floating point

Figure 12.4 x86 Numeric Data Formats

Instruction Types

Data processing (arithmetic and logic instructions)

Data storage (main memory): to transfer data to/from

memory (store or fetch data and instructions)

Data movement (I/O) to transfer program and data to

memory

Program flow control : to execute the decision and

looping instruction.

Number of Addresses (a)

3 addresses

Consists of two operands (Operand 1, Operand 2) in additional to

the address of the Result

Ex. The next instruction can be represented by single add

instruction with three operands (a = b + c;)

May be a forth (2 data operands, result operand and the next

instruction operands)–next instruction address is being implicit.

Forth instruction format not common as well as 3-instructions

format

The reason is the need for very long words to hold everything

Number of Addresses (a)

Y= (A-B)/[C+(D*E)]

The 3-address instruction is used in the following program

to execute the above high level instruction

Sub Y, A,B

MPY T, D,E

ADD T,T, C

DIV Y, Y, T

Number of Addresses (b)

2 addresses

One address doubles as operand and result

a = a + b (one of the operands is used as data and result)

Reduces length of instruction

Requires some extra work

Temporary storage to hold some results

MOVE Y, A

SUB Y, B

MOVE T,D

MPY T,E

ADD T, C

DIV Y, T

Number of Addresses (c)

1 address

Implicit second address

Usually a register (accumulator)

Common on early machines

MOVE D

MPY E

ADD C

STORE Y

MOVE A

SUB B

DIV Y

STORE Y

Number of Addresses (d)

0 (zero) addresses

All addresses implicit

Uses a stack

e.g. push a

push b

add

pop c

c=a+b

How Many Addresses

More addresses

More complex (powerful?) instructions

More registers

Inter-register operations are quicker

Fewer instructions per program

Fewer addresses

Less complex (powerful?) instructions

More instructions per program

Faster fetch/execution of instructions

Design Decisions

Registers

Number of CPU registers available

Which operations can be performed on which registers?

Addressing modes (later…)

RISC v CISC

RISC

CISC

Reduced Instruction Set

Architecture (RISC) RISC

processors only use simple

instructions that can be

executed within one clock

cycle.,

Complex Instruction Set

Computers(CISC) The

primary goal of CISC

architecture is to complete a

task in as few lines of

assembly as possible.

LOAD A, 3

LOAD B, 5

PROD A, B

STORE 3, A

MULT 3, 5

Types of Operation

Data Transfer

Arithmetic: add, subtract, multiply, and divide

Logical

Conversion

I/O

System Control

Transfer of Control: Branch, Skip, Procedure call

Type

Data Transfer

Arithmetic

Logical

Operation Name

Description

Move (transfer)

Transfer word or block from source to destination

Store

Transfer word from processor to memory

Load (fetch)

Transfer word from memory to processor

Exchange

Swap contents of source and destination

Clear (reset)

Transfer word of 0s to destination

Set

Transfer word of 1s to destination

Push

Transfer word from source to top of stack

Pop

Transfer word from top of stack to destination

Add

Compute sum of two operands

Subtract

Compute difference of two operands

Multiply

Compute product of two operands

Divide

Compute quotient of two operands

Absolute

Replace operand by its absolute value

Negate

Change sign of operand

Increment

Add 1 to operand

Decrement

Subtract 1 from operand

AND

Perform logical AND

OR

Perform logical OR

NOT (complement)

Perform logical NOT

Exclusive-OR

Perform logical XOR

Test

Test specified condition; set flag(s) based on outcome

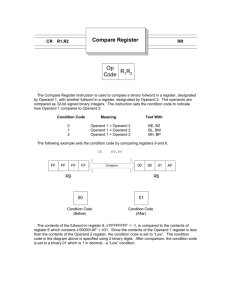

Compare

Make logical or arithmetic comparison of two or more

operands; set flag(s) based on outcome

Set Control

Variables

Class of instructions to set controls for protection

purposes, interrupt handling, timer control, etc.

Shift

Left (right) shift operand, introducing constants at end

Rotate

Left (right) shift operand, with wraparound end

© 2016 Pearson Education, Inc., Hoboken, NJ. All rights reserved.

Table 12.3

Common

Instruction Set

Operations

(page 1 of 2)

(Table can be found on page

426 in textbook.)

Type

Operation Name

Jump (branch)

Unconditional transfer; load PC with specified address

Jump Conditional

Test specified condition; either load PC with specified

address or do nothing, based on condition

Jump to Subroutine

Place current program control information in known

location; jump to specified address

Return

Replace contents of PC and other register from known

location

Execute

Fetch operand from specified location and execute as

instruction; do not modify PC

Skip

Increment PC to skip next instruction

Skip Conditional

Test specified condition; either skip or do nothing based

on condition

Halt

Stop program execution

Wait (hold)

Stop program execution; test specified condition

repeatedly; resume execution when condition is satisfied

No operation

No operation is performed, but program execution is

continued

Input (read)

Transfer data from specified I/O port or device to

destination (e.g., main memory or processor register)

Output (write)

Transfer data from specified source to I/O port or device

Start I/O

Transfer instructions to I/O processor to initiate I/O

operation

Test I/O

Transfer status information from I/O system to specified

destination

Translate

Translate values in a section of memory based on a table

of correspondences

Convert

Convert the contents of a word from one form to another

(e.g., packed decimal to binary)

Transfer of Control

Input/Output

Description

Conversion

© 2016 Pearson Education, Inc., Hoboken, NJ.

All rights reserved.

Table 12.3

Common

Instruction Set

Operations

(page 2 of 2)

(Table can be found on page

426 in textbook.)

Usage of Transfer Control instructions

To be able to execute set of instructions more than once.

While (x ==y){

1

Load x

2

Sub y

3

BRZ 5

instructions here

4 BR 8

}

5

instructions here

6

….

7

BR 1

8

AFTER LOOP

Usage of Transfer Control instructions

To be able to make decision.

If (x y){

1

Load X

2

Sub Y

3

BRZ 6

4

Instruction 1

instruction 1

}else {

instruction 2

}

5 BR 7

6

Instruction 2

7

remaining instructions

Branch Instruction

Branching

A conditional branch causes a branch

only if a specified condition is satisfied.

If the condition is not satisfied, the PC

(program counter) is incremented in the

normal way, and the next instruction in

sequential address order is fetched and

executed.

Move

N,R1

Clear

R0

LOOP

Program

loop

Ex: Consider the task of adding a list of n

numbers:

The addresses of the memory locations

containing the n numbers are symbolically given

as NUMl, NUM2, ..., NUMn

A separate Add instruction is used to add each

number to the contents of register R0.

After all the numbers have been added, the result

is placed in memory location SUM.

Determine address of

"Next" number and add

"Next" number to R0

Decrement R1

Branch>0

LOOP

Move

R0,SUM

•

•

•

SUM

N

n

NUM1

NUM2

•

•

•

NUMn

CODE:

Move N,Rl

;R1n number of elements stored at N memory location,

;used as a counter for loop

Move #NUMl,R2

Clear R0

LOOP :

Add (R2),R0

Add #4,R2

;location of the first number

;R0 0

; R0 R0+ number in this location

;point to next number as memory is doubleword =32bit

;width

Decrement R1; R1R1-1

Branch>0

LOOP ;branch if R1>0

Move R0,SUM

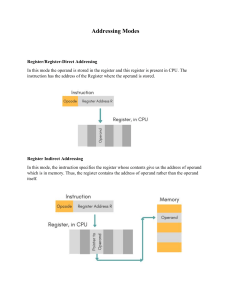

Addressing modes.

The different ways in which

the location of an operand

is

specified

in

an

instruction.

There are five basic

addressing modes:1. Immediate,

2. Register,

3. Absolute (Direct),

4. Indirect,

5. Index

And

RELATIVE addressing

Name

Assem bler syntax

Addressingfunction

Immediate

#Value

Operand = Value

Register

Ri

EA= Ri

Absolute(Direct) LOC

EA= LOC

Indirect

(Ri)

(LOC)

EA= [Ri]

EA= [LOC]

Index

X(Ri)

EA= [Ri] + X

Relative

X(PC)

EA=[PC] + X

(Ri)+

EA= [Ri]

Increment Ri

Autoincrement

Autodecrement

(ــRi)

EA: effective address

Decrement Ri

EA= [Ri]

1. Immediate mode –

The operand is given explicitly in the instruction.

Ex:

Move 200immediate , R0

Places the value 200 in register R0. Clearly, the Immediate

mode is only used to specify the value of a source operand.

A common convention is to use the sharp sign (#) in front of

the value to indicate that this value is to be used as an

immediate operand. Hence, we write the instruction above in

the form

Move #200,R0

R0

200

2.

Register mode - The operand is the contents of a processor

register; the name (address) of the register is given in the

instruction ex: Move R1,R0

R0

R1

2.

Absolute[Direct] mode - The operand is in a memory location;

the address of this location is given explicitly in the instruction.

(In some assembly languages, this mode is called Direct.)

Ex: Move LOC,R2 Memory

:

LOC

R2

:

4. Indirect mode

The effective address of the operand is the contents of a register

or memory location whose address appears in the instruction.

Add (R2),R0

Or

Add (A),R0

Index mode - The effective address of the operand is

generated by adding a constant value to the contents of a

register.

EA = X + [Ri]

The Indexed mode commands are formatted as X(Rn), where X

is a constant and Rn is one of the CPU registers. The absolute

memory location X+Rn is addressed.

Ex:

Add 20(R1),R2

5.

RELATIVE addressing

1. Relative mode –

The effective address is

determined by the Index

mode using the program

counter(PC) in place of

the

general-purpose

register Ri.

0

1

2

PC = 2

+

100

101

102

103

104

X= 100

Move X(PC), R1

R1

1 1 0 A

Additional Modes

Autoincrement mode - The effective address of the operand is the

contents of a register specified in the instruction. After accessing the

operand, the contents of this register are automatically incremented

to point to the next item in a list.

(Ri)+

But in a byte addressable memory, this mode would only be useful in

accessing successive bytes of some list.

Autodecrement mode - The contents of a register specified in the

instruction are first automatically decremented and are then used

as the effective address of the operand.

-(Ri)

Ex:

Question:

Write a program, using assembly language , that can evaluate the

expression

Dot Product

Sol:

To compute the dot product of two vectors. Let A and B be two

vectors of length n. Their dot product is defined as

N

Avec

n

Dot Product

Bvec

DotProduct

:

:

:

:

Type

Data Transfer

Arithmetic

Logical

Operation Name

Description

Move (transfer)

Transfer word or block from source to destination

Store

Transfer word from processor to memory

Load (fetch)

Transfer word from memory to processor

Exchange

Swap contents of source and destination

Clear (reset)

Transfer word of 0s to destination

Set

Transfer word of 1s to destination

Push

Transfer word from source to top of stack

Pop

Transfer word from top of stack to destination

Add

Compute sum of two operands

Subtract

Compute difference of two operands

Multiply

Compute product of two operands

Divide

Compute quotient of two operands

Absolute

Replace operand by its absolute value

Negate

Change sign of operand

Increment

Add 1 to operand

Decrement

Subtract 1 from operand

AND

Perform logical AND

OR

Perform logical OR

NOT (complement)

Perform logical NOT

Exclusive-OR

Perform logical XOR

Test

Test specified condition; set flag(s) based on outcome

Compare

Make logical or arithmetic comparison of two or more

operands; set flag(s) based on outcome

Set Control

Variables

Class of instructions to set controls for protection

purposes, interrupt handling, timer control, etc.

Shift

Left (right) shift operand, introducing constants at end

Rotate

Left (right) shift operand, with wraparound end

© 2016 Pearson Education, Inc., Hoboken, NJ. All rights reserved.

Table 12.3

Common

Instruction Set

Operations

(page 1 of 2)

(Table can be found on page

426 in textbook.)

Type

Operation Name

Jump (branch)

Unconditional transfer; load PC with specified address

Jump Conditional

Test specified condition; either load PC with specified

address or do nothing, based on condition

Jump to Subroutine

Place current program control information in known

location; jump to specified address

Return

Replace contents of PC and other register from known

location

Execute

Fetch operand from specified location and execute as

instruction; do not modify PC

Skip

Increment PC to skip next instruction

Skip Conditional

Test specified condition; either skip or do nothing based

on condition

Halt

Stop program execution

Wait (hold)

Stop program execution; test specified condition

repeatedly; resume execution when condition is satisfied

No operation

No operation is performed, but program execution is

continued

Input (read)

Transfer data from specified I/O port or device to

destination (e.g., main memory or processor register)

Output (write)

Transfer data from specified source to I/O port or device

Start I/O

Transfer instructions to I/O processor to initiate I/O

operation

Test I/O

Transfer status information from I/O system to specified

destination

Translate

Translate values in a section of memory based on a table

of correspondences

Convert

Convert the contents of a word from one form to another

(e.g., packed decimal to binary)

Transfer of Control

Input/Output

Description

Conversion

© 2016 Pearson Education, Inc., Hoboken, NJ.

All rights reserved.

Table 12.3

Common

Instruction Set

Operations

(page 2 of 2)

(Table can be found on page

426 in textbook.)

Good Luck