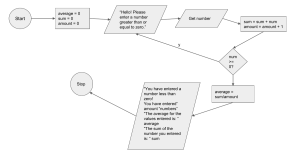

###### This document is to give a idea about the PD Flow #####

DATA PREPARATION:

Make a setup file which contains all the files mentioned below:

.vg (generally DFT Inserted netlist)

.sdc (timing constraint file)

.libs

.lefs (tech lef, macro lef and std. cell lefs)

.io (pin assignment file if any)

.cdbs (celtic libraries for cross talk analysis)

Libgens

AUDIT CHECKS

Check the design for the type of cells, IO Pin, Physical info

checkDesign –all –outDir <path>

Check the design for check timing loops, combo loops

check_timing

Utilization

Memory aspect ratio wrt core aspect ratio

Check for preplace timing

timeDesign –prePlace –outDir <path>

FLOORPLAN

Define global net connectivity

globalNetConnect VDD -type pgpin -pin VDD* -inst * -module {} -override -verbose

globalNetConnect VSS -type pgpin -pin VSS* -inst * -module {} -override -verbose

Fix Io pin status

Add endCaps (at both the ends of each std. cell row)

addEndCap -postCap <cell_name> -preCap <cell_name>

Place macros

Add soft blockages around macros

Spacing between macros (based on no. of pins, making sure enough space is left

between macros for timing fixes)

Add tapCells

addWellTap -cell <cell_name> -cellInterval 50.00 -checkerBoard -fixedGap startRowNum 1

Add endCaps (along the edges of the macros)

addEndCap -postCap <cell_name> -preCap <cell_name>

Check the placement

checkPlace

Save the design

saveDesign DBS/init.enc

PG PLAN

Draw the PG Stripes

For vertical layer

addStripe -block_ring_top_layer_limit <layer_name> -max_same_layer_jog_length

<num> -padcore_ring_bottom_layer_limit <layer_name> -set_to_set_distance

<num> -ybottom_offset <num> -stacked_via_top_layer <layer_name> padcore_ring_top_layer_limit <layer_name> -spacing <num> -merge_stripes_value

<num> -direction horizontal -layer <layer_name> -block_ring_bottom_layer_limit

<layer_name> -width <num> -nets {VSS VDD } -stacked_via_bottom_layer

<layer_name> -allow_jog_block_ring <num>

For horizontal layer

addStripe -block_ring_top_layer_limit <layer_name> -max_same_layer_jog_length

<num> -padcore_ring_bottom_layer_limit <layer_name> -set_to_set_distance

<num> -stacked_via_top_layer <layer_name> -padcore_ring_top_layer_limit

<layer_name> -spacing <num> -xleft_offset <num> -allow_jog_padcore_ring <num>

-xright_offset <num> -layer <layer_name> -block_ring_bottom_layer_limit

<layer_name> -width <num> -nets {VSS VDD } -stacked_via_bottom_layer

<layer_name> -allow_jog_block_ring <num>

add vias

editPowerVia -skip_via_on_wire_shape {Ring Followpin Corewire Blockwire Iowire

Padring Fillwire Noshape} -bottom_layer <layer_name> -add_vias 1 -top_layer

<layer_name>

SRoute

sroute -connect { corePin floatingStripe} -layerChangeRange { lower_layer_name

top_layer_name } -blockPinTarget { nearestTarget } -deleteExistingRoutes checkAlignedSecondaryPin 1 -allowJogging 0 -crossoverViaBottomLayer

<lower_layer_name> -allowLayerChange 0 -targetViaTopLayer <top_layer_name> crossoverViaTopLayer <top_layer_name> -targetViaBottomLayer

<lower_layer_name> -viaConnectToShape { stripe } -corePinMaxViaWidth <num> corePinLayer 2 -targetPenetration { stripe <num> }

Check for opens and shorts

Save the design

saveDesign DBS/init.enc

PLACE

Attach the IO Buffers

attachIOBuffer -in <buffer_name> -out <buffer_name> -port -markFixed excludeClockNet -baseName MPIN_BUF -excNetFile <file_name>

Set the attributes for placement

To specify the tool to perform placement based on timing driven, congestion driven,

module aware placement, so on.

Place the std. Cells

placeDesign

Check the placement

checkPlace

Tool generally performs trial route automatically. Check for congestion (make sure there

are no local hotspots and the congestion value is in the specified limit)

Save the design

saveDesign DBS/place.enc

PRE CTS OPT

This is the 1st optimization in the design

The optimization can be done by giving priority to the specific path groups, we can use

the creatPathGroup option to create the path groups.

optDesign –preCTS –outDir <path> -numPaths <no .of paths to report>

Save the design

saveDesign DBS/prects.enc

CTS

Before creating the clock tree spec, we must enable the all modes (func,

scan,mbist,bscan) in which the design is being run

Generate the clock tree spec

createClockTreeSpec –file <file_name> -buffer_list <list of buffer to be used>

Set the skew value, insertion delay, leaf and non leaf transition, list of inverters and

buffers to be used.

Clock group, leaf pins, exclude pins,

Specify the NDR (non default rules)

Macro models

Analyze the clock tree and check the coverage of the clock tree network

ckSynthesis –check -forceReconvergent

Build the clock

ckSynthesis -forceReconvergent

Save the design

saveDesign DBS/cts.enc

POST CTS OPT

In postCTS stage, we can perform the optimization for both setup and hold.

Optimize the design by propagating the clocks

To propagate the clocks use set_propagated_clocks [all_clocks]

optDesign –postCTS –outDir <path> -numPaths <num>

to optimize for hold

optDesign –postCTS –hold –outDir <path> -numPaths <num>

Save the design

saveDesign DBS/postcts.enc

DETAIL ROUTE

Perform the detail route

Make sure the attributes for SI aware route is set

globalDetailRoute

Save the design

saveDesign DBS/route.enc

POSTROUTE OPT

Optimize the design if any timing violations are there

optDesign –postRoute

Save the design

saveDesign DBS/postroute.enc

PDV

Check the design for shorts, opens

Perform LVS, LPC, DRC, Antenna Checks