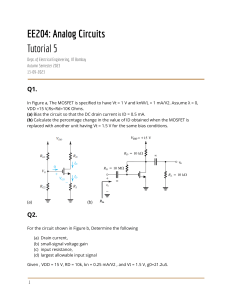

MOSFET Analysis: Construction, Characteristics, and Amplifiers

advertisement

Electronic Circuits Unit No.: 1: MOSFET & its Analysis Syllabus: Enhancement MOSFET: Construction, Characteristics, DC Load line, AC equivalent ckt, Parameters, Parasitics. Non ideal characteristics: Finite output resistance, Body effect, Sub-threshold conduction, breakdown effects, temperature effect, effect of W/L ratio, Common source amplifier & analysis, Source follower: circuit diagram, comparison with common source, Frequency response for amplifier Mapping of Course Outcomes for Unit I: CO1: Assimilate the physics, characteristics and parameters of MOSFET towards its application as amplifier. 1.1 : Introduction to MOSFET: A MOSFET is “Metal oxide semiconductor field effect transistor”. It is a three terminal active device with drain (D), source (S) & gate (G). Basically it is a field-effect transistor with a MOS structure. MOSFET is a voltage controlled device. There are two types of MOSFET: 1) Depletion type MOSFET 2) Enhancement type MOSFET The symbols of E-MOSFETs are as follow: i) n-channel (n-type) Enhancement MOSFET: or Fig-1: Symbol of n-channel (n-type) Enhancement MOSFET ii) p-channel (p-type) Enhancement MOSFET: or Fig-2: Symbol of p-channel (p-type) Enhancement MOSFET 1.2 : Construction & working of E-MOSFET: Construction: A MOSFET is a three terminal and a voltage controlled device. The construction layer diagram of n-channel enhancement type is shown in fig. The thickness of n- layer determines blocking capability of device. The first N+ layer is the source layer and the second N+ layer is the drain layer. The gate is insulated by a SiO2 layer. The body (p) is shorted with source terminal to avoid unnecessary conduction of parasitic BJT. The E-MOSFET has no channel between source and drain. The substrate extends completely to the SiO2 layer so that no channel exists. N-channel enhancement type is more common because of higher mobility of electronics. Because of its construction, the MOSFET has a very less chip area than BJT, which is 5% of the occupancy when compared to bipolar junction transistor. Fig-3: Construction of n-channel enhancement type MOSFET Symbol of E-MOSFET: • • • The significance of 3 MOSFET terminals are as follow: Source: The majority of the source of carriers required for the device enters through this terminal. Through a source terminal, current enters the channel, which is denoted by IS Drain: The majority of the carriers in the channel leaves through this terminal. That is draining. Hence, conventional current enters the channel, which is denoted by ID. Gate: This terminal always controls the conductivity of the channel. Hence, the flow of current in the output is controlled with the help of a voltage level across the gate. Working: The n-channel E-MOSFET requires a proper +ve gate voltage to form a channel, called induced channel between the source and the drain. It operates only in the enhancement mode and has no depletion mode. By applying +ve VGS, +ve VDS, the device starts conducting. The minimum value of VGS which turns on the E-MOSFET is called gate threshold voltage VGS(th). Hence for proper MOSFET conduction, i) VGS ≥ VGS(th) ii) VDS > 0 When positive gate voltage VGS is applied then the minority carriers i.e. holes, get repelled and the majority carriers i.e. electrons gets attracted towards the SiO2 layer. Hence in MOSFET, current conduction takes place due to only majority carriers, so MOSFET is “bipolar” in nature. With some positive VGS & VDS, a certain amount of drain current ID flows from drain to source. When both positive voltages, VGS & VDS are further increased, the current ID increases due to the flow of electrons. Hence the more positive the applied VGS & VDS, the more the value of drain current ID will flow. The current flow ID gets enhanced due to the increase in electron flow better than in depletion mode. Hence this mode is termed as Enhanced Mode MOSFET. 1.3 : MOSFET characteristics: 1) Output characteristics: (VDS – ID) The o/p characteristics of power MOSFET is shown in fig. Fig.4: V-I (o/p) / Drain characteristics There are three regions of operations: i) Cut off region: In this region no drain current flows w.r.t. VDS through MOSFET due to VGS < VGST and MOSFET remains off. Hence MOSFET is operated as an open switch in cut-off region. ii) Ohmic / linear region: In this region VGS ≥ VGST & VDS >0, drain current flows through MOSFET i.e. it becomes on. The drain current ID changes w.r.t. VDS & VGS. Due to high drain current and low drain voltage, the MOSFET is operated as a closed switch in ohmic / linear region. iii) Pinch-off / saturation region: In this region VDS > (VGS - VGST) and MOSFET conducts. The drain current ID remains constant w.r.t. VDS but changes with VGS. MOSFET is operated as an amplifier in this saturation region / Pinch-off region. 2) Transfer characteristics: (VGS – ID) As i/p impedance of MOSFET is very high, current gain (ID/ IG) is in the order of 109. For MOSFET operation current gain is not an important parameter but ‘transconductance’ is very important parameter which is ratio of drain current ID to gate voltage VGS , defines the transfer characteristics. The transfer characteristics is shown in fig.5. Fig.5. Transfer characteristics 1.4 : Voltage Divider Biasing Circuit for MOSFET Fig.6: Voltage Divider Biasing Circuit for MOSFET Working: 1) Voltage divider biasing circuit consists of 4 resistors: R1, R2, RD & RS. 2) Resistors R1& R2 form a voltage divider network and decide the position of Q-point on DC load line. 3) When VDD is applied, current will flow through R1 & R2 and IG is zero due to isolated gate due to SiO2 layer. Also current flows through RD, MOSFET & RS. 4) Resistor RD limits the drain current and also controls the o/p resistance hence voltage gain. 5) RS is a stabilization resistance and also controls the voltage gain. 1.5 : DC Load line: In graphical analysis of nonlinear electronic circuits, a load line is a line drawn on the characteristic curve, (a graph of the current vs. the voltage) in a nonlinear device like a MOSFET. The points where the characteristic curve and the load line intersect are the maximum possible voltage VDD & ID(max) as show in following fig.7 Fig.7: DC load line 1.6 : Common Source Amplifier: Common source (C-S) amplifier is shown in fig.8 Fig.8: Common source (C-S) amplifier In common source amplifier input signal is given to gate terminal & output is taken from drain terminal, hence it is called “common source” (C-S) amplifier. Here voltage divider biasing circuit is used for its biasing. The component wise functions are given as follow: 1) Resistors R1 & R2: Resistors R1 & R2 perform voltage divider biasing circuit. They control the location / position of Q-point on dc load line so that there will not be any distortion in amplified output. 2) Input coupling capacitor: C1: C1 blocks any DC component if present in AC input signal & passes pure AC input to gate terminal 3) Output coupling capacitor: C2: At o/p terminal drain a DC component from VDD is mixed with amplified AC output signal. So C2 blocks DC component present in AC output signal & passes pure AC output. 4) Resistor RD: RD limits drain current through MOSFET and controls the voltage gain of amplifier. 5) Resistor RS: RS provides Q-point stability and also controls the voltage gain of amplifier. 6) Bypass capacitor Cs: Bypass capacitor Cs is connected across Rs. During amplifier operation at high frequency, Cs provides low reactance path to amplified AC output signal. As Cs is in parallel with Rs, low reactance of Cs shorts Rs hence Cs bypasses Rs. Therefore Cs is called “bypass capacitor”. 7) Input & Output waveforms: Fig.9: Input & output waveforms of (C-S) amplifier Here +ve half cycle starts from 0 but +ve output half cycle starts from π i.e 1800. Hence output of C-S amplifier is out of phase by 1800 w.r.t. input. It means there is phase shift of 1800 between input & output. Therefore voltage gain of C-S amplifier is indicated by -ve sign i.e. output is negative in C-S amplifier. Small signal analysis (AC analysis) of Common Source Amplifier: 1) Small signal model / AC equivalent circuit of Common Source Amplifier (without series resistance RSi): Fig.10: AC equivalent circuit of Common Source Amplifier without RSi Mathematical formulae: 1) Transconductance: gm It is a ratio of drain current to gate-source voltage. gm = id / Vgs gm = 2K (VGSQ – VGST) But IDQ = K (VGSQ – VGST)2 2) Dynamic output resistance: ro It is ratio of change in drain voltage to change in drain current at constant gate voltage. ro = | δVDS / δID | ……at constant VGS ro = 1 / (λ.ID) 3) Input impedance / Input resistance: Zi or Ri Zi = Ri = RG Zi = Ri = R1 || R2 4) Output impedance / Output resistance: Zo or Ro Zo = Ro = ro || RD 5) Voltage gain: Av It is ratio of output voltage to input voltage of an amplifier. Av = - gm . Zo Av = - gm . (ro || RD) If ro >> RD, then Av = - gm . RD 2) Small signal model / AC equivalent circuit of Common Source Amplifier (with series resistance RSi): Fig.11: AC equivalent circuit of Common Source Amplifier without RSi Mathematical formulae: 1) Transconductance: gm It is a ratio of drain current to gate-source voltage. gm = id / Vgs gm = 2K (VGSQ – VGST) But IDQ = K (VGSQ – VGST)2 2) Dynamic output resistance: ro ro = 1 / (λ.ID) 3) Input impedance / Input resistance: Zi or Ri Zi = Ri = RG Zi = Ri = R1 || R2 4) Output impedance / Output resistance: Zo or Ro Zo = Ro = ro || RD 5) Output voltage: Vo = - gm . Vgs . Ro Vo = - gm . Vgs . (ro || RD) Where Vgs = [ Ri / (Ri + Rsi )] . Vin 6) Voltage gain: Av Av = (- gm . Vgs . Ro) / Vin Av = (- gm . Ri . Ro) / ( Ri + Rsi) 1.7 : Non ideal characteristics: 1) Finite or limited output resistance: The MOSFET had finite or limited output resistance at saturation mode and active mode of operation. The resistance at any device will be functioned by the flow of current at the channels, this is possible due to the formation of the electric field by the charged carrier. Finite resistance at MOSFET is also due to the channel length modulation process. ro= 1/λk(VGS-VGST)2 But K = Id /(VGS-VGST)2 The output resistance ro = 1/ (λ *ID) 2) Body effect: In MOSFET, source and body terminals are both connected together and into ground. But what if the body is not connected to the source? If the body is not connected to the source and it is connected to a different potential, then this causes the threshold voltage to vary according to the below formula: Vt=Vt0+γ ((Φs+Vsb)1/2 – Φs1/2) where Vt0 is the threshold voltage when Vsb=0, γ is the body effect coefficient and Φs is the surface potential at threshold. From the above formula, we can infer that the threshold voltage increases with source voltage and decreases with body voltage. 3) Channel Length Modulation: As VDS increases, the depletion region increases and the channel length becomes shorter. The current through the channel Ids is inversely proportional to the length of the channel. Hence with decrease in the channel length, the current increases. Channellength modulation is important because it decides the MOSFET output resistance. The effect of channel‐length modulation is less for a long‐channel MOSFET than for a short‐channel MOSFET 4) Subthreshold Conduction • When VGS < the threshold voltage VGST , MOSFET will be in threshold region / weak inversion region • From experimental results, one can observe that there is still some non-zero current flowing from drain to source even when we are operating at a region with (subthreshold region). This effect is called as “subthreshold or weak inversion conduction.” This happens because, for the subthreshold region, the substrate near oxide-interface is in “Weak-Inversion”. At this point, if we apply a positive VDS , there will be a small current flowing. For the conduction in the MOSFET; we need VGS > the threshold voltage VGST . • • • • • 5) Temperature effect • • • • • • Temperature variations affect the device characteristics of MOSFETs thereby varying the performance of integrated circuits. Propagation delay of a circuit is a function of the drain saturation current produced by active transistors. Performance of an integrated circuit under temperature fluctuations is determined by a set of device parameters. Temperature fluctuations alter threshold voltage, carrier mobility, and saturation velocity of a MOSFET. Temperature fluctuation induced variations in individual device parameters have unique effects on MOSFET drain current. The dominant parameter that determines circuit speed varies with the device/circuit bias conditions. Variation of the drain current (IDS) of NMOS and PMOS transistors with supply voltage (VDD). At higher supply voltages, the drain saturation current of a MOSFET degrades when the temperature is increased. 6) Breakdown effects If applied VDS is very high to a MOSFET, junction between drain & substrate becomes heavily reverse biased. This causes avalanche multiplication to take place and hence ‘avalanche breakdown’ occurs. Various factors for breakdown are as follow: • Breakdown due to avalanche multiplication: • Breakdown due to punch-through effects: • Breakdown due to static charge: 1.8 : MOSFET- Source Follower (Common Drain Amplifier): In the Common Drain Amplifier configuration, the drain terminal is at AC ground. The input is applied between the gate and drain terminals, while the output is measured between the source and drain terminal. Since the drain terminal is common between the input and output side, it is known as Common Drain Amplifier. Fig.12: Common Drain Amplifier / Source follower The source follower is a circuit with a voltage gain slightly less than or equal to 1 and with a high input impedance and a low output impedance. Hence i/p =~~ o/p The Common Drain Amplifier has 1) High Input Impedance 2) Low Output Impedance 3) Sub-unity voltage gain Since the output at the source terminal is following the input signal, it is also known as Source Follower. 1.9 : Frequency response for MOSFET (C-S) amplifier Frequency response is a characteristics curve plotted between voltage gain vs frequency. Frequency response of C-S amplifier is shown below: Fig.13: Frequency response of C-S amplifier In low frequency band, gain of amplifier is low. This gain is low due to the effect of coupling & bypass capacitors. Here it is assumed that their imedances are small enough to act as short circuits. In mid-band, the amplifier gain is maximum and remains constant w.r.t. frequency. In this mid-band, all capacitances effects are neglected. In high frequency band, gain of amplifier is low. This gain is low due to the effects of internal capacitances. Cut-off frequencies: i) Lower cut-off frequency (FL): It is a lower frequency from which voltage gain increases by 3dB and reaches to maximum gain is known as Lower cut-off frequency (FL). Or It is a lower frequency at which voltage gain drops by 3dB is known as Lower cut-off frequency (FL). ii) Higher cut-off frequency (FH): It is a higher frequency at which maximum gain drops by 3dB is known as Higher cut-off frequency (FH). iii) Bandwidth: BW: The maximum range of frequency to which amplifier can sustain with good performance / output is known as “bandwidth” BW = FH - FL Comparisons: 1) Power MOSFET & BJT: Sr. No. 1 2 3 4 5 6 7 8 9 10 11 12 Parameter / factor Construction: Power MOSFET SiO2 layer is present to isolate the gate Operation: It is a voltage controlled device Current Current conduction is due to only conduction: majority carriers, hence it is unipolar Input impedance: It is very high due to presence of SiO2 layer Switching times: ton & toff are very small It is very high due to smaller ton Switching & toff frequency: On state It is larger resistance: On state losses: Due to larger on state resistance, on state losses are more i.e. on state voltage drop is 2V – 5V Temp. It has positive temp. coefficient coefficient of res. of resistance i.e. PTC Second Second break down does not breakdown: occur Current sharing resistor does not Parallel require for parallel operation due operation: to PTC property. i.e. direct paralleling can be done. Efficiency: It is less BJT SiO2 layer is absent in the construction It is a current controlled device Current conduction is due to both majority & minority carriers, hence it is bipolar It is low due to absence of SiO2 layer ton & toff are larger It is low due to larger ton & toff It is smaller Due to smaller on state resistance, on state losses are less i.e. on state voltage drop is 0.7V – 1.5V It has negative temp. coefficient of resistance i.e. NTC Second break down occurs in BJT Current sharing resistor is required for parallel operation due to NTC property. i.e. direct paralleling cannot be done. It is more 2) Common source amplifier & Common drain amplifier: Sr. No. 1 2 3 4 5 Parameter / factor Common terminal: o/p voltage nature Voltage gain Input impedance Output impedance Common source amplifier Common terminal is source w.r.t. input & output. o/p voltage is out of phase by 180 degree with i/p Voltage gain is maximum (high) Input impedance is high Output impedance is low Common drain amplifier Common terminal is drain w.r.t. input & output. o/p voltage is in phase (zero degree) with i/p Voltage gain is unity Input impedance is very high Output impedance is very low