Digital Control Systems

Design via Frequency Response

Technique

Controller Types

• Lead compensator

w 1

C ( w) K

, 0< 1

w 1

when is very small, can be approximated as PD control

• Lag compensator

w 1

C ( w) K

, 1

w 1

For large , can be approximated as PI control

• Lead-Lag compensator

Can be approximated as PID control

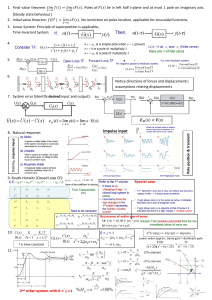

Lead Compensator

Transfer function: C ( w) K w 1 , 0< 1

w 1

Frequency response:

20log K 20log(1/ )

20log K

1

If

1

1

max , max is given, pole and zero of C (w) is obtained as

1 sin max

1 sin max

1

max

The gain K will be determined from the Ess specification

Lead Characteristic

Comparison:

Key Idea:

The lead compensator will

enlarge the gain crossover

frequency and increase

the PM. However, the GM

can not be designed from

the lead compensator

PM new PM old max

max gc (new)

Design Example (1)

Design a lead compensator for the digital control system below

so that the PM is 50, the GM is at least 10 DB

R( s )

+

-

T 0.2

C(z)

ZOH

K

s( s 1)

Y ( s)

and the static velocity error K v 2

Sol. Obtain the discrete-time plant (by Matlab or by hand)

K

1

1

G ( z ) (1 z )Z {L { 2

}}

s ( s 1)

K (0.01873z 0.01752)

2

z 1.8187 0.8187

Design Example (2)

By using the bilinear mapping, we obtain

Gw ( w) G ( z ) |

z

1 ( w /2)T 1 0.1w

1 ( w /2)T 1 0.1w

K (0.000333w2 0.09633w 0.9966)

w2 0.9969w

The controller is in the form of

Cw ( w)

w 1

, 0< 1

w 1

Design Example (3)

Design technique:

Step 1 Compute the gain that satisfies the required K v

Kv lim wCw (w)Gw (w) K 2

w0

Step 2 Set K 2 , find Bode plot of

Gw ( w)

2(0.000333w2 0.09633w 0.9966)

Gw ( w)

w2 0.9969w

Matlab command: bode(2*Gw)

Step 3 Determine PM from the Bode diagram

Here, we get PM=30 (approximately)

Matlab command: [Gm,Pm,Wcg,Wcp] = margin(2*Gw)

Design Example (4)

Design Example (5)

Step 4 Estimate required phase lead

max PM new PM old

50 30 8 28

Step 5 Compute the lead factor

(1 sin 28 ) / (1 sin 28 ) 0.361

Step 6 Find the new “gain cross over freq.” from

| Gw ( jgc ) | 10log(1/ ) dB 4.425 dB

By reading the Bode diagram, we get gc 1.7 rad/s

Design Example (6)

Step 7 Get corner frequencies for zero and pole

1

1

0.9790

gc 1.7 0.361

0.3534

The lead compensator is

w 1 0.9790w 1

Cw ( w)

w 1 0.3534w 1

Step 8 Verify margins from the Bode plot of Cw ( w)Gw ( w)

Step 9 If everything is OK, obtain the controller in z-plane

2.3798 z 1.9387

C ( z ) Cw ( w) | 2 z 1

w

z 0.5589

T z 1

Design Example (7)

Discussion (Lead Comp.)

Advantage

• Improve phase margin

• Improve high-frequency performance

• Improve the speed of the response

Disadvantage

• May have effects from high-frequency noise

• Generate large signals which may damage the system

Lag Compensator

w 1

Transfer function: C ( w) K

, 1

w 1

Frequency response:

20log K

20log K 20log

1

1

The gain K will be determined from the Ess specification

Lag Characteristic

Comparison:

Key Idea:

The lag compensator will

reduce the gain crossover

frequency to where the

phase margin is satisfied

5 -10 deg.

Phasenew Phaseold

The zero corner frequency

1/ is set to 1 decade

below the new gain cross

over frequency

Design Procedure (Lag Comp.)

1. Determine the gain K to satisfy the requirement on Ess

2. Find the new gain cross-over frequency gc such that

PM gc PM desired

3. Choose the corner frequency 1 one decade below gc

4. Magnitude reduction from the lag comp. at gc is equal

to 20log , then is determined from

) | 20 log

20 log | KG ( jgc

w 1

5. Obtain the lag comp. C ( w) K

w 1

6. If all the requirements are satisfied, C ( z ) Cw ( w) |

w

2 z 1

T z 1

Discussion (Lag Comp.)

Advantage

• Low-frequency characteristics is improved or maintained

• Stability margins are improved

• BW is reduced

reduce effects from high-freq. noise

Disadvantage

• BW is reduced

slower rise time

• Numerical problems with controller coefficients may result

in bad control performance

Lag-Lead Compensator

Objective : Cascade a phase-lag compensator with a phaselead compensator to change the overall system characteristics

1 w

1 w

C w K

K

1

w

1

w

Approximation of a PID controller

Lag compensator :

increase the low-frequency gain

Lead compensator :

increase BW and stability margin

Lag section

lead section

Reading Materials

K. Ogata, “Discrete-time Control Systems” , Chapter 4,

pp. 225-242 . See also problems A-4-10, A-4-11, and A-4-12