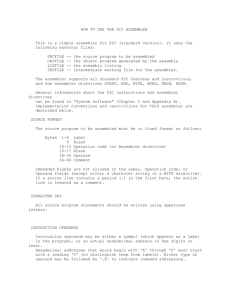

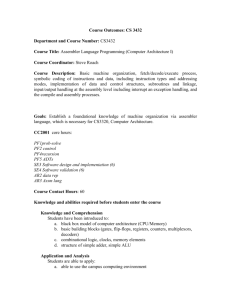

Assembler Language Programming Lecture Slides for IBM System z

advertisement