This article has been accepted for inclusion in a future issue of this journal. Content is final as presented, with the exception of pagination.

IEEE JOURNAL OF SOLID-STATE CIRCUITS

1

A Second-Order Noise-Shaping SAR ADC With

Passive Integrator and Tri-Level Voting

Haoyu Zhuang , Wenjuan Guo , Jiaxin Liu , Member, IEEE, He Tang , Member, IEEE, Zhangming Zhu ,

Long Chen , Student Member, IEEE, and Nan Sun, Senior Member, IEEE

Abstract— This paper presents a low-power and scalingfriendly noise-shaping (NS) SAR ADC. Instead of using operational transconductance amplifiers that are power hungry

and scaling unfriendly, the proposed architecture uses passive

switches and capacitors to perform residue integration and

realizes the path gains via transistor size ratios inside a multipath dynamic comparator. The overall architecture is simple and

robust. Since the noise transfer function is set by component

ratios, it is insensitive to process, voltage, and temperature (PVT)

variations. Besides the proposed architecture, this paper also

presents two new circuit techniques. A tri-level voting scheme

is proposed to reduce the comparator noise. It outperforms the

majority voting technique by exploiting more information in the

comparator output statistics and providing an extra decision

level. A dynamic multi-phase clock generator is also proposed to

guarantee non-overlapping and support an arbitrary number of

phases. A prototype 9-bit NS-SAR ADC is fabricated in a 40-nm

CMOS process. It consumes 143 µW at 1.1 V while operating at

8.4 MS/s. Taking advantage of the second-order NS, it achieves

a peak SNDR of 78.4 dB over a bandwidth of 262 kHz at the

oversampling ratio of 16, leading to an SNDR-based Schreier

figure of merit (FoM) of 171 dB.

Index Terms— Analog-to-digital converter, majority voting

(MV), multi-phase non-overlapping clock generator, noise shaping (NS), successive approximation register.

I. I NTRODUCTION

S

AR ADC is a power-efficient architecture for mediumresolution applications. It is also simple to design, mostly

digital, and scaling friendly. However, for high-resolution

Manuscript received May 21, 2018; revised August 28, 2018 and

December 13, 2018; accepted February 10, 2019. This work was supported in

part by NSF under Grant 1254459, Grant 1509767, and Grant 1527320. This

paper was approved by Associate Editor Andrea Baschirotto. (Corresponding

author: Haoyu Zhuang.)

H. Zhuang is with the School of Electronic Science and Engineering,

University of Electronic Science and Technology of China, Chengdu 611731,

China, and also with the Department of Electrical and Computer Engineering, The University of Texas at Austin, Austin, TX 78712 USA (e-mail:

hyzhuang@uestc.edu.cn).

W. Guo, L. Chen, and N. Sun are with the Department of Electrical

and Computer Engineering, The University of Texas at Austin, Austin,

TX 78712 USA (e-mail: wjguo@utexas.edu; nansun@mail.utexas.edu).

J. Liu is with the Department of Electronic Engineering, Tsinghua University, Beijing 100084 China, and also with the Department of Electrical

and Computer Engineering, The University of Texas at Austin, Austin,

TX 78712 USA.

H. Tang is with the School of Electronic Science and Engineering, University of Electronic Science and Technology of China, Chengdu 611731,

China.

Z. Zhu is with the School of Microelectronics, Xidian University,

Xi’an 710126, China.

Color versions of one or more of the figures in this paper are available

online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2019.2900150

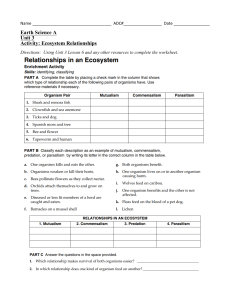

Fig. 1.

ADC.

Concept of NS SAR ADC. (a) Standard SAR ADC. (b) NS SAR

applications, its power efficiency degrades due to the tough

requirement on the comparator noise and the exponentially

growing capacitor DAC array. A widely used architecture for

high-resolution applications is the ADC. Taking advantage of oversampling and noise shaping (NS), it can reach

high resolution with a low-resolution quantizer and DAC.

Nevertheless, ADC usually requires high-performance

OTA-based active integrators, which are power hungry and

scaling unfriendly.

NS SAR ADC is an emerging hybrid ADC architecture

that aims to combine the benefits of both SAR and ADCs while simultaneously obviating their drawbacks [1]–[9].

Comparing to a classic SAR, the NS-SAR ADC can achieve

higher resolution by using NS. It relaxes the requirement on

the raw SAR quantizer resolution. Comparing to a classic

ADC with a low-resolution flash quantizer, the NS-SAR

has a higher quantizer resolution and, thus, can reduce the

oversampling ratio (OSR), leading to enlarged bandwidth

and/or reduced clock rate. In addition, it uses the same DAC

array for both quantization and feedback, which reduces the

circuit complexity. Furthermore, its conversion residue is small

and readily available after the SAR operation. This greatly

simplifies the design of the loop filter and relaxes the filter

linearity requirement, leading to significant power saving. The

limitation for the NS-SAR is that its SAR quantizer is slower

than a flash and, thus, is difficult to support a high sampling

rate (e.g., beyond 1 GS/s), but it is well suited for low-tomedium speed applications where power efficiency is a critical

consideration.

0018-9200 © 2019 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

See http://www.ieee.org/publications_standards/publications/rights/index.html for more information.

This article has been accepted for inclusion in a future issue of this journal. Content is final as presented, with the exception of pagination.

2

Fig. 2.

IEEE JOURNAL OF SOLID-STATE CIRCUITS

Proposed second-order passive NS-SAR architecture.

Fig. 1 shows the functional diagram of a standard SAR

ADC and a NS-SAR ADC. As can be seen, the only difference

between them is that an NS-SAR ADC uses a filter to further

process the conversion residue Vres and feeds the result to

the comparator. The function of the filter is the same as

that in ADCs, which is to memorize the residue and

subtract it from the next conversion cycle, thereby realizing

NS. There are different ways to realize the filter. Some prior

works use OTA to build active filters [1]–[3]. By using OTA,

good NS effect (i.e., aggressive noise transfer function) can

be achieved. However, OTA consumes high power and is

scaling unfriendly, requiring large device gain and supply

voltage. To save power and be more compatible to CMOS

scaling, the works in [4] and [5] choose to use dynamic

amplifiers instead of OTAs. Nevertheless, the gain of the

dynamic amplifier is sensitive to process, voltage, and temperature (PVT) variations. Digital background calibration can

be used to ensure PVT robustness as in [5], but it increases

the design complexity and takes time to converge. Recently,

several researchers propose to use switches and capacitors to

implement fully passive filters [6]–[8]. These passive switched

capacitor filters are simple, low power, robust, and scaling

friendly. Moreover, they are very well suited for low dutycycle sensor applications. Different from the OTA-based filter,

they do not consume any active power or require a stable

operating point. They can wake up immediately and do not

need any guard time for bias circuits to settle, which can

greatly save the overall system power. However, prior works

using passive filters have limited NS effect. Only first-order

NS is achieved in [6] and [7]. Although second-order shaping

is realized in [8], its SNDR is limited to only 65 dB because

of its mild noise transfer function.

To overcome the limitations of prior passive NS-SAR ADC

works, this paper proposes a novel NS-SAR architecture.

It adds only a few switches and capacitors to a standard

SAR ADC but can achieve second-order NS. It can also be

readily extended to even higher order shaping. Since passive

switched capacitor integrators do not provide gain by themselves, the required path gains are realized via transistor size

ratio inside a multi-path strong-arm latch-based comparator.

It is insensitive to PVT variations as its noise transfer function

is set by component ratios. Besides the proposed architecture,

this paper also presents two new circuit techniques. A tri-level

voting scheme is proposed to reduce the comparator noise.

It outperforms the majority voting (MV) technique in [10] by

exploiting more information in the comparator output statistics

and providing an extra decision level. A low-power multiphase clock generator is also proposed to guarantee nonoverlapping and allow an arbitrary number of clock phases.

To validate the proposed architecture and circuit techniques,

a prototype 9-bit NS-SAR ADC is fabricated in a 40-nm

CMOS process. It consumes 143 μW from a 1.1-V supply

while operating at 8.4 MS/s. Enabled by the second-order NS,

it achieves 78.4 dB of SNDR over the bandwidth of 262 kHz

at the OSR of 16, leading to an SNDR-based Schreier figure of

merit (FoM) of 171 dB.

This paper is an extension of [9]. It is organized as follows. Section II presents the proposed second-order NS-SAR

architecture, including its basic operation, various forms of

nonidealities, and PVT robustness. Section III discusses the

proposed tri-level voting technique. Section IV describes the

arbitrary-phase non-overlapping clock generator. Section V

shows the measurement results. Finally, Section VI concludes

this paper.

II. P ROPOSED S ECOND -O RDER PASSIVE NS-SAR ADC

A. Basic Operation

Fig. 2 shows the architecture of the proposed secondorder NS-SAR ADC. Although the real implementation is

fully differential, a single-ended version is shown here for

simplicity. The capacitive DAC is 9-bit with 1-bit redundancy.

Four switches and three capacitors are added to realize secondorder passive integration. The three-input-path comparator

adds up the DAC output Vres with the two integrator outs Vint1

and Vint2 .

The proposed ADC adopts a synchronous clocking scheme.

The external master clock clk is divided into 20 phases by

This article has been accepted for inclusion in a future issue of this journal. Content is final as presented, with the exception of pagination.

ZHUANG et al.: SECOND-ORDER NS SAR ADC WITH PASSIVE INTEGRATOR AND TRI-LEVEL VOTING

3

in Fig. 3. The comparator core is a strong-arm latch but is

modified to have three input pairs. By merging the drain

currents of the input pairs, the summation of the three voltages

is realized. Note that this summation is performed dynamically

instead of using a static analog adder. This reduces the circuit

complexity and power.

Because passive integrators do not provide voltage gain,

it is necessary for the comparator to provide gain for Vint1

and Vint2 in order to realize the desired noise transfer function

(see Section II-B). Note that only relative gains among Vres ,

Vint1 , and Vint2 are needed, as the comparator output is always

1 bit. As a result, the relative gains can be realized by sizing

the input pairs of the comparator into specific ratios as shown

in Fig. 3. No extra static amplifiers are needed, which also

simplifies the hardware and saves power.

Fig. 3.

Three-path dynamic comparator for weighted summation.

B. Signal Flow Diagram

a non-overlapping clock generator that will be presented in

Section IV. The first two clock cycles, φe , are used to sample

the input voltage Vin . Bottom-plate sampling is used to reduce

signal-dependent charge injection. The next nine cycles are

used for comparator decisions for the 8 MSB bits plus 1

redundant bit at 16C. The following eight cycles are used to

decide the last 2 LSB bits. To reduce the comparator noise and

improve the decision accuracy, the comparator is fired four

times for each LSB bit to perform tri-level voting. Unlike the

prior MV technique that always makes binary decisions and

quantizes the comparator input to ±1 LSB [10], the proposed

tri-level voting scheme adds an extra middle decision level.

That is, when the comparator decisions are evenly distributed

(i.e., 2 “1”s and 2 “0”s out of 4 repeated comparisons),

the comparator input is quantized to 0 and no update is made

to the DAC. With no additional cost in hardware or power,

the proposed tri-level voting scheme outperforms the MV

technique in [10] by making more use of the comparator

output statistics. More detailed explanations will be provided

in Section III. In the 20th clock cycle φout , the last bit decision

is fed back to the DAC to generate the final residual voltage

Vres . At the same time, a small capacitor Cres is connected

to the capacitive DAC to sample Vres . Afterward, when φns1

goes high, Cres shares charges with Cint1 to perform the first

passive integration. Then, when φns2 goes high, Cres shares

charges with Cint2 to realize the second integration. After the

integration finishes, Cres is reset during φrs and ready to sample

the next residue voltage. By contrast, Cint1 and Cint2 are never

reset, so that they memorize the integration results, which are

necessary for the NS. It is clear from Fig. 2 that φns1 and

φns2 happen during φe , and thus, they do not elongate the

overall conversion time. This implementation is advantageous

than prior NS-SAR works that add extra clock cycles at the

end [2], [5]–[7]. Comparing to a conventional SAR ADC,

the proposed NS-SAR requires only one extra clock cycle

φout to sample the conversion residue. Thus, the overall speed

penalty is small.

A key to realize the second-order NS is the summation of

Vres , Vint1 , and Vint2 during each comparison. This operation

is realized through the three-path dynamic comparator shown

Fig. 4 shows the signal flow diagram of the proposed

NS-SAR ADC, assuming CDAC = Cint1 = Cint2 = C and

Cres = ac/(1 − a). Vin (z) is the input voltage sampled onto

the capacitive DAC, Dout (z) is the ADC output, and thus,

the residual voltage is Vres (z) = Vin (z) − Dout (z). When φout

goes high, this residual voltage is sampled by Cres , making

the voltage on Cres to be (1 − a) · Vres (z). Then, when φns1

goes high, by combining the previous voltage Vint1 (z) · z −1 on

Cint1 with the present voltage (1 − a) · Vres (z) on Cres , a new

voltage Vint1 (z) is generated. Therefore,

a

Vint1 (z)

= (1 − a) ·

Vres (z)

1 − (1 − a)z −1

(1)

which is a first-order integration with a pole at (1 − a). When

φns2 goes high, similarly combining the voltage on Cint2 with

the voltage on Cres . Thus, we have

a2

Vint2 (z)

= (1 − a) ·

.

Vres (z)

[1 − (1 − a)z −1 ]2

(2)

Constituting a second-order integration with two poles at

(1 − a). Then, the previous Vint1 (z) · z −1 , Vint2 (z) · z −1 , and the

present Vin (z) are summed together by the three-path comparator. As can be seen from the integration equations, Vint1 and

Vint2 have gain loss, thus it is necessary to compensate this

gain loss by voltage gains g1 and g2 , which are embedded

inside the comparator.

Finally, through analog-to-digital conversion, this summation result of Vint1 , Vint2 , and Vin is converted into Dout (z) by

adding a quantization error Q(z). Using the signal flow diagram, one can obtain the complete z-domain transfer function

of the ADC

Dout (z)

= Vin (z)

+

[1−(1−a)z−1]2 · Q(z)

. (3)

1+(1−a)(g2a 2 +g1a −2)z−1 +(1−a)2(1−g1a)z−2

By setting g1 = 1/a and g2 = 1/a 2 , the overall transfer

function can be simplified to

Dout (z) = Vin (z) + [1 − (1 − a)z −1 ]2 · Q(z)

(4)

This article has been accepted for inclusion in a future issue of this journal. Content is final as presented, with the exception of pagination.

4

IEEE JOURNAL OF SOLID-STATE CIRCUITS

Fig. 4.

Signal flow diagram of the proposed second-order NS-SAR ADC.

Fig. 5.

Signal flow diagram with non-ideal effects.

which clearly shows the second-order NS. By examining the

signal flow diagram, we can see that the proposed NS-SAR

ADC maps to the cascade of integrators with feed-forward

(CIFF) architecture [11].

As shown in (4), the value of “a” determines the location

of the NTF zeros. A smaller “a” leads to stronger suppression

for the quantization noise, but it would result in a smaller

Cres capacitor and larger kT /C noise. The optimal value

of “a” depends on the target ADC performance and the

balance of this tradeoff. In the prototype ADC, as a proof

of concept, we choose its target SNDR of 80 dB at the OSR

of 16. To leave margin for other noise sources, we budget the

SQNR to be 90 dB, which translates to the 15-bit resolution.

The base SAR quantizer resolution is chosen to be 9 bit

due to its design simplicity. The OSR of 16 provides 2-bit

resolution increase. Thus, we need to get the remaining 4-bit

resolution boost from the loop filter, which corresponds to

an in-band noise suppression of 16 times. Since the NTF

can be approximated as a 2 in the signal band based on (4),

16 times noise reduction translates to a = 1/4. An even

smaller a can also meet the 90-dB SQNR requirement, but

it would lead to the increase in the kT /C noise, which is

undesirable. With a = 1/4, we can derive that Cres = C/3.

We also have g1 = 4 and g2 = 16, which means that the

comparator input pairs have the ratios of 1 : 4 : 16, as shown

in Fig. 3.

This article has been accepted for inclusion in a future issue of this journal. Content is final as presented, with the exception of pagination.

ZHUANG et al.: SECOND-ORDER NS SAR ADC WITH PASSIVE INTEGRATOR AND TRI-LEVEL VOTING

5

C. Effects of Offset, Noise, and Mismatch

Fig. 5 shows how non-ideal effects influence the signal

flow diagram. Here, we investigate various sources of kT /C

noise, comparator noise, comparator offset, DAC noise, and

DAC capacitor mismatch. As shown in Fig. 5, n 1 –n 6 represent

the kT /C noise on different capacitors during different clock

phases: n 1 is the noise on CDAC at the end of φe ; n 2 is the

noise on Cres at the end of φrs ; n 3 is the noise on Cres at the

end of φout ; n 4 is the noise on Cint1 at the end of φns1 ; n 5 is

the noise on Cres at the end of φns1 ; and n 6 is the noise on

Cint2 at the end of φns2 . n 7 represents the comparator input

referred noise. Vos represents the comparator input referred

offset voltage. n 8 represents the DAC noise. ε represents the

error due to DAC capacitor mismatch. This ε shows up both at

the quantizer and inside the feedback path, as the same DAC

is used for both quantization and Vres generation. The mean

squared values of n 1 –n 6 are derived and shown in Fig. 5.

With g1 = 1/a and g2 = 1/a 2 , the z-domain transfer

function considering nonidealities can be calculated, as shown

in Fig. 5. It shows that the front-end kT /C noise n 1 –n 4 are not

suppressed as they are directly added to the input signal. n 5 –n 6

are first-order shaped. Based on the equations, we can properly

choose C to meet the in-band thermal noise specification. The

comparator noise n 7 , the DAC noise n 8 , and the comparator

offset Vos are second-order shaped, together with the quantization error Q(z). Note that even though the comparator noise

n 7 is second-order shaped, it can still dominate the in-band

noise of the ADC due to its large value. For example, the inband noise breakdown of the prototype ADC is as follows:

the comparator noise power is 1.2 × 10−9 V 2 , the total kT /C

noise power is 1.1 × 10−9 V 2 , and the quantization noise

power is 0.3 × 10−9 V 2 . The comparator is the largest noise

contributor. The reason for a large comparator noise is that the

two extra paths in the three-path comparator degrade its noise

performance. Take the comparator used in the prototype ADC

as an example, its three input pairs have the widths of W , 4W ,

and 16W . Comparing to a classic one-path comparator with

the same total input pair width of 21W (to keep the same

comparator power consumption), the noise of the three-path

comparator, when input referred to the 1X path (marked as

Vres+/− in Fig. 3), is 21 times larger than that of the one-path

comparator. As a result, even though the three-path comparator

input referred noise is attenuated by 16 times due to NS, its

net in-band noise is 21/16 times larger than that of the onepath comparator. In other words, comparing to a classic SAR

ADC with a one-path comparator, the proposed NS SAR ADC

does not bring benefit to the comparator noise. Instead, its

main purpose is to reduce the quantization error and increase

SQNR. In the prototype ADC, the comparator noise reduction

is achieved by using the proposed tri-level voting technique in

Section III.

For an NS-SAR ADC, the overall error transfer function

(ETF) for the DAC mismatch error ε is one, as shown in Fig. 5.

This holds true for any value of a, g1 , and g2 . This behavior

is the same as that of a conventional SAR ADC. Thus,

standard SAR DAC mismatch error calibration techniques

can be applied to the proposed NS-SAR if needed. Another

Fig. 6. Influence of mismatch on gains. (a) Influence of Vth,cm,diff on g1 .

(b) Influence of Vth,cm,diff on g2 .

Fig. 7.

Influence of g1 and g2 variations on SNDR.

effective and hardware-efficient way to suppress ε is to use

error-feedback (EF)-based mismatch error shaping techniques

as in [3] and [12]. Unlike classic dynamic element matching

techniques that require unit-element DACs [13], they can be

directly applied to binary weighted DACs and, thus, are wellsuited for SAR ADCs.

D. Robustness Against PVT Variations

To examine the robustness of the proposed NS-SAR ADC,

let us investigate the locations of NTF zeros and poles.

As shown in (3), its zero location is set solely by the capacitor

ratio a and, thus, is robust against PVT variations. The pole

locations depend on a, g1 , and g2 . Since g1 and g2 represent

the strength of different input pairs and are first-order set by

This article has been accepted for inclusion in a future issue of this journal. Content is final as presented, with the exception of pagination.

6

Fig. 8.

IEEE JOURNAL OF SOLID-STATE CIRCUITS

Stability criteria for g1 and g2 .

size ratios of the same type of transistor, they are also insensitive to process corner, temperature, and voltage variations.

Yet g1 and g2 can change due to random mismatch in the

transistor threshold voltages. Each of the six comparator input

transistors has random V th mismatch. For each transistor pair,

we can define a common-mode mismatch and a differentialmode V th mismatch

Vth,dm ≡ Vth, p − Vth,n

(5)

Vth,cm ≡ (Vth, p + Vth,n )/2

(6)

where Vth, p and Vth,n represent the V th mismatch in

the positive and negative sides of the transistor pair. The

differential-mode mismatch Vth,dm contributes to the overall

ADC offset, but it does not affect the values of g1 and g2 .

By contrast, the common-mode mismatch Vth,cm changes

the effective overdrive voltage of the comparator input pair

and, thus, alters the relative strength of different transistor

pairs, affecting g1 and g2 . For example, if the common-mode

threshold voltage of the 4X transistor pair is lower than that of

the 1X transistor pair, the 4X transistor pair will have a larger

overdrive voltage and be stronger than expected, leading to

g1 > 4. In the prototype ADC, the V th standard deviation of

the 1X transistor is simulated to be 3.8 mV. Based on this

value, we can derive that the 3σ value of Vth,cm = (Vth, p +

Vth,n )/2 difference between the 1X pair and the 4X pair,

as well as the difference between the 1X pair and the 16X pair,

are 9 and 8.3 mV, respectively. To investigate their influence on

g1 and g2 , SPICE simulations have been performed assuming

the worst case ±10-mV Vth,cm difference between different

transistor pairs. The result is shown in Fig. 6 at different

comparator input common-mode voltages Vcm . It can be seen

that a larger Vcm leads to reduced variation in both g1 and g2 as

it has a larger baseline overdrive voltage (similar to a current

source mismatch analysis). In the prototype ADC design, Vcm

is set to half VDD of 550 mV. Therefore, the worst case g1

and g2 variations are within ±20%.

Now, let us investigate the effect of gain variations on the

final ADC performance. Fig. 7 shows the simulated SNDR

versus OSR under the worst case ±20% gain variations.

As can be seen, the SNDR variation is less than ±2 dB,

which demonstrates the robustness of the proposed NS-SAR

ADC architecture. Fundamentally, it is because a, g1 , and g2

are primarily set by component ratios. Even though transistor

Fig. 9. Root-locus plot of the NTF. (a) Pole/zero shift when g1 changes by

±20%. (b) Pole/zero shift when g2 changes by ±20%.

random mismatch can affect g1 and g2 , the overall ADC

performance variation is small.

To ensure loop stability, the poles in the NTF need to be

within the unit circle. The pole locations as a function of g1

and g2 can be derived from (3). By forcing them to be within

the unit circle, we can derive that the stability criterion is

7g1 + g2 < 196/3 for the case of a = 1/4. This inequality

is plotted in Fig. 8. The red shadowed region in Fig. 8 is

the unstable region, and the blue dots are g1 and g2 values

without variations and with ±20% variations each. As can

be seen, even if g1 and g2 vary by ±20%, they are far away

from the unstable region. Therefore, the proposed second-order

NS-SAR ADC is a stable architecture.

Fig. 9 shows how g1 and g2 variations affect the locations of

poles and zeros in the NTF. As can be seen, the NTF has two

zeros and two poles. The zero locations do not shift. The poles

move slightly under g1 and g2 variations. However, even if g1

and g2 vary by ±20%, the poles are still well within the unit

circle. This also demonstrates the robustness of the proposed

architecture.

III. T RI -L EVEL VOTING

A. ADC as Estimation Process

The SAR ADC conversion process can be considered as

a series of operations that aim to minimize the conversion

This article has been accepted for inclusion in a future issue of this journal. Content is final as presented, with the exception of pagination.

ZHUANG et al.: SECOND-ORDER NS SAR ADC WITH PASSIVE INTEGRATOR AND TRI-LEVEL VOTING

7

residue Vres ≡ Vin − Dout . Mathematically speaking, the standard SAR operation can be described by the following set

of equations (for simplicity, the kT /C noise, the comparator

offset, and capacitor mismatch are ignored here)

Vres,1 = Vin

Vres,n+1 = Vres,n

(7)

Vref Cn

− dn · N

i=1 Ci

(8)

where Vin ∈ [−Vref , +Vref ], Vres,n is the conversion residue

before the nth comparison, Cn is the nth capacitor size, and

dn is the nth comparison result given by

+1, for Vres,n + Vnoise,n > 0

dn =

(9)

−1, for Vres,n + Vnoise,n < 0

where Vnoise,n is the input-referred comparator noise during

the nth comparison. If the comparator noise Vnoise,n is very

small, d

n can accurately reflect the sign of Vres,n . Thus, dn ·

N

Ci is a good estimator for Vres,n , leading to a

Vref Cn / i=1

two times reduction in the range of Vres,n+1 . However, when

a low-power dynamic comparator is used, its noise Vnoise,n

can be comparable to the LSB conversion residue Vres,n . This

leads to incorrect decision dn . As a result, Vres,n+1 can no

longer decrease, leading to a limited ADC accuracy.

B. Majority Voting Technique

To effectively reduce the comparator noise and increase its

decision accuracy, the MV technique is proposed in [10]. The

way it works is to perform repeated comparisons and make

the final decision based on the majority

+1, for vote ≥ K /2

dn =

(10)

−1, for vote < K /2

where vote is the number of comparator outputs being “1”

and K is the total number of votes. Despite its effectiveness,

this approach has several limitations. First, it does not make

f ull use of the information embedded in the voting results.

It only cares about whether there are more “1”s or more “0”s.

It does not exploit the detailed distribution of “1”s and “0”s,

which carries additional information. Take a 15-time voting

as an example, the MV technique in [10] does not distinguish

15 or 8 votes as both are majority. However, 15 votes imply

that Vres,n is far away from 0, while 8 votes imply that Vres,n

is very close to 0. This information is not used.

Second, the technique in [10] requires a metastability detector that accurately senses the critical decision levels when

{Vres,n } is small. It needs calibration and increases the design

complexity. In addition, {Vres,n } may fall into metastability

more than once. This causes the total number of comparisons

to fluctuate. This complicates the SAR logic and the clocking

circuit and is not well suited for a modulator whose

quantizer is typically given a fixed amount of time to resolve.

C. Proposed Tri-Level Voting Technique

To obviate the need for the metastability detector as in

[10], the prototype NS-SAR does single comparison for the

first 9 bit (including 1 redundant bit) and only performs

Fig. 10.

Optimal L as a function of K .

repeated comparisons for the LSB bit. The comparator noise,

when referred to the ADC input, has a standard deviation

of 0.56 LSB. Under this condition, it is easy to show that

Vres,10 follows normal distribution with the standard deviation

of 0.8 LSB and has little dependence on Vin [14].

Our goal is to find a new definition of d10 that is a more

accurate estimator for Vres,10 , so that Vres,11 from (8) can

be minimized. A recent research work shows that one can

make full use of the voting statistics and produce a multilevel d10 that is a more accurate estimate for Vres,10 [14].

However, it cannot be directly applied to an NS-SAR ADC:

since the multi-level d10 is a fractional number, it cannot be

easily fed back by the DAC to generate the next conversion

residue Vres,11 required for passive integration. To address this

problem, we propose a tri-level voting technique, in which dn

is defined as follows:

⎧

⎪

⎨+1, for vote > K /2 + L

(11)

dn = 0,

for vote ∈ [K /2 − L, K /2 + L]

⎪

⎩

−1, for vote < K /2 − L

where L is a coefficient that depends on K . For K = 4, L

can be chosen to be 0, so that

⎧

⎪

⎨+1, for vote = 3 or 4

dn = 0,

(12)

for vote = 2

⎪

⎩

−1, for vote = 0 or 1.

When vote = 2, it implies that Vres,n is close to zero, and thus,

dn is set to 0. In this case, the DAC update is trivial. Feeding

back dn = 0 means that the DAC can be just maintained at

its previous state. No action is needed.

The optimal L is defined as the value of L that minimizes

the standard deviation of Vres,11 . In other words, the definition

of dn with the optimal L is the most accurate tri-level estimator

for Vres,10 . This optimal L can be solved using the same

statistical estimation technique as in [14]. Specifically, for

a given K , we can first derive the value of the Bayesian

estimator {V̂res,10 } under different vote values. Then, we find

the value of vote whose corresponding V̂res,10 is near 0.5.

Since 0.5 is the decision boundary for dn = 1 or 0, it is easy

to derive that such vote value is equal to K /2 + L according

to (11), and thus, we can back solve the optimal value for L.

This article has been accepted for inclusion in a future issue of this journal. Content is final as presented, with the exception of pagination.

8

IEEE JOURNAL OF SOLID-STATE CIRCUITS

Fig. 11. Standard deviation of Vres,11 versus K for tri-level voting and MV.

Although the optimal L can be calculated analytically, it can

also be obtained via numerical simulations. We can construct

a behavioral model for the ADC with noise, and then, feed in

a large number of input samples (e.g., > 104 ). For a given K ,

we can sweep the value of L and see which value of L leads

to the minimum standard deviation of Vres,11 .

The optimal value for L as a function of K is plotted shown

in Fig. 10. It shows that L increases with K . This is because

as K increases, even if Vres,n is very close to 0, there is a high

probability to have slightly unbalanced comparator decisions.

With the optimal value of L, the standard deviation of

Vres,11 is plotted in Fig. 11 as a function of K . It shows

that the proposed tri-level voting always outperforms the MV

technique. More importantly, this performance improvement

does not come with any hardware cost. It even lowers the

DAC power by skipping unnecessary updates.

In the prototype ADC, two LSB bits are used (see Fig. 2)

and the proposed tri-level voting is applied for both of them

with K = 4 to reduce the conversion error and boost the

ADC SNR. Comparing to having a single LSB bit with the

tri-level voting of K = 8, having two LSB bits with the trilevel voting of K = 4 yields 2.5-dB higher SNR as it is

able to cover a wider range (±2 LSB). The extra redundant

bit can also recover potential errors because of incomplete

settling [15]. The cost is one extra LSB capacitor and one

extra DAC update. Nevertheless, a SAR DAC typically has

two 1C LSB capacitors for layout matching purpose. Thus,

in reality, there is no need to explicitly add the extra LSB

capacitor.

Fig. 12 shows the simulated distribution of Vres,10 to Vres,12

for different types of ADC inputs. It can be seen that the

distribution of {Vres } has weak dependence on the input.

The proposed tri-level voting technique works well for both

large and small sinusoidal inputs, as well as Gaussian random inputs. It decreases the standard deviation of Vres from

0.81 LSB to 0.37 LSB.

Fig. 13 shows the behavioral simulation results. It can be

seen that two-time tri-level voting with K = 4 outperforms

the rest. It improves the SNR by 4 dB compared to the

case without voting applied. The proposed tri-level voting

technique increases the total comparator power by 70% due to

Fig. 12. Histogram of Vres,10 , Vres,11 , and Vres,12 (a) with a −6-dBFS

sinusoidal input signal, (b) with a −20-dBFS sinusoidal input signal, and (c)

with a Gaussian random input signal whose standard deviation is 10% ADC

full range.

Fig. 13.

voting.

SNR versus amplitude of input signal under different kinds of

seven extra firing. By contrast, to achieve the same 4-dB SNR

improvement in a conventional SAR, the comparator inputreferred noise would have to be reduced from 0.56 LSB to

0.23 LSB through analog scaling (in order to maintain the

same Vres standard deviation of 0.37 LSB, which also includes

0.29 LSB of quantization error). This translates to six times

comparator power increase. As a result, the proposed tri-level

voting technique is much more power efficient than the direct

analog scaling.

Fig. 14 shows the in-band noise breakdown of the prototype

ADC with and without two-time tri-level voting technique.

This article has been accepted for inclusion in a future issue of this journal. Content is final as presented, with the exception of pagination.

ZHUANG et al.: SECOND-ORDER NS SAR ADC WITH PASSIVE INTEGRATOR AND TRI-LEVEL VOTING

9

Fig. 14. In-band noise breakdown of the prototype ADC (a) with no voting

and (b) with two-time tri-level voting.

Fig. 16.

example.

Fig. 15.

Proposed N -phase (N > 2) non-overlapping clock generator.

It can be seen that the tri-level voting reduces both the

comparator noise and the quantization noise through the third

quantization level. It effectively reduces the sum of comparator noise and quantization noise from 1.5 × 10−9 V 2 to

0.6 × 10−9 V 2 .

The proposed tri-level voting technique can be applied to

not only NS-SAR but also standard SAR ADCs. Compared

to the MV technique in [10], the proposed tri-level voting

technique improves SNR but without extra power or hardware

cost. It does not need a metastability detector. It has a fixed

number of comparisons and works well for both synchronous

and asynchronous clocking schemes.

IV. DYNAMIC N ON -OVERLAPPING C LOCK G ENERATOR

As shown in Fig. 2, the master clock clk is divided into

20 phases, out of which φout , φns1 , φns2 , and φrs need to be

non-overlapping. This is to prevent more than two capacitors

to be shorted simultaneously; otherwise, the passive switchedcapacitor filters would not work properly.

The conventional way to construct a multi-phase clock generator for a synchronous SAR ADC is to use a chain of shift

Simulation of the proposed clock generator with N = 5 as an

registers. However, it cannot guarantee non-overlapping in the

presence of device mismatch and PVT variations. The classic

two-phase non-overlapping clock generator, widely used in

switched capacitor circuits, is not suitable either, as the clock

generator needs to produce 20 phases. The clock generators in

[16] and [17] provide four-phase non-overlapping clocks, but

they cannot be easily generalized to any arbitrary number of

non-overlapping clock phases.

This paper proposes a simple and low-power multi-phase

non-overlapping clock generator, whose topology is shown

in Fig. 15. It can support an arbitrary number of nonoverlapping phases. It is built by an array of dynamic D flipflops (DFF) with a modified second stage latch, whose pMOS

transistor M1 is connected not to C L K but rather a delayed

version of a new input terminal DNOL . DNOL is typically

shorted with D inside the DFF array. Because of the inserted

delay τd between DNOL and the gate of M1, signal Q can

rise only after D N O L falls low after τd time, which ensures

non-overlapping. To enable self-startup for the clock generator,

the D terminal in the first DFF is connected to a multi-input

NOR gate, as in a standard shift register-based multi-phase

clock generator. This ensures that there is only one mode of

oscillation regardless of the DFF initial condition. The number

of non-overlapping phases can be easily adjusted by changing

the number of DFFs in the chain.

This article has been accepted for inclusion in a future issue of this journal. Content is final as presented, with the exception of pagination.

10

IEEE JOURNAL OF SOLID-STATE CIRCUITS

Fig. 17.

Chip micrograph of the proposed NS-SAR ADC.

Fig. 18.

Measured power consumption.

Fig. 16 shows the simulated waveform of an example fivephase non-overlapping clock generator using the proposed

structure. The non-overlapping time τd is 115 ps under the

typical condition. The 20-phase non-overlapping clock generator used in the prototype ADC runs with a master clock

of 168 MHz. Its simulated power consumption is only 8 μW

because of its simplicity and the use of dynamic logic.

Similar to a standard shift register, the proposed nonoverlapping clock generator adds only one DFF delay from

the master clock edge to the output clock edges. As a result,

its jitter is small. The SPICE simulation shows that the rms

jitter is 0.5 ps. It does not affect the SNR of the prototype NS

SAR with the signal bandwidth of 262 kHz.

Fig. 19. Measured output spectrum. (a) Before DAC mismatch calibration.

(b) After DAC mismatch calibration.

V. M EASUREMENT R ESULTS

To verify the proposed NS-SAR architecture and circuit

techniques, a prototype ADC is fabricated in a 40-nm CMOS

process. Fig. 17 shows the chip micrograph, whose core area

is 0.04 mm2 . The DAC array capacitor CDAC has a total

capacitance of 4.2 pF and a unit MOM capacitor of 8 fF.

The integrator capacitors, Cint1 , Cint2 , and Cres , are 4.2, 4.2,

and 1.4 pF, respectively. Unlike CDAC , these capacitors do

not need to be partitioned into small unit capacitors, and

thus, they are implemented using high-density capacitors. As a

result, they occupy much smaller area than CDAC (see Fig. 17).

Even though using capacitors with different area densities can

cause slight mismatch, such mismatch only slightly changes

the locations of NTF poles and zeros, and thus, the overall

ADC performance is not affected.

The ADC sampling frequency is 8.4 MS/s. At the supply

voltage of 1.1 V, the chip consumes in total 143 μW, out of

which 55 μW comes from digital circuits such as SAR logic

Fig. 20.

Measured SNR and SNDR versus input amplitude.

and clock generator, 53 μW comes from the comparator, and

35 μW comes from the DAC switching, as shown in Fig. 18.

An off-chip reference buffer is used.

Fig. 19(a) shows the measured ADC output spectrum with

a −3-dBFS 100-kHz input. The slope of the second-order

shaping of (1 − 0.75z −1)2 is clearly seen. The harmonics are

primarily due to capacitor mismatches. At the OSR of 16,

the measured SNDR, which takes into account the second-

This article has been accepted for inclusion in a future issue of this journal. Content is final as presented, with the exception of pagination.

ZHUANG et al.: SECOND-ORDER NS SAR ADC WITH PASSIVE INTEGRATOR AND TRI-LEVEL VOTING

11

TABLE I

C OMPARISON W ITH S TATE - OF - THE -A RT ADC S

to seventh-order harmonics, is 74 dB. Fig. 19(b) shows the

measured spectrum after applying the foreground capacitor

mismatch calibration technique of [18] and [19]. All harmonics

are suppressed to −90 dBFS. The SNDR is improved to 78 dB.

Fig. 20 shows the measured SNR and post-calibration SNDR

versus the input amplitude. The peak SNR and SNDR are

83 and 78.4 dB, respectively. There is a small dip in the SNDR

when the input amplitude approaches the full-signal swing,

which is caused by the nonlinearity in the sample-and-hold

circuit and the ADC input signal.

Table I shows the comparison of the performance of this

prototype ADC with prior NS-SAR ADCs. It achieves 171dB Schreier FoM, which is in-line with the state of the art.

It outperforms prior passive NS-SAR ADCs in both SNDR

and power efficiency. The works using dynamic amplifiers can

achieve higher FoM [4], [5], but the dynamic amplifier gain is

PVT sensitive and, thus, requires either foreground or background amplifier gain calibration. By contrast, the proposed

fully passive NS-SAR architecture does not use any dynamic

amplifier. Its loop filter response is PVT robust.

VI. C ONCLUSION

This paper proposes a simple, robust, low-power, and

scaling friendly second-order NS-SAR ADC. It obviates the

need for operational amplifiers. Instead, it uses switches and

capacitors to build passive integrators and compensate the

signal attenuation by embedding relative gains inside a multipath dynamic comparator. The noise transfer function zeros

and poles are set by component ratios that are PVT insensitive.

It does not consume any static power. Moreover, it does not

require any bias circuit or stable operating point. This property

makes it well suited for sensor applications with low duty

cycle. It can wake up immediately and does not need any guard

time for the bias circuit to settle, which not only simplifies the

system design but also saves the overall system power.

R EFERENCES

[1] J. Fredenburg and M. Flynn, “A 90-MS/s 11-MHz-bandwidth 62-dB

SNDR noise-shaping SAR ADC,” in IEEE Int. Solid-State Circuits Conf.

(ISSCC) Dig. Tech. Papers, Dec. 2012, pp. 468–469.

[2] K. Obata, K. Matsukawa, T. Miki, Y. Tsukamoto, and K. Sushihara,

“A 97.99 dB SNDR, 2 kHz BW, 37.1 μW noise-shaping SAR ADC

with dynamic element matching and modulation dither effect,” in Proc.

IEEE Symp. VLSI Circuits, Jun. 2016, pp. 1–2.

[3] Y.-S. Shu, L.-T. Kuo, and T.-Y. Lo, “An Oversampling SAR ADC with

DAC mismatch error shaping achieving 105 dB SFDR and 101 dB

SNDR over 1 kHz BW in 55 nm CMOS,” in IEEE Int. Solid-State

Circuits Conf. (ISSCC) Dig. Tech. Papers, Dec. 2016, pp. 458–459.

[4] C.-C. Liu and M.-C. Huang, “A 0.46 mW 5 MHz-BW 79.7 dB-SNDR

noise-shaping SAR ADC with dynamic-amplifier-based FIR-IIR filter,”

in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers,

Feb. 2017, pp. 466–467.

[5] S. Li, B. Qiao, M. Gandara, and N. Sun, “A 13-ENOB 2nd -order

noise-shaping SAR ADC realizing optimized NTF zeros using an errorfeedback structure,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig.

Tech. Papers, Feb. 2018, pp. 234–235.

[6] Z. Chen, M. Miyahara, and A. Matsuzawa, “A 9.35-ENOB,

14.8 fJ/conv.-step fully-passive noise-shaping SAR ADC,” in Proc.

Symp. VLSI Circuits, 2015, pp. C64–C65.

[7] W. Guo and N. Sun, “A 12b-ENOB 61μW noise-shaping SAR ADC

with a passive integrator,” in Proc. 42nd Eur. Solid-State Circuits Conf.

ESSCIRC Conf., 2016, pp. 405–408.

[8] Z. Chen, M. Miyahara, and A. Matsuzawa, “A 2nd order fully-passive

noise-shaping SAR ADC with embedded passive gain,” in Proc. IEEE

Asian Solid-State Circuits Conf., Nov. 2016, pp. 309–312.

[9] W. Guo, H. Zhuang, and N. Sun, “A 13b-ENOB 173 dB-FoM 2nd -order

NS SAR ADC with passive integrators,” in Proc. Symp. VLSI Circuits,

2017, pp. C236–C237.

[10] P. Harpe, E. Cantatore, and A. V. Roermund, “A 10b/12b 40 kS/s SAR

ADC with data-driven noise reduction achieving up to 10.1 b ENOB

at 2.2 fJ/conversion-step,” IEEE J. Solid-State Circuits, vol. 48, no. 12,

pp. 3011–3018, Dec. 2013.

[11] S. Pavan, R. Schreier, and G. C. Temes, Understanding Delta–Sigma

Data Converters. Hoboken, NJ, USA: Wiley, 2017.

[12] J. Liu, G. Wen, and N. Sun, “Second-order DAC MES for SAR ADCs,”

Electron. Lett., vol. 53, no. 24, pp. 1570–1572, 2017.

This article has been accepted for inclusion in a future issue of this journal. Content is final as presented, with the exception of pagination.

12

[13] R. T. Baird and T. S. Fiez, “Linearity enhancement of multibit A/D and D/A converters using data weighted averaging,” IEEE Trans.

Circuits Syst. II, Analog Digit. Signal Process., vol. 42, no. 12,

pp. 753–762, Dec. 1995.

[14] L. Chen, X. Tang, A. Sanyal, Y. Yoon, J. Cong, and N. Sun, “A 0.7V 0.6-μW 100-kS/s low-power SAR ADC with statistical estimationbased noise reduction,” IEEE J. Solid-State Circuits, vol. 52, no. 5,

pp. 1388–1398, May 2017.

[15] T. Miki et al., “A 4.2 mW 50 MS/s 13 bit CMOS SAR ADC with

SNR and SFDR enhancement techniques,” IEEE J. Solid-State Circuits,

vol. 50, no. 6, pp. 1372–1381, Jun. 2015.

[16] X.-P. Yu, Y. Fang, and Z. Shi, “2.5 mW 2.73 GHz non-overlapping multiphase clock generator with duty-cycle correction in 0.13 μm CMOS,”

Electron. Lett., vol. 52, no. 14, pp. 1261–1262, 2016.

[17] D. Jeong, S. Lee, H. Lee, and B. Kim, “Ultra-low power directconversion 16 QAM transmitter based on Doherty power amplifier,”

IEEE Microw. Wireless Compon. Lett., vol. 26, no. 7, pp. 528–530,

Jul. 2016.

[18] S.-W. M. Chen and R. W. Brodersen, “A 6-bit 600-MS/s 5.3-mW

asynchronous ADC in 0.13-μm CMOS,” IEEE J. Solid-State Circuits,

vol. 41, no. 12, pp. 2669–2680, Dec. 2006.

[19] H. Garvik, C. Wulff, and T. Ytterdal, “An 11.0 bit ENOB, 9.8 fJ/conv.step noise-shaping SAR ADC calibrated by least squares estimation,” in

Proc. IEEE Custom Integr. Circuits Conf. (CICC), Apr. 2017, pp. 1–4.

Haoyu Zhuang received the B.S. and Ph.D. degrees

from the School of Microelectronics, Xidian University, Xi’an, China, in 2010 and 2017, respectively.

From 2014 to 2016, he was a Researcher with

The University of Texas at Austin, Austin, TX,

USA. He is currently an Assistant Professor with

the School of Electronic Science and Engineering,

University of Electronic Science and Technology

of China, Chengdu, China. His research interests

include analog circuits, such as physically unclonable function, pipeline ADC, SAR ADC, voltage

reference, amplifier, and sampling hold circuit.

Dr. Zhuang was a recipient of the Chinese National Scholarship in 2014,

the Chinese CSC Scholarship in 2014, the Chinese National Encouragement

Scholarship in 2009, the School Principal Scholarship in 2011, the name of

the Best Postgraduate Student in 2011, and the School First-class Scholarship

in 2010, 2012, and 2014. During his study in Xidian University, he ranked

the first in the school for three consecutive years of 2010–2012.

Wenjuan Guo received the B.S. degree from the

Institute of Microelectronics and Nanoelectronics,

Tsinghua University, Beijing, China, in 2011, and

the Ph.D. degree from The University of Texas at

Austin, Austin, TX, USA, in 2016.

From 2013 to 2014, she was a Design Co-Op

with Texas Instruments, Dallas, TX, USA. She is

currently an Analog Engineer with Intel Corporation,

Austin, TX, USA. Her current research is focused on

analog and mixed-signal integrated circuits design.

Dr. Guo was a recipient of the Texas Instruments

Ph.D. Fellowship in 2014 and 2015.

Jiaxin Liu (S’13–M’19) received the B.S. degree

from Shandong University, Jinan, China, in 2010,

and the M.S. and Ph.D. degrees from the University of Electronic Science and Technology of

China (UESTC), Chengdu, China, in 2013 and 2018,

respectively.

From 2015 to 2017, he was a Visiting Ph.D.

Student with the Department of Electrical and Computer Engineering, The University of Texas (UT)

at Austin, Austin, TX, USA. He is currently a

Post-Doctoral Researcher with Tsinghua University,

Beijing, China. His research interest is on analog and mixed-signal integrated

circuits design.

Dr. Liu was a recipient of the First Prize of Academic Scholarship in UESTC

for the consecutive years from 2012 to 2015, the China National Scholarship

in 2012, the First Prize of VeriSilicon Circuits Design Competition in 2015,

and the China CSC Scholarship in 2015.

IEEE JOURNAL OF SOLID-STATE CIRCUITS

He Tang (M’09) received the B.S.E.E. degree from

the University of Electronic Science and Technology of China, Chengdu, China, in 2005, the M.S.

degree in electrical and computer engineering from

the Illinois Institute of Technology, Chicago, IL,

USA, in 2007, and the Ph.D. degree in electrical

engineering from the University of California at

Riverside, Riverside, CA, USA, in 2010.

From 2010 to 2012, he was an Analog IC Designer

with OmniVision Technologies, Inc., Santa Clara,

CA, USA, where he worked on high-speed I/O

interface. Since 2012, he has been an Associate Professor and subsequently

a Professor with the University of Electronic Science and Technology of

China. He has authored or co-authored more than 50 papers. His research

interests focus on data converters and analog/mixed-signal IC designs. His current interest includes high-speed high-resolution low-power digital-calibrated

pipelined/SAR ADCs, and high-performance low-power ROIC designs.

Dr. Tang was a recipient of the Recruitment Program of Global Experts of

Sichuan Province, China, in 2013. He has been serving on IEEE CAS Analog

Signal Processing Technical Committee (ASPTC) since 2013.

Zhangming Zhu received the B.S., M.S., and Ph.D.

degrees in microelectronics from Xidian University,

Xi’an, China, in 2000, 2003, and 2004, respectively.

Since 2009, he has been a Professor with

the School of Microelectronics, Xidian University,

Xi’an. He has authored or co-authored more than

100 papers in journal. His research interests include

date converters, RF ICs, biomedical interface VLSI,

and 3-D ICs.

Long Chen (S’14) received the B.S. degree from the

Institute of Microelectronics, Tsinghua University,

Beijing, China, in 2011, and the Ph.D. degree from

The University of Texas at Austin, Austin, TX, USA,

in 2016.

He was an Intern with the Silicon Laboratories,

Austin, TX, USA, and Taiwan Semiconductor Manufacturing Company Ltd. He is currently a Staff

Design Engineer with Broadcom Ltd., Austin, TX,

USA. His current research interests include lowpower mixed-signal circuits design and CMOS RF

biosensors design.

Nan Sun (S’06–M’11–SM’16) received the B.S.

degree (Hons.) from the Department of Electronic

Engineering, Tsinghua University, Beijing, China,

in 2006, and the Ph.D. degree from the School of

Engineering and Applied Sciences, Harvard University, Cambridge, MA, USA, in 2010.

He is currently an Associate Professor with the

Department of Electrical and Computer Engineering,

The University of Texas (UT) at Austin, Austin, TX,

USA. His current research interests include analog,

mixed-signal, and RF integrated circuits, miniature

spin resonance systems, magnetic sensors and image sensors, micro- and

nano-scale solid-state platforms (silicon ICs and beyond) to analyze biological

systems for biotechnology and medicine.

Dr. Sun was the AMD Endowed Development Chair from 2013 to 2017.

He was a recipient of the NSF Career Award in 2013 and the Jack Kilby

Research Award from UT Austin in 2015 and 2016. He serves on the Technical

Program Committee of the IEEE Custom Integrated Circuits Conference and

the IEEE Asian Solid-State Circuit Conference. He is an Associate Editor of

the IEEE T RANSACTIONS O N C IRCUITS A ND S YSTEM I: R EGULAR PAPERS

and a Guest Editor of the IEEE J OURNAL OF S OLID -S TATE C IRCUITS . He

is currently the Distinguished Lecturer of the IEEE Circuits-and-Systems

Society.