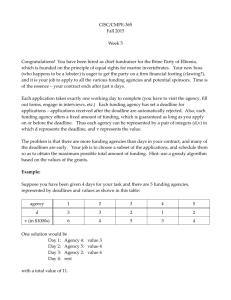

REAL TIME TASK SCHEDULING FOR EMBEDDED SYSTEMS Dr. Amlan Chakrabarti, SMIEE Associate Professor and Coordinator A.K. Choudhury School of Information Technology University of Calcutta (acakcs@caluniv.ac.in) Outline Real time Tasks Scheduling Real time issues for Embedded Systems Real time scheduling techniques for Multicore systems New real time task scheduling methodologies for Reconfigurable Platforms Advance design thoughts Conclusion Real-time System A real-time system is a system whose specification includes both logical and temporal correctness requirements. ◦ Logical Correctness: Produces correct outputs. ◦ Can by checked, for example, by Hoare logic. ◦ Temporal Correctness: Produces outputs at the right time. ◦ It is not enough to say that “brakes were applied” ◦ You want to be able to say “brakes were applied at the right time” Key property ◦ Predictability on timing constraints Types of Real Time Systems Hard real time systems ◦ Must always meet all deadlines ◦ System fails if deadline window is missed Soft real time systems ◦ Must try to meet all deadlines ◦ System does not fail if a few deadlines are missed Firm real time systems ◦ Result has no use outside deadline window ◦ Tasks that fail are discarded Real-Time System Example • Digital control systems – periodically performs the following job: senses the system status and actuates the system according to its current status Control-Law Computation Sensor Actuator 5 Other Real-Time Applications Real-time databases. ◦ Transactions must complete by deadlines. ◦ Main dilemma: Transaction scheduling algorithms and real-time scheduling algorithms often have conflicting goals. ◦ Data may be subject to absolute and relative temporal consistency requirements. Multimedia. ◦ Want to process audio and video frames at steady rates. ◦ TV video rate is 30 frames/sec. HDTV is 60 frames/sec. ◦ Telephone audio is 16 Kbits/sec. CD audio is 128 Kbits/sec. ◦ Other requirements: Lip synchronization, low jitter, low end-to-end response times (if interactive). Characteristics of Real-Time Systems Event-driven, reactive. High cost of failure. Concurrency/multiprogramming. Stand-alone/continuous operation. Reliability/fault-tolerance requirements. Predictable behavior. Notion of Predictability The behavior of the real-time system must be predictable which means that with certain assumptions about workload and failures, it should be possible to show at design time that all the timing constraints of the application will be met. For static systems, 100% guarantees can be given at design time. For dynamic systems, 100% guarantee cannot be given since the characteristics of tasks are not known a priori. In dynamic systems, predictability means that once a task is admitted into the system, its guarantee should never be violated as long as the assumptions under which the task was admitted hold. 8 What’s Important in Real-Time Metrics for real-time systems differ from that for time-sharing systems. Time-Sharing Systems Real-Time Systems Capacity High throughput Schedulability Responsiveness Fast average response Ensured worst-case response Overload Fairness Stability ◦ schedulability is the ability of tasks to meet all hard deadlines ◦ latency is the worst-case system response time to events ◦ stability in overload means the system meets critical deadlines even if all deadlines cannot be met Periodic, Sporadic, Aperiodic Tasks Periodic task: ◦ We associate a period pi with each task Ti. ◦ pi is the interval between job releases. Sporadic and Aperiodic tasks: Released at arbitrary times. ◦ Sporadic: Has a hard deadline. ◦ Aperiodic: Has no deadline or a soft deadline. Task constraints Deadline constraint Resource constraints ◦ Shared access ◦ Exclusive access Precedence constraints ◦ T1 T2: Task T2 can start executing only after T1 finishes its execution Fault-tolerant requirements ◦ To achieve higher reliability for task execution ◦ Redundancy in execution 11 Real-Time Workload 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 = job release = job deadline • Job is released at time 3. • Its (absolute) deadline is at time 10. • Its relative deadline is 7. • Its response time is 6. Job (unit of work) a computation, a file read, a message transmission, etc Attributes Resources required to make progress Timing parameters Real-Time Task Task : a sequence of similar jobs ◦ Periodic task (p,e) ◦ Its jobs repeat regularly ◦ Period p = inter-release time (0 < p) ◦ Execution time e = maximum execution time (0 < e < p) ◦ Utilization U = e/p 0 5 10 15 13 Deadlines: Hard vs. Soft Hard deadline ◦ Disastrous or very serious consequences may occur if the deadline is missed ◦ Validation is essential : can all the deadlines be met, even under worst-case scenario? ◦ Deterministic guarantees Soft deadline ◦ Ideally, the deadline should be met for maximum performance. The performance degrades in case of deadline misses. ◦ Best effort approaches / statistical guarantees 14 Schedulability Property indicating whether a real-time system (a set of real-time tasks) can meet their deadlines (4,1) (5,2) (7,2) 15 Real-Time Scheduling Determines the order of real-time task executions Static-priority scheduling Dynamic-priority scheduling (4,1) (5,2) (7,2) 5 10 15 5 10 15 16 RM (Rate Monotonic) Optimal static-priority scheduling It assigns priority according to period A task with a shorter period has a higher priority Executes a job with the shortest period T1 (4,1) T2 (5,2) T3 (7,2) 5 10 15 5 10 15 17 RM (Rate Monotonic) Executes a job with the shortest period T1 (4,1) T2 (5,2) T3 (7,2) 5 10 15 5 10 15 18 RM (Rate Monotonic) Executes a job with the shortest period Deadline Miss ! T1 (4,1) T2 (5,2) T3 (7,2) 5 10 15 5 10 15 19 Why Are Deadlines Missed? For a given task, consider ◦ preemption: time waiting for higher priority tasks ◦ execution: time to do its own work ◦ blocking: time delayed by lower priority tasks The task is schedulable if the sum of its preemption, execution, and blocking is less than its deadline. Focus: identify the biggest hits among the three and reduce, as needed, to achieve schedulability EDF (Earliest Deadline First) Optimal dynamic priority scheduling A task with a shorter deadline has a higher priority Executes a job with the earliest deadline T1 (4,1) T2 (5,2) T3 (7,2) 5 10 15 5 10 15 21 EDF (Earliest Deadline First) Executes a job with the earliest deadline T1 (4,1) T2 (5,2) T3 (7,2) 5 10 15 5 10 15 22 EDF (Earliest Deadline First) Optimal scheduling algorithm ◦ if there is a schedule for a set of real-time tasks, EDF can schedule it. T1 (4,1) T2 (5,2) T3 (7,2) 5 10 15 5 10 15 23 RM vs. EDF Rate Monotonic ◦ Simpler implementation, even in systems without explicit support for timing constraints (periods, deadlines) ◦ Predictability for the highest priority tasks EDF ◦ Full processor utilization ◦ Misbehavior during overload conditions For more details: Buttazzo, “Rate monotonic vs. EDF: Judgement Day”, EMSOFT 2003. 24 REAL TIME ISSUES IN EMBEDDED SYSTEM What is an Embedded System Its not a PC! Most computer in the world do not have a keyboard and screen The vast majority of computers in the world are small chips that are hidden inside all kinds of products What is an Embedded System? Embedded Systems An embedded system is nearly any computing system (other than a general-purpose computer) with the following characteristics Single-functioned Typically, is designed to perform predefined function Tightly constrained Tuned for low cost Single-to-fewer components based Performs functions fast enough Consumes minimum power Reactive and real-time Must continually monitor the desired environment and react to changes Hardware and software co-existence 28 Where are ESs? Embedded computing systems are becoming pervasive in our society (more than 109 units/year): Robotics Flight control systems Plant control Automotive Consumer electronics Multimedia systems Sensor/Actor Networks Modern day Car as ES Mission: Reaching the destination safely. Controlled System: Car. Operating environment: Road conditions. Controlling System - Human driver: Sensors - Eyes and Ears of the driver. - Computer: Sensors - Cameras, Infrared receiver, and Laser telemeter. Controls: Accelerator, Steering wheel, Break-pedal. Actuators: Wheels, Engines, and Brakes. 30 Car example (contd) Critical tasks: Steering and breaking. Non-critical tasks: Turning on radio. Cost of fulfilling the mission → Efficient solution. Reliability of the driver → Fault-tolerance needs to be considered. 31 Target Platforms for ES Microcontroller-based systems DSP processor-based systems ASIC technology FPGA technology 32 Integration in System Design Integration of Functions Embedded Software Tools CPU CPU Embedded Software Tools Embedded Software Tools FPGA I/O FPGA + Memory + IP + High Speed IO (4K & Virtex) Logic Design Tools Memory Logic + Memory + IP + Processors + RocketIO (Virtex) Logic Design Tools Programmable Systems usher in a new era of system design integration possibilities Logic Design Tools Time 33 What are FPGAs FPGAs are programmable digital logic chip We can program them to do almost any digital function Here's the general flow of working with FPGAs: We use a computer to describe a "logic function" that we want. We might draw a schematic We compile the "logic function", using a software provided by the FPGA vendor. That creates a binary file that can be downloaded into the FPGA Binary file can be downloaded to the FPGA by connecting cable That's it! our FPGA behaves according to our "logic function" Xilinx Spartan 3e & Altera Cyclone Board Why FPGAs are Favorable for ES Customization Complete flexibility to select any combination of peripherals and controllers New, unique peripherals that can be connected directly to the processors bus Component and cost reduction Multiple component systems can be replaced with a single FPGA One can reduce board size and inventory management, both of which will save design time and cost Hardware acceleration Ability to make trade off between hardware and software to maximize efficiency and performance Algorithm with software bottleneck, a custom co-processing engine can be designed in the FPGA specially for that algorithm Main processor and co-processor architecture makes the total Hardware system much accelerated Embedded Design in an FPGA Embedded design in an FPGA consists of the following: FPGA hardware design C drivers for hardware Software design Software routines Interrupt service routines (optional) Real Time Operating System (RTOS) (optional) Basic Requirements for RTOS Requirements Multi-threading and preemptibility Thread priority Thread synchronization mechanisms Priority inheritance Predefined latencies Example of RTOSes for FPGA RTOSes available in market are VxWorks by Wind River Systems, ThreadX by Express Logic, Nucleus Plus by Mentor Graphics, XILKERNEL by Xilinx and many more XILKERNEL Small, robust and modular kernel RTOS Interface with POSIX API Works with both MicroBlaze & PowerPc Highly integrated with EDK lightweight (16Kb-32 Kb) FPGA Based system with Xilkernel Threads Processing using Xilkernel on FPGA Using Xilkernel Thread synchronization can be done by Semaphore and Mutex. Thread communication can be carried out using Shared memory and message queue. Real time resource sharing protocol like (PIP) can be implemented. Though RMS ( real time scheduling) can’t be applied here. But using virtualization RMS can be implemented Sangeet Saha; Amlan Chakrabarti;Ranjan Ghosh., "Exploration of Multi-thread Processing on XILKERNEL for FPGA Based Embedded Systems," Control Systems and Computer Science (CSCS), 2013 19th International Conference (Bucharest, Romania) on , vol., no., pp.58,65, 29-31 May 2013 Real time scheduling techniques for Multicore systems Multiprocessors A multi-core processor is one which combines, two or more independent processors into a single package, often a single integrated circuit. Most high-end computers today have multiple processors In a busy computational environment, multiple processes compete for processor time More processors means more scheduling complexity Real-Time Multiprocessor Scheduling Real-time tasks have workload deadlines Hard real-time = “Meet all deadlines!” Problem: Scheduling periodic, hard realtime tasks on multiprocessor systems. This is difficult. 42 Scheduling Three Tasks Example: 2 processors; 3 tasks, each with 2 units of work required every 3 time units deadline job release Task 1 Task 2 Task 3 time = 0 1 2 3 43 Global Schedule Example: 2 processors; 3 tasks, each with 2 units of work required every 3 time units Task 1 migrates between processors CPU 1 CPU 2 time = 0 1 2 3 44 The Big Goal Design an optimal scheduling algorithm for periodic task sets on multiprocessors A task set is feasible if there exists a schedule that meets all deadlines A scheduling algorithm is optimal if it can always schedule any feasible task set 45 Necessary and Sufficient Conditions Any set of tasks needing at most 1) 1 processor for each task ( for all i, ui ≤ 1 ) , and 2) m processors for all tasks ( ui ≤ m) is feasible Status: Solved pfair (1996) was the first optimal algorithm 46 New real time task scheduling methodologies for Reconfigurable Platforms Why Involving Reconfigurable Platforms Reconfigurable FPGAs can be used as a performance efficient back up platform for real time tasks in a complex safety-critical system This backup platform is activated whenever one or more processors in the system fail Assume the responsibility of executing the real-time tasks that were previously running on the failed processors So, it is essential to have well defined scheduling methodologies, feasibility criteria and admission control mechanisms for real-time task sets in these reconfigurable platforms Such that all timing constraints may be met while taking care of the reconfiguration overheads and also allowing efficient resource utilization Assumptions Processor Identity: All processors are equivalent Task Independence: Tasks are independent Task Unity: Tasks run on one processor at a time Task Migration: Tasks may run on different processors at different times Overhead: Context switch overhead (Full and partial reconfiguration overhead) In practice: built into WCET estimates 49 Concept of Deadline Partitioning Task 1 Task 2 Task 3 Task 4 50 Deadline Partitioning CPU 1 CPU 2 51 DPSFR and DPSPR DPSFR ( Deadline Partitioning Scheduler for Fully Reconfigurable Systems) DPSPR ( Deadline Partitioning Scheduler for Partially Reconfigurable Systems) Equally Partitioned the 2D-reconfigurable space in m homogeneous tiles, where each tasks can be feasibly mapped. Assumed that task have been compiled before to a binary bitstream and rectangular in shape. Tasks has its execution requirement , ei, period =deadline =Pi and taks weights = ei/pi, Each tasks need to complete their execution requirement within their deadline Idea is same as Deadline Partitioning. ( Each task need to complete their share within deadline partition) But Full reconfiguration overhead and Partial reconfiguration overhead is to be considered Promising Results Simulation based experimental results reveal that the DPSFR can achieve fair resource utilization up to 80% (Workload) with TRR less than 10% and DPSPR can utilize resource up-to 90% with 1%TRR ( Task Rejection Rate) Sangeet Saha, Arnab Sarkar, Amlan Chakrabarti, “Scheduling Dynamic Hard Real-Time Task Sets on Fully and Partially Reconfigurable Platforms”, under review at IEEE Embedded System Letters Full Reconfiguration time vs TRR Advance Design Thoughts Software components running on processors exhibit high flexibility but often poor performance Hardware components placed on FPGA modules are of high performance but of low flexibility and higher cost Making a framework to allow seamless mapping and scheduling of real time tasks on these complex platform Low run time overhead, Power budgets and reliability are need to be satisfied Scheduling a task on S/W or H/W is a crucial decision An improper execution would lead to deadline failure and more consumption of power So its serious concern of combined spatial-cum-temporal scheduling Advance Design Thoughts S/W tasks multitasking by proper scheduling scheme among hard & soft core H/W task multitasking via Partial Reconfiguration inside the FPGA logic Overall system utilization be maximized and reliability should be maintained Lower use of Si area with lower consumption of power If we conclude………….. It requires analysis of real time scheduling algorithms on heterogeneous multiprocessor architectures. Develop a comprehensive simulation bed for real time task scheduling on heterogeneous platforms so that various parameters like real-time constraints, cache misses, power consumption etc. may be analyzed. We need a suitable dynamic and static strategy for a task to core assignment in run time reconfigurable FPGA systems with processor core for real time task scheduling. It requires execution of software task by processing elements (ARM or MicroBlaze for Zynq platform) with load balancing and low minimum power consumption. Group Members DR. Arnab Sarkar,Assistant Professor, Dept of CSE, IIT Guwahati (mail : arnabsarkar@iitg.ernet.in) Mr.Sangeet Saha, TCS RSP Fellow, AKCSIT, University of Calcutta (mail:sasakc_s@caluniv.ac.in) Acknowledgements Tata Consultancy Services (TCS) for all kinds of support and encouragement to carry out this research work.