Lecture 04: Single Transistor Ampliers

Analog IC Design

Dr. Ryan Robucci

Department of Computer Science and Electrical Engineering, UMBC

Spring 2015

Dr. Ryan Robucci

Lecture IV

1 / 37

Single-Transistor Ampliers

Common Source

Common Drain

Common Gate

Dr. Ryan Robucci

Lecture IV

2 / 37

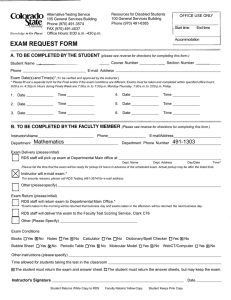

Common Source Aplier (1)

cut- sat

off

nonsat

When leave sat?

Approach: Use equation

VD = VG − VTH

VOUT = VIN − VTH

Must nd unknown voltage

Assume Saturation

VDD −Vout

RD

=

k0 W

L

2

VOUT

in terms of input

2

VGS − VT →Vout = RD

| {z }

Vov

Dr. Ryan Robucci

2

k0 W

L

Lecture IV

2

VGS − VT − VDD

| {z }

Vov

3 / 37

Common Source Aplier (2)

2

VIN − VTH = Vout = RD

VIN − VTH = RD

| {z }

Vov

0

= RD

k0 W

L

2

k0 W

L

2

k0 W

L

2

VGS − VT − VDD

| {z }

V

2ov

VGS − VT − VDD

| {z }

V

2 ov

VGS − VT − VIN − VTH − VDD

| {z }

| {z }

Vov

r

VIN =

−1±

+4RD 2

1

RD k 0 W

L

Vov

k0 W

L

= Vin,sat

Dr. Ryan Robucci

(pos. answer is the obvouis choice)

Lecture IV

4 / 37

Common Source Aplier (3)

For

Vin > Vin,sat

Vout = VDD − RD

k0 W

L

2

For linear region (Vout

2Vov Vout

2

− Vout

2Vov ):

k0 W

L

Vout ≈ VDD − RD 2 (2Vov Vout )

Vout ≈ VDD − RD k 0 W

L Vov Vout

W

0

Vout 1 + RD k L Vov ≈ VDD

= VDD 1 Vout ≈ 1+R VkDD

( D 0 WL Vov )

1+RD

R

ON

Now let

Vout ≈

Vout ≈

RON =

1

k0 W

L

Vov

VDD

1

1+RD

RON

RON

VDD (RON

+RD ) (a simple voltage divider)

Dr. Ryan Robucci

Lecture IV

5 / 37

Common Source Aplier (4)

However the highest gain is in the sat region:

2

k0 W

d RD 2L VGS

|

dV

out,sat

AV = dV

=

in

AV = −gm RD

−V

{z T}

−VDD

Vov

dVin

= −RD k 0 W

L Vov

Compare with Small Signal Approach:

−vo

RD = gm vi

vo

vi = −gm RD

0

(same as before)

What happens when

vo

vi

λ 6= 0

= −gm (RD ||rd )

What is the limit as

RD

is increased?

(RD ||rd ) ≤ RD and (RD ||rd ) rd

RD rd , Rout ≈ rd , Av ≈ −gm rd

rd RD , Rout ≈ RD , Av ≈ −gm rd

Note

If

If

Dr. Ryan Robucci

Lecture IV

6 / 37

Ideal Current-Source Load (1)

RD replaced

Av = −gm rds

With

with

∞

in the small signal model, the gain is:

To set these values in a design, we must choose the bias current.

The value of the current source, Ib , becomes the the transisor bias

current, Ibias , in the design.

Choose Ibias based on desired values for the input voltage bias,

gm ,

power(current),etc..

Dr. Ryan Robucci

Lecture IV

7 / 37

Ideal Current-Source Load (2): Design of the input bias

point

Note: In practice, high-gain circuits have a very limited input range

Some intuative nessisity for for this is as follows:

Output range is practically limited by the supply rails.

Input range size is

output range size

Av

Bias

Point?

Output

Range

Input

Range

Therefore, if output range size is <5 V and gain is Av = 100, the input

range size is <50 mV

For high gain circuits, we conceptually design an input bias point, Vin,bias ,

rather than an input range dened by two values, Vin,min and Vin,max

Typically start by assumming Ibias ≈ ID,sat

Then, Vin,bias is denedrby the decided bias current, Ibias ,

and the relation Vov =

2Ibias

k0 W

L

Dr. Ryan Robucci

Lecture IV

8 / 37

Ideal Current-Source Load (3): Output Range

Vout,max :

The ideal current source presents no maximum on

the output voltage, though if we are approximating a practical

circuit we expect

Vout,min :

Vout < VDD = Vout,max

The transistor presents a lower bound on

Vout

to

maintain saturation

Vout > Vin − Vth

0

Vout,min = Vin,bias − VTH = Vov

0

What parameters aect Vov ?

r

Vov =

2Ibias

k0 W

L

Dr. Ryan Robucci

Lecture IV

9 / 37

Ideal Current-Source load (4): Ex. Design Modication

Take a situation in which after simulation you are satised with the

gain but need to lower the input bias point to make it compatible

with another circuit.

Vout,min without

1

Vov λ I =q

λ Vov

2I

and Vov =

k0 W

How can you lower

Av = −gm rd =

sacracing gain

(−gm × rd )?

1

λ ∝ L1

q

0

Av ∝ k 2WL

I

now,

so,

I

2

L

q

Vov = k20IL

W

maintain Av and lower

input bias determined by

You'll nd that to

the input bias, more than

one free design parameter must be changed.

L

and

I

may be decreased proportionally so that

L

I is constant

The cost of this solution is more size and lower bandwidth

↑ W =⇒ more parasitics

↓ I =⇒ ↑ R =⇒ ↑ (RCout ) =⇒ ↓ B.W.

Dr. Ryan Robucci

Lecture IV

10 / 37

PFET (less-ideal) current source (1)

To design for the PFET choose

Vbias

such that Isat for PFET is the

same as the desired Ibias

To approximate a current source, the L for the PFET can be made

large so that

Rout

is large

Model for saturated PFET acting as current source is shown.

(Optional in-class sidebar current and voltage sources)

Dr. Ryan Robucci

Lecture IV

11 / 37

PFET (less-ideal) current source (2) Gain

Finding Gain: (done as example in-class)

Rout = rd,p ||rd,n

Gm = −gm,n

Av = −gm,n rd,p ||rd,n

Dr. Ryan Robucci

Lecture IV

12 / 37

PFET (less-ideal) current source (3)

Why not just use a resistor with value of

rd,p ?

Take example:

λp =

1

100

−1 V

for a 1- µm eective length device

Ibias = 1 [µA]

rd,p =

1

λ Ibias

=

100

= 100 M˙

the voltage drop with 1 µA would be 100 V!

PFET Leff can be modied to alter the

×10−6

1

For a resistor of 100 M˙,

Furthermore, the

relationship.

Transistor loads allow exibility in terms of designing the

small-signal resistance and bias point.

Dr. Ryan Robucci

Lecture IV

13 / 37

PFET (less-ideal) current source (4): Output range

However, this active load limits output range as compared to an

Ideal current source

as

↑ Vout > Vbias + VTp

replaced with

So

, PFET leaves saturation and

rd,p

is

1

β (VSG −|VTp |)

Vout,max = Vdd − Vsd,sat

Output Range:

Vds,sat,n < Vout < Vdd − Vsd,sat,p

Vov ,n < Vout < Vdd − Vov ,p

OUTPUT RANGE is a key concept in Analog Design

Dr. Ryan Robucci

Lecture IV

14 / 37

Source Follower (Common Drain, Level Shifter) (1)

cutoff

sat nonsat

VGB = VG and VSB = VS

vgb = vg and vsb = vs for the small-signal model

A grounded bulk implies

A xed bulk implies

As

Vi

Ans:

As

Vi

increases when does the transistor leave saturation?

Vi > VDD + VTH

decreases, when is cut-o achieved?

Dr. Ryan Robucci

Lecture IV

15 / 37

Source Follower (Common Drain, Level Shifter) (2)

gm vin =

vo

vin

= gm

vo

Rs

+ gs vo + rvdso

1

1 +g + 1

S r

Rs

ds

rds

= gm gS rds RRSs+R

s +rds

gs Rs 1 and gs rds 1

gm

vo

vin ≈ gs

gm

cox

1

1

gs = n = κ = cox +cdep = 1+η

≈ 1 in strong inversion

if

Dr. Ryan Robucci

Lecture IV

16 / 37

Source Degenerated Amplier (1)

Vin increases I will increase

Vout decreases Vs increases (as in source follower)

When VOUT < VG − VTH FET LEAVES SAT

As

as

At what rate does Vout drop in the high gain region?

To answer, can use small signal analysis.

Dr. Ryan Robucci

Lecture IV

17 / 37

Source Degenerated Amplier (2) (Rout )

Rout = Rup ||Rdown

Rup = RD

Rdown :

vs = it RS

vx = vs + (it + gs vs ) rds

vx = it Rs + (it + gs Rs ) rds

vx

it = Rs + (1 + gs Rs ) rds

vx

it = Rs + rds + gs rds Rs

****This result we will want to utilize often:

resistance looking into drain***

Rdown :

Set Vi xed (0):

Req = Rs + rds + gs rds Rs

gs Rs 1 may ignore rds

gs rds 1 may ignore RS

If both assumptions apply :

Req ≈ gs rds Rs

Rout ≈

RD || (gs rds Rs + Rs + rds )

Dr. Ryan Robucci

Lecture IV

18 / 37

Source Degenerated Amplier (3) (Gm )

A

Set ouput to 0 V

Gm =

io

vi

=?

Dr. Ryan Robucci

Lecture IV

19 / 37

Source Degenerated Amplier (4) (Gm )

vs

gS + r1ds + R1s

Solve for unknown

(1a)

gm vi = vs

(1b)vs

gm

= vi g

1 + 1

Rs

S+r

ds

(2a) note io

= ix = − Rvss

(or just proceed with standard brute-force

KCL)

rds

io = − gS rdsvRi Sgm+R

S +rds

gm rds

io

=

−

vi

gS rds RS +RS +rds

−gm Gm = 1

1

gs + Rs + r

ds

as before, if

using (1b)

Rs

gs Rs rds Rs , rds

Gm ≈ − ggmS rrdsds = − ggms R1s

above threshold

κ ≈1

1

Gm ≈ − Rs

Dr. Ryan Robucci

Lecture IV

20 / 37

Source Degenerated Amplier (5) (Av

Av = Gm Rout =

= Gm Rout )

−gm

(RD || (gs rds Rs + Rs + rds ))

1

1

|

{z

}

Rs gs +

+

≈RD

rds Rs

|

{z

}

≈gs

Under some assumptions:

Av ≈ − ggms RRDs ≈

Rout ≈ RD

BW = Cout1Rout

RD

Rs (make sense?)

Dr. Ryan Robucci

Lecture IV

21 / 37

Source Degenerated Amplier (6) (source node)

Take source node as output instead:

Rout = Rup ||Rdown

Rdown = Rs

Dr. Ryan Robucci

Lecture IV

22 / 37

Source Degenerated Amplier (7) (source node)

Set

vi = 0

Req = vitx =?

vd = iz RD = it RD (simplest equation that is in terms of input)

vy = vd + vds = vd + irds rds = vd + (it − vy gs ) rds (KVL using

resistors)

vy = it RD + (it − vy gs ) rds

Looking into source equation

Req =

vy

it

=

RD +rds

+rds gs

1

Dr. Ryan Robucci

Lecture IV

23 / 37

Resistance Looking into Source

Req =

RD +rds

+gs rds

1

You will sometimes see

Req =

RD +rds

+gm rds if

1

gmb

is ignored

note the following approximations (assuming

if

then

RD rds

RD ≈ rds

RD rds

Req ≈ gRs rDds

Req ≈ g2s

Req = g1s

Dr. Ryan Robucci

Lecture IV

gs rds 1)

24 / 37

Common Gate Amplier (Current Buer)

As

Vin increases,

Vo increases

and

current decreases

Vo

sat

VDD

~gsRD

VG-VTH

FET

Leaves

SAT

VG-VTH VG

Vi

FET is "off"

I is nearly 0

In sat region:

Gm = gs + r1ds ≈ gs

Rout = RD ||rds

Rin (input resistance)

is low (looking into source equation)

Dr. Ryan Robucci

Lecture IV

25 / 37

Common Gate Amplier Output Range

Transistor saturation condition limits ouput:

Vout > VB − VTH

VBqand current:

I

= Vin + k20 W

+ VTH

Bias point of input is tied to

VB = Vin + Vov + VTH

L

Dr. Ryan Robucci

Lecture IV

26 / 37

Common Gate, AC-Coupled

An issue with the previous circuits is that DC current is drawn from

the input. This can be resolved with an AC-coupled input:

DC operating point is independant of the input DC level

DC current is not drawn from input, though AC current is

drawn

Input impedance still low at most frequencies (though DC

input resistance is

∞)

Output resistance is high (RD ||casaded resistance)

Dr. Ryan Robucci

Lecture IV

27 / 37

Common Gate Amplier (Current Buer)

Pseudo

Small-Signal

Pseudo-Small Signal Drawing:

For

this class is a small-signal drawing

using a transistor symbol as a shorthand for the transistor's small signal

Here we'll

assume the

capacitor

can be treated

as a short

equivalence.

If we include a source resistance

RS

between the input voltage

source and source terminal:

Rout = RD || (gm rds Rs + Rs + rds ) ≈ RD

| {z }

if

1

Gm =

1

Rs +

|

!≈

(gm rds Rs +Rs +rds )RD

gs

Rs gs +1

gs + r1ds

{z

}

≈1/gs if gs rds 1

If

1

gs

Rs , Gm ≈

1

Rs

Dr. Ryan Robucci

Lecture IV

28 / 37

Common Gate Current Buer

The original circuit:

Transimpedance

(I-to-V) Amplifier

Current

Buffer

Current-Output

Device

The common-gate transistor can preferably be thought of as a

current buer. In the circuit shown:

looking into the source, the equivelent resistance

than the added output load resistance

is lower

RD .

Looking into the drain, the equvilent resistance

then

RSS

RDD ,

is higher

Rs .

In the common-gate voltage amplier we use

RD

to generate an

output voltage.

Dr. Ryan Robucci

Lecture IV

29 / 37

Common Gate Current Buer Example (1)

Using Common-Gate

Resistor Alone as I-to-V

Sensor-Circuit

(Pseudo) Small-Signal Model

Transimpedance

(I-to-V) Amplifier

Transimpedance

(I-to-V) Amplifier

Transimpedance

(I-to-V) Amplifier

Current

Buffer

Current

Buffer

Assume a sensor with the following characteristics:

100 µA on top of 1 mA bias current with a x output voltage, and

an output resistance of 100K

Assume the sensor parasitic capacitance,

cS ,

is 1 pF

Assume we want 1 V output modulation and bandwith≥100 Mhz

Dr. Ryan Robucci

Lecture IV

30 / 37

Common Gate Current Buer Example (2)

Ideally we want

vo

is

= RD

and we might choose

RD

to be 10 k˙.

However, the actual gain is less because the actual sensor current is

sensitive to the voltage. In this case the output voltage swing,

which we require, is seen by the sensor.

vo

is

= RD ||rs =

k·100k

k+100k

10

10

≈ 9.09k .

An alternative intuition from the small-signal model is that

the ideal

signal current is is divided between

rs

and

RD . iin = −is

rs

rs +RD

(OPTIONAL SIDEBAR ON CURRENT DIVIDER)

Dr. Ryan Robucci

Lecture IV

31 / 37

Common Gate Current Buer Example (3)

An alternative using the common-gate conguration is shown.

We'll assume the transistor along with

Vov = 0.5V

λ=

at 1 mA and

VG

is designed to obtain

1

1000

In this circuit the sensor sees resistance of

Req ≈

1

gs

=

Von

2I

= 250Ω

if

RD rds

.

RD || (rds gs RS + rds + RS ) =

∗ 100k + 100k + 100k) ≈ 10k

The output resistance is

10k|| (4m ∗ 100k

But what about the current

k

k+250 now vs

100

100

iy

Is ?

k

k+10k berfore

100

100

The current split is much better. The sensor sees a lower resistance

yet the output resistance generating the output voltage swing is

still high. The current buer has shielded the sensor from the

voltage swing.

Dr. Ryan Robucci

Lecture IV

32 / 37

Common Gate Current Buer Example (4)

Good Current-Current buer characteristics:

RIN RSOURCE : Input voltage does

not uxuate with current and all intended current uxuations at the

node are drawn into the buer.

Large output resistance, ROUT RLOAD : Output current

delivered to the load does not strongly depend on the output

voltage (which means it is not sensitive to the load resistance). The

ideal intended current is delivered to the load.

Small input resistance,

However, there is one more advantge, even more critical...BW

Sensor Node Resistance

Sensor Node Time Constant

Sensor Node BW

Sensor Node BW

Dr. Ryan Robucci

Resistor

Current Buer

9.09 kΩ

τ = 9.09 ns

110 M rad/s

17.5 MHz

250 Ω

τ = 250 ps

4 G rad/s

637 MHz

Lecture IV

33 / 37

Common Gate Current Buer Example (5)

The lower impedance that the capacitor sees in parallel to it

prevents the capacitor from drawing as much current. Therefore,

the sensing circuit draws a larger percentage of the current. The

-3dB frequency tells us when the capacitor draws an equal current

to the resistance path it parallels.

Transimpedance

(I-to-V) Amplifier

Current

Buffer

Dr. Ryan Robucci

Lecture IV

34 / 37

Finding Time Constant of a Capacitor (1)

We can nd the time constant of a capacitor by

1

replacing capacitor with a current source it

2

nding the voltage

vy

created

vy

it

3

Req =

4

τ = Req · C

Transimpedance

(I-to-V) Amplifier

Current

Buffer

+

-

Dr. Ryan Robucci

Lecture IV

35 / 37

Finding Time Constant of a Capacitor (2)

At

ω = ω−3dB : R =

1

jωC

and

|iR | = |iC |

iR

The time constant provides us the

frequency

ω−3dB =

1

τ

.

iC

At this frequency, the capacitor draws an

equal magnitude of sinusoidal current to

the resistance in parallel with it, though at

a dierent phase.

@DC:

A−3dB =

vx /ix = R = ADC

@ω

= ω−3dB

vx /ix =

r

2

R2 + ω 1 C =

−3dB

q

2

R + (R)2 =

A−3dB

Dr. Ryan Robucci

Note

q

log10

1

ADC

2

q 1

2

≈ −3

Half Power Frequency:

Also note

2

vx,(@ω =ω−3dB ) = 12 vx,(@DC)

|A−3dB |2 = 12 |ADC |2

Lecture IV

2

36 / 37

Reminder

Some hints discussed in solving small signal circuits

Identify variables to eliminate (node voltages or currents) and

try to choose and expression simplilest, most directly related to

the input or output

At times if there is a resistor between a node you have an

expression for and another, nding the voltage accross the

resistor can create a simple expression for the unknown voltage

in terms of the known voltage

When

λ =0

don't both with

When calculating

Gm

rds

throughout your work

and consider the short a t the output, it

is typical that a branch of your circuit can be quickly ignored

Dr. Ryan Robucci

Lecture IV

37 / 37