FinFET with Isolated Gates: Design and Performance

advertisement

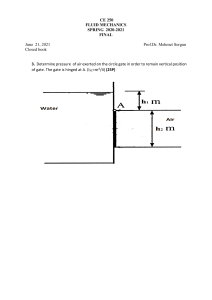

Finfet with isolated n+ and p+ gate regions strapped with Metal and Polysilicon L. Mathew , M. Sadd, B. E. White, A. Vandooren, S. Dakshina-Murthy*, J. Cobb, T. Stephens, R.. Mora, D. Pham , J. Conner, T. White, Z. Shi, A.V-Y Thean, A. Barr, M. Zavala, J. Schaeffer, M.J. Rendon, D. Sing, M. Orlowski, B.-Y. Nguyen, J. Mogab APRDL, DigitalDNA Laboratories 3501 Ed Bluestein Blvd.MD: K10 Motorola Inc-Semiconductor Products Sector (*Motorola-AMD alliance) 3501 Ed Bluestein blvd. Austin TX-7872, U.S.A : ( r26180@email.sps.mot.com, phone: 512 933 2385) Abstract A vertical double Gate MOSFET structure with a new gate stack architecture has been demonstrated. The Gate stack consists of two isolated polysilicon regions that are doped N+ and P+ with a metal/polysilicon strap connecting the doped regions. The device has an undoped channel yet performs as an enhancement mode MOSFET due to the asymmetric doping of the gate regions on either side of the channel. The advantages of this structure include: 1) reduction of the Vt variations caused by dopant fluctuation in the channel region 2) enhanced mobility due to an undoped channel region 3) flexibility to adjust Vt across a wide range from depletion mode to very high Vt depending on the application 4) lower interconnect resistance due to the use of metal/polysilicon gate components 5) better manufacturability due to easier patterning of gate over spacer. The devices are enhancement mode with Vt ~= (0.1-0.3V) at 100nm gate length and channel thickness of less than 30nm and height 100nm tall have been demonstrated. Functional devices at the 100nm gate have Ion =191 µA/ µm , Vt = 0.3V Ioff = 0.5 µA/ µm SS=94 mV/decade.. A different device with different implant dose and drive demonstrated Vt = 0.15V and SS=80mV/decade at Lgate=0.25µm. N+ Channel Metal Introduction Double gate MOSFET structures have been studied to replace the traditional planar CMOS structures [1-5]. These devices have already been demonstrated to offer significant performance improvements[3-5]. The purpose of this work was to demonstrate that the double gate architecture can be further enhanced with the use of undoped channels and metal gate interconnects reducing some of the causes of performance variation but without changing the material properties of the critical gate dielectric to gate electrode interface from traditional integrations. This device structure consists of a FinFET type channel region (Fig 1.a) but wrapped on both sides with poly silicon spacers in the gate region, these spacer gates are doped differently with n+ and p+ dopants. The spacers are then tied together with a combination of metals and polysilicon layers (Fig 1.b). The channel is undoped to keep threshold variations minimal from dopant fluctuations[6] and avoid mobility degradation. Defining the gate on a gradual ramped spacer makes lithography and etch over tall structures easier (Fig 2.). The option to dope the gate electrodes with various dopant species on either side of the channel and keep the dopants from crossmigration allows for wide range of Vt adjustment . The device has thick nitride on top of the channel region and metal over the polysilicon spacer gates. This allows doping the very tall source/drain regions with deep high energy implants without doping the gate and channel region. Process Integration. The process steps used to form this structure does not involve any additional masking steps, the same gate structure can be used for NMOS and PMOS structures. The Silicon active region consists of silicon fins with nitride on top these formed using an etch and trim process on Silicon on Insulator wafers. The channel has been trimmed down to 30nm thickness and are 1000A tall. Gate oxide of 24A is grown over this. Polysilicon gate spacer regions are formed over this channel and two sides are doped N+ and P+ by angled implants. Due to isolated spacers the dopants can be driven using thermal anneals without cross migration of dopants from one side to another like structures that are prone to possibility of crossmigration [5]. This is followed by deposition of metal and polysilicon stack. The metal gate is now patterned over these poly silicon spacers. After etching the stack of metal and polysilcon and removal of nitride over the channel regions, source/drain implants and silicidation is then pursued by standard process to fabricate this device structure as illustrated in Fig. 3. P+ Fig 1a: Isolated N+/P+ Strapped structure, Fig 1 b: Cross sectional through the gate and channel Fig 2: Device showing the smooth line edges of the Metal gate regions over polysilicon spacer gates. Fig 3. Cross sectional view of the device structure. Electrical Characteristics Fig. 4a shows long channel Id-Vg characteristics of a device with 0.25µm gate length. This device shows 80mV/decade sub threshold slope with a linear Vt of 0.14V. We observed that the subthreshold leakage for gate voltage less than 0.1V is dominated by gate leakage based on gate leakage measurement. The enhanced gate leakage is due to quality of the oxide edges, which could be further improved, with reoxidation of the edges damaged during etch. The performance of scaled-down 0.1µm device with a different n+/p+ gate doping is depicted in Fig. 4b. Fig.4a: Id Vg for Lgate=0.25µm ,Fig 4b: Id-Vg Lgate=0.1µm This device shows weaker short-channel control and degraded SS due to the relatively larger body and oxide thickness to gate length ratio. The linear subthreshold slope of this device is measured to be 94mV/decade. The Vt of this device is 0.3V and the Ion is 190µA/ µm and Ioff is 0.5µA/ µm at 1.2V. The Id-Vd characteristics are as shown in Fig 5. The Ion is limited by the resistance in the extension regions as shown by the bunching of the curves at Vd=1.2Vand Vd = 1.5V, this can be improved substantially by optimizing the extension with selective epitaxy, the gate leakage can be reduced more by optimizing the oxidation after etch to reduce edge etch damage. The Short channel effects can be controlled by going to higher gate-length to channel + gate dielectric thickness. Conclusions A new device structure that takes advantage of the double gate and extends its features has been demonstrated. Typical undoped channel integrations of these double gate structures lead to depletion mode transistors; previously enhancement mode transistors have been demonstrated with doped channels[3], or mid-gap gates such as silicided gate electrodes[5]. New gate metals and mid-gap gate materials at the oxide interface offer limited control of threshold voltage and not well understood silicide oxide interfaces [5]. Doped channels lead to reduction in mobility and threshold voltage variations due to doping variations. This device structure can overcome some of these limitations and useful Vt values have been demonstrated. As CMOS scales down to tens of nanometer gate lengths, threshold voltages as low as 0.1V will become necessary, making Vt variation specifications more stringent. Hence dopant fluctuations in the channel will become unacceptable. The demonstrated gate stack consists of well understood materials at the gate dielectric and gate electrode interface using silicon-dioxide and doped polysilicon, but the novel gate electrodes comprising of two isolated regions doped N+/P+ on either side of the channel region prevents dopant redistribution and enables fixing the Vt accurately across a wide range for various applications. A new metal scheme for the gate interconnects that is then capped with polysilicon and the etch process necessary to realize this structure has been developed. This allows for lower interconnect resistance and also allows for traditional subsequent processing with minimal exposure of the new metal gate regions. The entire structure does not use any additional masking steps. Since a common gate can be used for NMOS and PMOS it can save multiple masking steps that involve pre-doping the gate. Additional masks can be used to have multiple Vt devices by varying the dopants in the poly silicon regions across a wide range than traditionally possible without doping the channel or changing the gate dielectric. This novel structure has potential to be used in various mainstream applications. Acknowledgements The Motorola Dan Noble Center for processing the devices and developing the process modules References [1] D. Hisamoto et al, IEEE TED, Vol.38. p 1419-1424,1991 [2] H-S-P. Wong et al. IEDM Tech Dig., 1997 p 427-430 [3} F-L Yang et al, IEDM Tech Dig, 2002, p 255-258 [4] J. Kedzierski et al, IEDM 2001, p 437-440 [5] J. Kedzierski et al, IEDM 2002 , p 247-250 [6] A. Thean et al, IEEE 2002 Silicon Nanoelect. Work., p 25 Fig 5. Id-Vd curves for device with Lgate = 0.1 µm