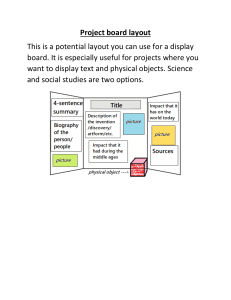

1. INTRODUCTION 1.1 Physical verification While in the digital domain many design steps have been automated through synthesis algorithms attempts to apply such methods in analog design typically fail due to the number and complexity of design constraints that typically emerge from analog circuits. This work presents a practical automation method for IC design assembly using various automation methods for its layout physical verification [1]. These methods can be used along with design verification flow followed in the verification as various violations encountered. Violations are encountered at various stages of verification to automate the determined solution layouts generated. The presented concept shows an enhanced way of verification automation by considering designs for layout versus schematic issues, in order to generate the possible solution for entire circuit, hierarchically consisting of other designs as well as their interconnections. This approach has two vital objectives: first to extensively include designer’s human expertise, knowledge and creativity into the automation, and second to take only small automation steps which enhance the design flow in verification stage . A basic overview of previous design automation techniques evolved in the digital and analog domain. The idea of employing the isolation with respect to different layout objects interacting at top level and the implementation based on schematic guided layout. The objective is to have the functionality observed in the schematic is as such reflecting in the layout. Physical verification tool has to do layout processing & proximity correction comprising rule files for manufacturing. Runtime depends on size of the layout & rules to be checked with increasing complexity of designs. The operation of a circuit by means of reenactments at the schematic level before endeavoring to design is confirmed. LVS verifies the schematic and layout match, so if schematic is not functioning properly layout would not either. Passing LVS at lower levels of hierarchy reduces time and effort at later VEDA IIT Confidential Project Report (PR-I) 1 stages. Any change in schematic or layout requires re-run of LVS tool. Recent improvement in the tools doesn’t require re-run of the LVS tool, but in the same job can be checked against the changes made in the layout. Fig 1.1: Physical verification top view Fig. 1.1 shows how the problem in layout physical verification is resolved using several commands running to produce error output and modified layout (where physical verification for layout modification is used for optimal correction). Turnaround time is reduced to extent possible by using optimal processing platform to determine the command run and part of the layout subject to change, and these combinations used as separate blocks for processing. The results reassembled at the end can be generalised. EDA tools with sign-off checks are used to perform physical verification on the layout before tape out. Number of iterative steps involved in fixing the problems used incrementally between front end designers and back end designers. With shrinking technology geometries, design constraints are becoming time consuming & complex. Design cycle time mostly increased due to lack of information and communication between different stages of implementation. Physical Verification is a later stage process in design cycle. Design problems occurring at later stages results in the delayed tape out. Since lack of information in layout stage of design is in practice because foundry doesn’t need much of the information. Due to which verification becomes cumbersome and tedious task at times. Every tape out run results in the cost involved in fabrication and affect time to market. Fig. 1.2 shows VLSI design flow. VEDA IIT Confidential Project Report (PR-I) 2 Fig 1.2: The diagram of VLSI design flow The VLSI design flow comprising various small steps and widely related to the design constraints. The abstract layout flow for IC design is discussed in this project. 1.2 Verification flow Advances in process technology and increasing design complexity have placed growing demand on physical verification products to check many more design rules. Evolving new physical verification solution geared specifically to address these challenges faced by IC designers. Tool has to be a comprehensive physical verification product which may include DRC, LVS checks, electrical rule checking and metal fill insertion. A layout can be viewed as a schematic drawing for verification and modification. For large designs schematic drawing to represent layout is not preferred for obvious reasons. To tackle this problem database format is used. GDSII serves as a stream format database file format and has been as the standard used by industry for data exchange of integrated circuit or IC layout artwork. VEDA IIT Confidential Project Report (PR-I) 3 It represents planar geometric shapes, text labels and other information about the IC layout. It can be used in sharing, transferring layout artwork between different EDA tools, or creating photo masks for fabrication. Fig. 1.3 shows the summary of physical verification flow for a digital layout. Place and route tool is used to generate the layout for digital design automatically generated based on design. Fig. 1.4 shows the summary of physical verification for an analog layout. Based on different foundries physical layout engineers perform different run based on flow requirement. Fig 1.3: Digital design verification flow Design-to-silicon success with the different tools is flow dependent and vary in time elapsed to perform chip design. The functionality and performance required for continued success at established nodes demand scalable advancements in tools. To integrate and assemble chips, from first pass to successful tape-out time taking and cumbersome. With increasing complexity in designs and size, layout editors lack in quick and efficient visualization, revision and processing. To perform chip finishing on full chip designs, layout making tool lack in efficiency. Layout viewing tools find application in rapid loading and processing large layout files. VEDA IIT Confidential Project Report (PR-I) 4 Fig 1.4: Verification flow for analog design VEDA IIT Confidential Project Report (PR-I) 5 2. LITERATURE REVIEW 2.1 Design Rule Check (DRC): 2.1.1 Introduction to DRC: Design Rule Check (DRC) is the process of checking physical layout data against fabrication-specific rules specified by the foundry to ensure successful fabrication. Process specific design rules must be followed when drawing layouts to avoid any manufacturing defects during the fabrication of an IC. Process design rules are the minimum allowable drawing dimensions which affects the X and Y dimensions of layout and not the depth/vertical dimensions. Violating a design rule might result in a non-functional circuit or low yield. As Technology Shrinks • Number of Design Rules are increasing • Complexity of Routing Rules is increasing • Increasing the number of objects involved • More Design Rules depending on Width, Halo, Parallel Length Table 2.1.1: Technology based DRC rules 2.1.2 DRC issues • Maximum Rules: Manufacturing of large continuous regions can lead to stress cracks. So ‘wide metal’ must be ‘slotted’ (holes). • Angles: Usually only multiples of 45 degree are allowed. • Grid: All corner points must lie on a minimal grid, otherwise an “off griderror” is produced. VEDA IIT Confidential Project Report (PR-I) 6 • Minimum Spacing: The minimum spacing between objects on a single layer. • Minimum Width: The min width rule specifies the minimum width of individual shapes on a single layer. • Minimum Enclosure/ Overlap: Implies that the second layer is fully enclosed by the first one. • Notch: The rule specifies the minimum spacing rule for objects on the same net, including defining the minimum notch on a single-layer, merged object. • Minimum Cut: the minimum number of cuts a via must have when it is on a wide wire. Fig 2.1.2 Few common DRC issues VEDA IIT Confidential Project Report (PR-I) 7 2.2 Layout Versus Schematic (LVS) 2.2.1 Introduction to LVS: DRC only verifies that the given layout satisfies the design rules provided by the fabrication unit. It does not ensure the functionality of layout. Because of this, idea of LVS is originated.Layout Versus Schematic (LVS) verifies the connectivity of a Verilog Netlist and Layout Netlist (Extracted Netlist from GDS) Tool extracts circuit devices and interconnects from the layout and saved as Layout Netlist (SPICE format) As LVS performs comparison between two netlist, it does not compare the functionalities of both the netlist.LVS rule deck is a set of code written in Standard Verification Rule Format (SVRF) or TCL Verification Format (TVF). It guides the tool to extract the devices and the connectivity of IC’s. It contains the layer definition to identify the layers used in layout file and to match it with the location on of layer in GDS. It also contains device structure definitions.Input Requirements given below. • LVS Rule deck • Verilog Netlist • Physical layout database (GDS) • Spice Netlist (Extracted by the tool from GDS) Fig 2.2.1 LVS flow VEDA IIT Confidential Project Report (PR-I) 8 2.2.2 LVS issues • Shorts: Shorts are formed, if two or more wires which should not be connected together are connected. • Opens: Opens are formed, if the wires or components which should be connected together are left floating or partially connected. • Component mismatch: Component mismatch can happen, if components of different types are used (e.g, LVT cells instead of HVT cells). • Missing components: Component missing can happen, if an expected component is left out from the layout. • Parameter mismatch: All components has it’s own properties, LVS tool is configured to compare these properties with some tolerance. If this tolerance is not met, then it will give parameter mismatch. Fig 2.2.2 LVS shorts and opens VEDA IIT Confidential Project Report (PR-I) 9 Fig 2.2.3 Device related LVS issues VEDA IIT Confidential Project Report (PR-I) 10 2.3 Calibre Tool : 2.3.1 About Calibre: Calibre provides fast, sophisticated, and proven technology that enables the fastest and most accurate physical verification of the most challenging designs at any node.Foundries iteratively explore design constraints and manufacturability to define the design rules ultimately used by their customers. The physical verification tool used by every major foundry to develop these design rules is Calibre. What that means to you is that Calibre rule decks are proven long before you need them. When performance and time to market control potential profitability, using Calibre for your physical verification can mean the difference between market success and failure. Calibre is continually evolving to meet the demands of shrinking geometries and complex manufacturing methodologies. When designers need new ways to assess the quality of their designs in light of more complex process constraints and larger process variations, Calibre delivers the new capabilities and enhanced performance that provide comprehensive analysis capabilities while minimizing cycle time. With Calibre nmDRC, designers can confidently manage physical verification for every design, at every node. Calibre tool Runtime and Resource Usage With increasing size and complexity of designs, and the explosion of new rule checks required for the next technology node, the need for faster turnaround time is critical.Calibre delivers the fastest runtimes in the industry, whether you’re using one CPU or dozens, providing you with the flexibility you need to optimize your resource allocation and usage while achieving your desired turnaround time. Calibre performs equally well in either shared memory or distributed processing configurations, and is completely compatible with load balancing and grid computing software. Verification jobs can be run in parallel to support multiple designers completing subsections of a design on the same hardware, then brought together for full chip verification.Calibre nmDRC is constantly enhanced to provide VEDA IIT Confidential Project Report (PR-I) 11 new and more comprehensive physical verification methodologies to manage today’s most complex design requirements. 2.3.2 Features of calibre • Used by every major foundry for process development and validation. • Fast, scalable, flexible resource usage. • Direct access to Milkyway, LEF/DEF, OpenAccess, OASIS, andGDSII design databases. • Calibre eqDRC provides precise characterizations and simplifies debugging of complex multi-variate design issues. • Calibre Fast XOR enables fast,accurate LVL comparisons. • Comprehensive fill support, including fill back annotation to Milkyway, LEF/DEF, OpenAccess, OASIS, and GDSII design databases. • Pattern matching support. • Double patterning layout analysis support. 2.3.3 Benfits of calibre • Comprehensive, accurate, and proven signoff physical verification for advanced technology nodes and designs at all major foundries. • Industry-leading speed minimizes runtime and resource usage. • Enhanced DRC debugging provides the fastest results with the highest accuracy. • Extensive innovative and sophisticated capabilities support the most complex design requirements at every node. • Earliest rule deck availability for new process technologies supports fast production of leading edge designs. VEDA IIT Confidential Project Report (PR-I) 12 2.4 IC validator Tool : 2.4.1 About IC validator: Synopsys’ IC Validator physical verification is a comprehensive signoff solution improving productivity for customers at all process nodes from mature to advanced. The IC Validator tool offers the industry’s best distributed processing scalability to over 2000 CPU cores. The tool’s performance and scalability has enabled some of the industry’s largest reticle limit chips with billions of transistors, same day design rule checking (DRC), layout versus schematic (LVS), and dummy fill turnaround time. IC Validator physical verification is seamlessly integrated with Fusion Compiler RTL-to-GDSII solution and IC Compiler® II place and route system in the Fusion Design Platform.This integrated physical verification Fusion TechnologyTM accelerates design closure for manufacturing by enabling independent signoff-quality analysis and automatic repair within the implementation environment. IC Validator is architected for massively parallel distributed processing. IC Validator enables excellent scalability to 2000+ CPU cores.The built-in memory awareness keeps jobs within machine memory resource limits. IC Validator’s elastic CPU management adds and removes CPUs dynamically. Intelligent file management balances disk, memory and speed up multi-host environment. IC Validator is a cloud ready physical signoff solution. Its secure, scalable and certified by TSMC for signoff. IC Validator’s smart load sharing technology continuously monitors jobs and determines job health. Jobs that crash are restarted on other CPU cores. CPU cores can be added or removed on the fly allowing the job to smartly adjust according to job needs and farm constraints. Memory aware scheduling estimates memory requirements in advance and schedules jobs based upon hardware configurations allotted for any given run. This means that physical verification jobs always run as efficiently as possible even on highly restrictive and heavily loaded compute farms. This is essential considering hundreds or even thousands of CPUs are required for today’s modern chips. VEDA IIT Confidential Project Report (PR-I) 13 2.4.2 Features of IC validator • Explorer technology for 5X faster DRC verification during SoC integration. • Live DRC for signoff quality on-the-fly DRC checking within full custom ayout design tools. • Programmable Electrical Rule Checks (PERC) for customized checking for EOS/ESD/ERC rules. • Signoff certified at leading foundries with the broadest qualification and runset availability. 2.4.3 Benfits of IC validator • Industry leading physical verification performance enabled by distributed processing scalability past 2000 CPU cores. • Cloud-ready physical signoff, certified by TSMC. • Elastic CPU management adds and removes CPUs dynamically. • Physical Verification Fusion within place and route enabling automatic DRC repair, timing aware FILL, and engineering change order (ECO) capabilities. • LVS-aware simulation based short-finder. • Integration with StarRC parasitic extraction, Custom Compiler™ full- custom design environment, and other third-party layout tools for increased designer productivity. VEDA IIT Confidential Project Report (PR-I) 14 3. SCOPE OF PROJECT We are living in an age of ever accelerating digital innovation, where world-wide knowledge, commerce and communication are broadly accessible and literally at our fingertips. Over the past six decades, thousands of companies in the tech sector have worked diligently to bring new, ever-more sophisticated electronic innovations to market daily, culminating in today’s age of digitalization, which is rapidly changing how we live, travel, conduct business and communicate.This pace of digital transformation will accelerate even more rapidly as more companies begin to incorporate artificial intelligence (AI) and machine learning (ML) into their systems to leverage and even monetize the exponentially increasing amount of data produced by seemingly everything digital.EDA is dedicated to helping more companies advance in their digital transformation and engineer a smarter future faster. To achieve a better yield for a design we have do physical verification thoroughly. Removing DRC and LVS issues is major task for engineer manually. So, we need EDA tools to automate the work and reduction of manual effort and time in fixing the errors. In the market, few tools are available but we have to choose better one for our work to do it in efficient way. To fix DRC and LVS issues without degrading manufacturability with the help of EDA tools like calibre and IC validator tools. VEDA IIT Confidential Project Report (PR-I) 15 4. CONCLUSION Designs are getting larger and complex day by day, time for physical designs schedule continuing same or shorter. Verification is continuous process regarding flow automation because rule files are subject to change from time to time based on foundries. Runset might get confluence with the updated runset in order to obtain necessary adjustments based on automation of flow. As advancements observed in technology, older versions of EDA tools might not be useful and new features in tools need to cater latest problems in deep submicron technologies. Different EDA tools might be different from each other in flow automation. Hence new structure demand development in the flow from time to time. Fully automation in design and verification is still not practical in complex design constraints. The main objective is to avoid the delayed tape out. VEDA IIT Confidential Project Report (PR-I) 16 5. PLAN OF ACTION S.NO ACTION ITEM TARGET DATE 1 Literature Survey 24/02/2023 2 Stream out the GDS II of design 05/03/2023 3 Generation BEOL, FEOL and double patterning 10/03/2023 4 Detection and debugging of DRC and LVS errors with calibre 15/03/2023 5 Detection and debugging of DRC and LVS errors with IC validator 20/04/2023 6 Results and Conclusion 10/05/2023 7 Documentation 20/06/2023 Table 5.1: Plane of action VEDA IIT Confidential Project Report (PR-I) 17 6. REFERENCES [1]Synopsys’ IC Validator physical verification data sheet. https://www.synopsys.com/content/dam/synopsys/implementation&signoff/ datasheets/ic-validator-ds.pdf [2]Synopsys’ IC Validator Reference Manual Version N-2017.12-SP2. https://pdfcoffee.com/icvrefman-pdf-free.html [3]Calibre Verification User’s Manual. https://eda.sw.siemens.com/en-US/ic/calibre-design/userman.pdf [4]Calibre SVRF. https://eda.sw.siemens.com/en-US/ic/calibre-design/svrf.pdf [5]Calibre nmDRC datasheet https://trias-mikro.de/wp-content/uploads/2018/08/Datenblatt-Calibre-nmDRC.pdf [6]Digital transformation: How Siemens EDA helps you engineer a smarter future faster https://static.sw.cdn.siemens.com/siemens-disw-assets/public/ 5KI4T3DvwAcwY2MkwNXDHP/en-US/Siemens-SW-Digital-transformation-HowSiemens-EDA-helps-you-engineer-a-smarter-future-faster-83731-WP-C5.pdf [7]Vikram Gautam and Dr. Pawan Kumar Dahiya “IC DESIGN PHYSICAL VERIFICATION” in International Research Journal of Engineering and Technology (IRJET) Volume: 04 Issue: 06 | June -2017. https://www.irjet.net/archives/V4/i6/IRJET-V4I6244.pdf VEDA IIT Confidential Project Report (PR-I) 18 [8]R. M. C. Roberts and C. J. Fourie, “Layout-to-schematic as a step towards layout-versus-schematic verification of SFQ integrated circuit layouts,” in Proc. AFRICON, Pointe-Aux-Piments, Mauritius, 2013. https://ieeexplore.ieee.org/document/6757839 [9] LayoutEditor:Online at http://www.layouteditor.net/. [10] DRC and LVS information: Online at https://vlsi-backend-adventure.com/pd_verification.html VEDA IIT Confidential Project Report (PR-I) 19