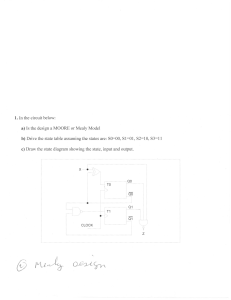

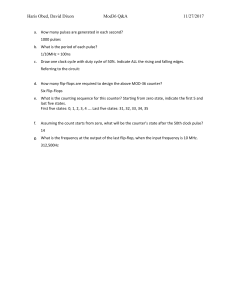

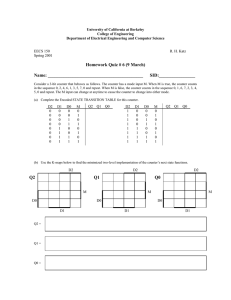

BCD COUNTER In digital and logical circuits, a sequential circuit called a counter is necessary to count the input pulses. The counter is designed by a group of flip-flops with an applied clock signal. A BCD counter is one of the types of most widely used digital counters, which counts up to 10 with an applied clock signal. It is a 4-bit binary digital counter, counts from 1 (0001) to 10 (1010). In practice, the BCD counter counts from 0000 (0) to 1001 (9) in decimal form on the application of the clock signal. These types of counting circuits are available in the form of integrated circuits like the 74LS90 asynchronous decade counter. This article gives an overview of the BCD counter or decade counter. What is a BCD Counter or Decade Counter? A BCD counter is one of the 4-bit binary counters, which counts from 0 to a predetermined count with an applied clock signal. When the count reaches the predetermined count value, it resets all the flip-flops and starts to count again from 0. This type of counter is designed by using 4 JK flip flops and counts from 0 to 9, and the result is represented in digital form. After reaching the count of 9 (1001), it resets and starts again. BCD or Decade Counter Circuit BCD or decade counter circuit is designed by using JK flip flops and NAND gate. The BCD counter design is very simple, and it requires 4 JK flip flops because it is a 4-bit binary counter. The design of the decade counter is shown below. BCD Counter Design From the figure, we observe that the outputs of J and K are connected to logic 1. The input pulses or clock input of each flip flop is fed as output to the next flip flop, but not the last flip flop. The CLR input is fed to the NAND gate output parallelly to reset all the flip flops when the count reaches. Decade Counter Operation At an initial stage (before operation), the count of the decade counter is 0000. When the clock signal is given as input, then the operation starts and counts the binary output. For the first clock pulse, the decade counter counts up to 9 ( 1001) and for the next clock input pulse, it is advanced to 10 (1010).The decade counter counts 0 to 9 for a given clock signal. When it reaches the count, it resets all the flip-flops and the cycle is repeated. When the inputs X1 and X3 of the NAND gate is high, the output will be low. If the output of the NAND gate is connected to the clear input, then it resets all the stages of flip flops of the decade counter. That means when the input pulse reaches the count from 0 to 9, then it stops counting and starts the count from 0 again. The Truth Table of Decade Counter The truth table of the decade counter is shown below. Input pulses/clock pulses 0 QD QC QB QA 0 0 0 0(resets) 0 0 0 1 0 0 0 1 0 0 1 1 2 3 1 0 4 5 6 7 8 0 1 0 0 1 0 0 1 1 0 1 1 1 0 0 1 0 1 0 1 9 1 0 0 It counts the decimal input pulses and displays the output in binary form. The output of the NAND gate is zero when the input pulse count reaches 9 (1001). The inputs X1 and X3 of the NAND gate decode the count to display the output in binary form. When the count reaches 9, it resets all the flip-flops by triggering the output of the NAND gate from 1 to 0. State Diagram of Decade Counter The state diagram of the decade counter is shown below. State Diagram The BCD counter or decade counter has 4 jk flip flops with 16 combinational states as shown in the figure above. Out of 16 states, 10 are used. When the counters are connected in series, we can count up to 100 or 1000 based on the application. The term Modulus is the total no of counts that a counter has a capacity of counting pulses. When a counter counts n- counts, it reaches zero, called modulus n-counter. Examples are mod-8 counter, mod-16 counter, etc. The counting range of the n-bit modulus binary counter is from 0 to 2n-1. Similarly, the BCD counter is a Mod-10 counter, which resets to zero after counting from 0(0000) to 9 (1001), represents the result in decimal form. (that means divide-by10 count). Hence, it is called a binary coded decimal counter (BCD Counter). It is an 8421 code (binary weight of 4 digits or bits), which consists of 4 binary digits and very easy to perform binary and decimal conversions. 74LS90 Decade Counter IC Description 74LS90 decade counter IC description and pin configuration is shown below. It is the most widely used 14-pin integrated chip. 74LS90 IC Pin Explanation Pin Configuration of BCD Counter Explanation The decade counter is a simple 4-bit binary counter with 4 outputs- QA, QB, QC, QD. Once the count reaches counting 10, then it resets all the flip-flops with a binary output 0(0000) each time and starts the counting cycle again. The reset pins R1, R2, R3, and R4 are used to set and reset the IC 7490. When the reset pins R1, R2 are high and R3, R4 are grounded, the output QA, QB, QC, QD is set to 0(0000) and resets the counter. When R3, R4 are high, then the output is set to 9(1001). The counting capability of the 74LS90 decade counter can be increased by connecting more no of ICs in series. It stores and represents the result in decimal form as shown in the above truth table. Applications of BCD Counters or Decade Counters The electronic circuit with a clock signal is known as a decade counter. It is a 4-bit binary input and output circuit. The applications of BCD counter or decade counter are as follows Clock circuits Frequency dividers Frequency counting circuits State machines Sequencers Clock division CMOS low power circuits Integrated oscillators Clock generation Used as inputs compatible with TTL etc Decade Counter in Frequency Counting Decade counters are the binary counters used in frequency counter design. The design of a decade counter using JK flip-flops is shown below. Decade Counter in Frequency Counting The purpose of the decade counter in frequency counting circuits is to find or count the frequency of the unknown signal. The frequency to be counted is fed to one input of the AND gate and the sample pulses are given to another input of the AND gate as shown in the figure above. The output of Frequency Counting At high sample pulses, the circuit is allowed to transfer the input to the counter. At low sample pulses, the input signal is transferred to the counter. The unknown frequency of the input signal is the ratio of no of counts given by the counter to the sample time interval. The JK flip-flop holds the output of the counter, where the third input of the AND gate is fed. When the input signal came from the JK flip-flop and the sample pulse is high, then the output is displayed by the counter. One-shot multivibrator sends a pulse to reset the counter after every high input signal (positive edge) of JK flip-flop. PRACTICE EXERCISE 220V TO 5V SYSTEM U1 7805 R1 VI VO 3 GND BR1 2 R1(1) 100k 1 BRIDGE C1 C2 C3+88.8 100u 1nF 1nF Volts