Creating Liberty Models for Custom and Mixed-Signal Blocks

(Virtuoso Liberate AMS Mixed-Signal Characterization Solution - GUI Interface)

Paul MOSinskis

Liberate Applications Engineer

Technology on Tour

Greensboro, NC – March 20, 2018

Boston, MA – March 22, 2018

Ottawa, Canada – March 27, 2018

Design Implementation Methodologies

Schematic on Top

(Analog on Top)

Typical MS design

Virtuoso ®

Netlist on Top

(Digital on Top)

Innovus ®

A

D

D

D

D

D

D

D

D

D

A

A

A

D

D

A

D

D

A

A

A

A

Virtuoso

Innovus

A

D

Virtuoso Implemented

Analog blocks

© 2018 Cadence Design Systems, Inc. All rights reserved.

A

D

D

A

A

D

D

D

A

D

2

D

A

A

D

D

A

D

A

A

D

A

A

Virtuoso Digital Implementation

Digital blocks

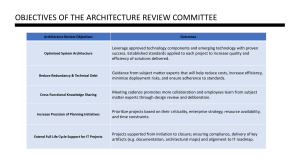

Cadence Characterization Technology Portfolio

Liberate

Virtuoso

Liberate™

Characterization

Solution

Virtuoso

Liberate LV Library

Validation Solution

Virtuoso

Variety™ Statistical

Characterization

Solution

Virtuoso

Liberate MX Memory

Characterization

Solution

Virtuoso

Liberate AMS MixedSignal Characterization

Solution

Standard Cells and

Complex I/Os

Library Validation

Process Variation

Modeling

Memory and

Custom Blocks

Mixed-Signal

Characterization

• Comprehensive

validation system

• Library function

equivalence and

data consistency

checking

• Revision analysis

• Timing and power

correlation

• Generates

libraries that can

be used by

multiple SSTA

tools

• Local and global

process variation

• AOCV/SOCV

tables, LVF

• Unique “dynamic

partitioning”

technology for

optimal runtime

• Timing constraints

and current

source models for

timing and noise

• “Hybrid

partitioning”

technology

• One step .lib

generation for

timing, power,

leakage and noise

• Ultra-fast library

characterization

• Advanced timing,

power, and noise

models

• CCS, ECSM,

NLDM, NLPM,

CCSN, ECSMN,

CCSP, ECSP

Inside View: Patented technology for generating and optimizing characterization stimulus

Spectre® API Integration: 2-3X improved throughput over command-line use model

3

© 2018 Cadence Design Systems, Inc. All rights reserved.

Liberate AMS Solution: GUI Flow

Liberate AMS Server

Auto Probing

Static Analysis

Topology Extraction

Boundary Modeling

Dynamic Analysis

Vector Generation

Power Characterization

Liberate AMS Clients

Block-level

power/leakage

Spectre APS/XPS

Timing Partitioning

Block-level

Spectre APS/XPS

Liberate AMS Clients

Partition-level timing

Spectre APS

.ldb

Model

Generation

.LIB

nldm, nlpm, ccs,

ccsn, ecsm

ecsmn

4

© 2018 Cadence Design Systems, Inc. All rights reserved.

Liberate AMS Solution – Typical Usage

Digital Interface

Tx

TxIN<*>

PLL

TxCK

Setup + Hold

Analog

Rx

RxOUT<*>

RxCK

Delay, RxCK to Q

RTL

5

© 2018 Cadence Design Systems, Inc. All rights reserved.

Custom Digital + Analog

Liberate AMS Solution - Preview

1. Identify clock nodes and probes

2. Perform a full-block single

simulation to identify arcs

RX

00000000000000000000000000000000000

11111111111111111111111111111111111

10101010101010101010101010101010101

00000000000000000000000000000000000

11111111111111111111111111111111111

10101010101010101010101010101010101

TX

00000000000000000000000000000000000

11111111111111111111111111111111111

10101010101010101010101010101010101

00000000000000000000000000000000000

11111111111111111111111111111111111

10101010101010101010101010101010101

DPLL

Digital

DPLL

6

© 2018 Cadence Design Systems, Inc. All rights reserved.

3. Create partitions

4. Characterize partitions

5. Create the library

library (ams) {

….

cell (serdes) {

….

bus (Q) {

bus_type : bus_serdes_Q_0_31;

direction : output;

pin (Q[0]) {

}

….

pin (Q[31]) {

}

timing () {

related_pin : "CLK";

timing_type : rising_edge;

cell_rise (delay_template_4x4) {

values ( \

"3.7446, 3.8261, 4.0435, 4.5617", \

….

);

}

…..

Decreasing Sim Time Dynamic Partitioning

• Run pre-simulation typically

using fast-spice or true spice

with lower accuracy

• For each arc extract the “worstcase” path

• Include active circuit, prune out

in-active devices

7

© 2018 Cadence Design Systems, Inc. All rights reserved.

Partition Sizes for MIPI I/O 13K xtrs

ARC TYPE

Max Xtrs

Delay

223

Constraint

165

Partition Accuracy

Library Data

Partition

Full Spice

%Diff

Delay (pS)

470.3

474.1

-0.81%

Setup (pS)

94.8

95.5

-0.74%

Hold (pS)

99.7

100.5

-0.80%

Circuit after Dynamic Partitioning

Decreasing Sim Type: Pin Cap and Noise Models

• Create a static boundary partition

consisting of the first level of Channel

Connected Components (transistors)

attached to each I/O port

– Typically <50 xtrs

• Characterize each boundary partition

separately for pin capacitance and noise

(ccsn/ecsmn)

• Integrate each boundary partition noise

and pin cap data back into the final model

8

© 2018 Cadence Design Systems, Inc. All rights reserved.

Pin Cap and SI Characterization

GUI Demo Goals

• GUI Pincap Flow – Quickly and easily generate .LIB file with

input capacitance from schematic

– Enable digital design while mixed-signal design continues

• GUI Characterization Flow - How to generate .LIB files for

multiple PVTs

– Configuration and setup from Virtuoso ADE Assembler

– Multi-threaded characterization of multiple corners

9

© 2018 Cadence Design Systems, Inc. All rights reserved.

GUI Demo

10

© 2018 Cadence Design Systems, Inc. All rights reserved.

Liberate AMS Solution - GUI Features

• Launched from within familiar Virtuoso environment

• Pincap Flow - Create shell libraries directly from schematic

• Characterization Flow - Generate .LIB files for multiple PVTs

• Site/project-wide variables

– So you can do common setups once

• Support for writing user attributes to library via user data library

file

– is_pll, dont_use, etc.

• Video available on support.cadence.com :

Creating Shell Libraries with Pin Capacitance using Liberate AMS GUI

11

© 2018 Cadence Design Systems, Inc. All rights reserved.

© 2018 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at www.cadence.com/go/trademarks are trademarks or registered trademarks of

Cadence Design Systems, Inc. All other trademarks are the property of their respective owners.

Additional Slides

13

© 2018 Cadence Design Systems, Inc. All rights reserved.

Pincap Flow Setup

Enter these values

From site/project-wide Setup

14

© 2018 Cadence Design Systems, Inc. All rights reserved.

Pincap Flow Setup

Check

15

© 2018 Cadence Design Systems, Inc. All rights reserved.

Adding Special Attributes and Bit Blasting Buses

Bit blasts buses

16

© 2018 Cadence Design Systems, Inc. All rights reserved.

Add special

attributes from

file