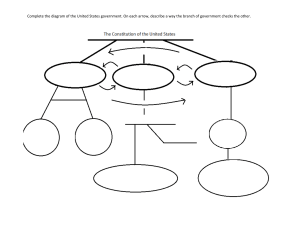

ASIC DESIGN FLOW ASIC DESIGN FLOW Design Specification Design Entry Functional Verification Sign Off Checks Tape Out Routing Physical Design CTS Placement Synthesis DFT Floor planning DESIGN SPECIFICATION • This is the stage at which the engineer defines features of the chip • Number of inputs and output pin • Number of clock signal to be used in the design • Maximum clock frequency to be used • Area of the chip • Operation voltage DESIGN ENTRY • RTL is know as for register transfer level • The designer start the design with a system specific language like VHDL , Verilog etc. • Example. AND gate Verilog code Module AND_2(output Y, input A, B); AND(Y, A, B); endmodule FUNCTIONAL VERIFICATION • Functional verification ensures that the design is logically correct and without major timing errors. • verification team write test-bench program for design. • RTL code and testbench are simulated using HDL simulators to check on functionality of the design. • Waveform is generated by the simulator to check the functional characteristics SYNTHESIS • • Converting Verilog /VHDL RTL program to gate level netlist. INPUT – 1) RTL Program 2) .lib File 3) .sdc File • • OUTPUT – Gate Level Netlist Following Steps In Synthesis 1]Translation- Converting RTL into simple logic gates. 2]Mapping - All cell will be mapped to cell present in .Lib file 3]Optimization – Optimize the design to meet timing constraints and to reduce power DFT • DFT Stand for Design For Testability • DFT is a technique, they will some addition design to become testable after production. • Its the extra logic which we put in the normal design, during the design process, which helps its post-production testing. PHYSICAL DESIGN Physical design is the process of turning a design into manufacturable geometries Input - .V file , . SDC file , .LIB/ .db file, .lef file, .view file etc. Output- GDS II Following Sub steps in Physical design 1) 2) 3) 4) Floor planning Placement CTS Routing FLOOR PLANNING • Floor planning is the process of placing blocks/macros in the core area. • Objective of floor planning are to minimize the area and delay. • Determine width and height of core and die. • Determine location of predefined cell/macros. • Determine I/O pin placement. • Creating the Pad Ring for the Chip. PLACEMENT • Placement is the process of placing standard cells in the design. • Objective of placement is to optimize the area, timing and power . • The placement should be routable. CTS • Clock Tree Synthesis (CTS) is a process which make sure that the clock signals distributed uniformly to all sequential elements in a design. • CTS is the process of insertion of buffers or inverters along the clock paths of design in order to achieve minimum skew. ROUTING • Routing is a process determines the precise paths for interconnections. • In routing stage, metal and vias are used to create the electrical connection • Objective of routing to meet the timing constraints, no LVS errors, no DRC errors and minimize the total wire length. SIGN OFF • These are some categories of signoff checks. 1)Physical Verification- DRC checks, LVS checks , ERC checks and Antenna rule checks etc. 2) Static timing analysis (STA) 3) IR Drop analysis 4) Electromigration checks TAPE OUT • Tape-out is the final phase of a IC design before the manufacturing starts. • This is the phase when the final database that contains the design information is sent to a foundry. • The data base will be in GDSII format.