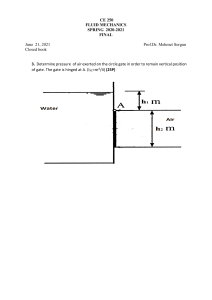

Author's personal copy Journal of Computational Electronics (2021) 20:209–217 https://doi.org/10.1007/s10825-020-01611-5 Performance enhancement of junctionless silicon nanotube FETs using gate and dielectric engineering S. Priscilla Scarlet1 · N. Vinodhkumar2 · R. Srinivasan3 Received: 3 June 2020 / Accepted: 21 October 2020 / Published online: 16 November 2020 © Springer Science+Business Media, LLC, part of Springer Nature 2020 Abstract The silicon nanotube field effect transistor (FET) is a tubular structure and has an inner gate and outer gate to control the channel. In this paper, the performance of a junctionless silicon nanotube FET is optimized using inner and outer gate engineering through 3D numerical TCAD simulations. The performance of the optimized devices is enhanced in terms of ON I current (ION), OFF current (IOFF), and I ON ratio. Appropriate work function and gate dielectric choices are suggested for the OFF inner and outer gates to obtain optimized devices. The lowest IOFF and highest I ON ratio are obtained for devices with high I OFF inner and outer gate permittivity along with low inner and outer gate work function. Also, the highest ION is obtained for the device with the highest inner and outer gate dielectric permittivity with low outer and inner gate work function. The device optimized for ION (98.6% increase compared to reference device) with the corresponding IOFF better than the reference device can be used for high-power applications. Keywords Junctionless · Silicon nanotube · Work function · Dielectric · FET 1 Introduction A number of important approaches have been introduced for tackling the issue of short channel effects (SCE), including (1) multi-gate structures, (2) junctionless (JL) devices, (3) gate dielectric engineering, and (4) gate electrode work function engineering [1–5]. Several multi-gate structures, such as fin field-effect transistors (FinFETs), tri-gate FETs, gate-all-around FETs, and nanowire FETs, have already been explored in the literature [6–10]. In the advanced form of the multi-gate structures, the silicon nanotube field effect transistor (SiNT-FET) was introduced in 2012 [11, 12]. In the SiNT-FET, the tubular channel is controlled by inner and outer gates. Since the inner gate provides additional charge control, the channel is more controllable in the SiNT-FET * S. Priscilla Scarlet lillypushpam5@gmail.com 1 Department of ECE, CVR College of Engineering, Hyderabad, India 2 Department of ECE, Vel Tech Rangarajan Dr. Sagunthala R&D Institute of Science and Technology, Chennai, India 3 Department of IT, SSN College of Engineering, Kalavakkam, India device compared to other multi-gate structures. The fabrication process steps for the tubular devices have been discussed in previous works [12–14]. Whereas in the multi-gate structures, control over the channel is achieved by increasing the number of gates, in junctionless devices, the source/drain-channel doping gradient is removed, thereby achieving better SCE performance [15, 16]. Junctionless devices are of interest to the device community because of both their reduced fabrication complexity and better SCE performance. Numerous junctionless operations on multi-gate structures have been investigated in the literature; for example, tri-gate, quadruple-gate, and nanowire structures have been reported [17–20]. Junctionless operations on a SiNT-FET structure, known as a JLSiNT-FET, is explored in [21–23]. Figure 1a shows the JLSiNTFET with both inner and outer gates, and Fig. 1b depicts the junctionless tubular channel alone, with the gate oxides removed for better visualization. SCE performance can also be improved through highK dielectric and appropriate gate electrode work function [24, 25]. The use of high-K dielectrics has been previously investigated in MOSFETs, FinFETs, and JL FETs [25–27], and work function engineering, i.e. the use of metal gates, has been similarly studied [28]. For the JLSiNT-FET, however, improving device performance through the use of 13 Vol.:(0123456789) Author's personal copy 210 Journal of Computational Electronics (2021) 20:209–217 Table 1 JLSiNT-FET device parameters S. no Parameters Dimensions 1 2 3 4 5 6 7 8 9 10 11 12 13 Gate length Tube wall thickness Tube outer diameter Tube inner diameter Oxide thickness Drain/source length Drain/source wall thickness Spacer length Doping concentration Inner gate electrode work function ­(WFIN) Outer gate electrode work function ­(WFOUT) Dielectric permittivity of inner gate (KIN) Dielectric permittivity of outer gate (KOUT) 45 nm 5 nm 32 nm 22 nm 1 nm 15 nm 15 nm 25 nm 1 × 1019 cm−3 4.68 eV 4.68 eV 3.9 F/m 3.9 F/m identical (case 2). A third case, referred to as the no-constraint case, is also investigated, where all possible combinations of inner and outer gate work functions along with inner and outer gate dielectric permittivity are used. All investigations are carried out using 3D technology computer-aided design (TCAD) simulations, in which the simulator is calibrated against the published results. The rest of the paper is organized as follows: The device structure of the JLSiNTFET and the models used for simulations are discussed in Sect. 2, with calibration details. Section 3 discusses the effect of the selected inner and outer gate dielectric permittivity combinations on the ON current (ION), OFF current I (IOFF), and I ON ratio, for case 1. Section 4 presents the effects OFF of inner and outer gate work function for case 2. Section 5 presents the effects for case 3 on the DC parameters. Finally, conclusions are given in Sect. 6. 2 Device structure and calibration Fig. 1 a JLSiNT-FET device structure, b silicon portion alone, c schematic vertical cross section, d circular cross section high-K dielectrics in the dielectric region and work function engineering in the inner and outer metal gates has yet to be explored. In this paper, we report the performance enhancement of a JLSiNT-FET through an appropriate choice of the inner and outer gate work function and dielectric permittivity. For the selection of gate work function, two types of constraint approaches are followed: (1) one in which the inner and outer gate work functions are identical (case 1), and (2) one in which the inner and outer gate dielectric permittivity are 13 Figure 1 shows the TCAD-generated JLSiNT-FET device with and without the gate region. The device is calibrated against published results [21] for its ION = 371 μA/μm and IOFF = 1.94 pA/μm for a channel length of 45 nm. The simulated structure has a gate length of 45 nm and a tube wall thickness of 5 nm. The other details are provided in Table 1. Various geometric parameters given in Table 1 are shown in the schematic vertical and circular cross sections in Fig. 1c, d. The TCAD-generated structure is used in the ID–VG (drain current versus gate voltage plot) device simulation to obtain its ION, IOFF, and VTH. As stated above, these parameters are calibrated by tuning the parameters used in the mobility models, namely the doping dependency on mobility, effect Author's personal copy Journal of Computational Electronics (2021) 20:209–217 211 of high and normal electric fields on mobility, and velocity saturation model [29]. The physics section of the sdevice includes these models. Simulations are also carried out using a drift–diffusion transport mechanism, charge carrier scattering, bandgap narrowing, and Schottky–Read–Hall mechanisms. The eQuantumPotential model is used to capture quantum effects such as quantization of inversion layer charge. Figure 2 shows the ID–VG characteristics of the calibrated JLSiNT-FET for a drain voltage of 1 V. A Sentaurus TCAD simulator (Synopsys, Inc.) is used for this study. 3 Effect of gate work function and dielectric permittivity with constraint of ­WFIN = WFOUT Fig. 3 IOFF versus work function (with ­WFIN = WFOUT) for various KOUT and KIN In this section, the impact of the inner and outer gate dielectric permittivity (KIN and KOUT) on the DC performance of the JLSiNT-FET device is investigated for various combinations of inner and outer gate dielectric materials, with ­WFIN = WFOUT. ­WFIN, ­WFOUT, KIN, and KOUT are described in Table 1. The DC parameters with respect to the OFF-state and ON-state profiles are analyzed. The OFF-state (VGS = 0 V and VDS = 1 V) profile is plotted in Fig. 3. Figure 3 shows IOFF versus gate work function with ­WFOUT = WFIN for various combinations of inner and outer gate dielectric materials. It can be observed that at a given inner and outer gate dielectric permittivity combination (with KIN = KOUT or KIN ≠ KOUT), as the gate work function increases, IOFF decreases. Also, the lowest leakage current is obtained at the highest work function and highest dielectric permittivity (i.e. W ­ FIN = WFOUT = 5.1 eV and ­K IN = K OUT = 25 F/m). We can understand this by studying the conduction band profile along the channel given in Figs. 4, 5, and 6. For any given inner and outer gate dielectric permittivity combination, as the gate work function increases from 4.3 to 5.1 eV, the potential barrier between the source and channel increases, as observed from Figs. 4, 5, and 6, thereby decreasing IOFF. Similar behavior in terms of the source–channel barrier height increase is observed for the increase in KIN from 3.9 to 25 for any W ­ FIN and ­WFOUT combination in the abovementioned figures. Also, from Figs. 4, 5, and 6, which are arranged in increasing order of KOUT, it can be observed that for any given KIN and gate work function combination, as KOUT increases, the source–channel barrier height increases. But the interesting behavior to note from Figs. 4, 5, and 6 is that the effect of each parameter, i.e. gate work function, KIN, and KOUT, on the source–channel barrier height is different. Fig. 2 Calibrated ID–VG characteristics of the JLSiNT-FET against published results [21] Fig. 4 Conduction band energy along the channel for KOUT = 3.9 F/m with different gate work functions and KIN 13 Author's personal copy 212 Fig. 5 Conduction band energy along the channel for KOUT = 7.5 F/m with different gate work functions and KIN Fig. 6 Conduction band energy along the channel for KOUT = 25 F/m with different gate work functions and KIN • The gate work function increase has the maximum impact on the source–channel barrier height compared to KIN or K,OUT as observed from Figs. 4, 5, and 6. This can be simultaneously confirmed from Fig. 3 in terms of leakage current as well. Also, as K OUT increases from 3.9 F/m (Fig. 4) to 25 F/m (Fig. 6), it can be observed that at any given work function, the spacing between the conduction bands for various KIN in the channel decreases. • I.e. the KOUT has a greater impact on IOFF compared to KIN. • Thus, in effect, the order of the parameters affecting IOFF to various extents is gate work function followed by KOUT and then KIN. 13 Journal of Computational Electronics (2021) 20:209–217 Fig. 7 Conduction band energy in the OFF state along the channel for KIN = 3.9 F/m and various KOUT and KOUT = 3.9 F/m and various KIN for ­WFIN = WFOUT = 4.3 eV Figure 7 depicts the conduction band energy along the channel in the OFF state for KIN = 3.9 F/m and various KOUT along with KOUT = 3.9 F/m for various KIN with ­WFIN = WFOUT = 4.3 eV. It can be observed from Fig. 7 that for a given KIN, as KOUT increases, the conduction band in the source region is constant, whereas that in the channel shifts upward. On the other hand, for a given KOUT, as KIN increases, the conduction band in both the source and channel regions shifts upward (see Fig. 7). This is because the inner gate covers the entire source, channel, and drain, and therefore its effect (in terms of KIN) is felt in all three regions. On the other hand, the outer gate covers only the channel region, and so its effect (in terms of KOUT) is felt in the channel region alone. Hence, the increase in the source–channel barrier during the OFF state with the increase in KOUT is greater than that with the increase in KIN. Thus, IOFF decreases at a higher rate with an increase in KOUT than with an increase in KIN. Figure 8 shows I ON versus gate work function with ­WFOUT = WFIN for various inner and outer gate dielectric materials. It can be observed from Fig. 8 that for a gate work function of 4.3 eV, 4.68 eV, or 4.9 eV, as KIN (with KOUT constant) or KOUT (with KIN constant) increases, ION increases. However, the rate at which ION increases with KIN (with KOUT constant) is higher than that of the increase with KOUT (with KIN constant). This is because the increase in eDensity with increased KIN is higher than with the increase in KOUT during the ON state, as shown in Fig. 9. The increase in ION with KOUT, keeping KIN = 3.9 F/m at a gate work function of 4.3 eV, is supported by the increase in eCurrentDensity for the same conditions in Fig. 10. Author's personal copy Journal of Computational Electronics (2021) 20:209–217 Fig. 8 ION versus work function (with W ­ FIN = WFOUT) for various KOUT and KIN Fig. 9 eDensity in the ON state versus work function (with ­WFIN = WFOUT) for various KOUT and KIN values 213 Fig. 11 eCurrentDensity in the ON state for various work functions with KOUT = KIN = 3.9 F/m On the other hand at a higher work function of 5.1 eV, as KIN (KOUT constant) or KOUT (KIN constant) increases, ION decreases. It can be observed from Fig. 8 that lower gate work function with higher dielectric permittivity w.r.t. both KIN and KOUT yields higher ON-state current. Also, at higher WF (i.e. at 5.1 eV), the impact of the inner and outer gate K value on ION is negligible. During the ON state, at a lower WF value (i.e. at 4.3 eV), the increase in inner or outer dielectric permittivity from 3.9 to 25 increases the electron density (see Fig. 9) in the channel, thereby increasing ION, as depicted in Fig. 8. Another observation inferred from Fig. 8 is that for any given KIN and KOUT combination as the gate work function increases ION decreases due to decrease in eDensity as shown in Fig. 9. This can be further evidenced from Fig. 11 clearly which shows the eCurrentDensity of the entire device in the ON state for KIN = KOUT = 3.9 F/m for 3 different gate work functions. From the analysis in this subsection it can be concluded that the lowest IOFF is obtained at the highest gate work function of 5.1 eV with the highest gate dielectric permittivity, i.e. KOUT = KIN = 25 F/m, resulting in IOFF = 3.1 × 10–21 A/µm and corresponding ION = 2.9 × 10–5 A/µm. For the same combination, the highest ION/IOFF ratio of 9.4 × 1015 is also obtained. On the other hand, the highest ION is obtained at the lowest gate work function of 4.3 eV and highest gate dielectric permittivity, i.e. KOUT = KIN = 25 F/m, resulting in ION = 1.9 × 10–3 A/ µm and corresponding IOFF = 9.8 × 10–5 A/µm. 4 Effect of gate work function and dielectric permittivity with constraint of KIN = KOUT Fig. 10 eCurrentDensity in the ON state for various KOUT with KIN = 3.9 F/m and ­WFIN = WFOUT = 4.3 eV In this section, the impact of the gate work function on ION and IOFF is studied under the constraint of KIN = KOUT. Figure 12 depicts the ION for various ­WFIN and ­WFOUT 13 Author's personal copy 214 combinations under the condition KIN = KOUT. It can be observed from Fig. 12 that for any given KIN = KOUT combination, as the ­WFIN or ­WFOUT increases, ION decreases. Similarly, for lower gate work function (­ WFIN or W ­ FOUT) ranges (4.3 eV to 4.9 eV), as KIN = KOUT increases, ION increases. On the other hand, for higher gate work function ­(WFIN or W ­ FOUT) range (5.1 eV), as KIN = KOUT increases, ­ION decreases. Table 2 lists the ION and IOFF for KIN = KOUT = 3.9 F/m, ­WFIN equal to a constant value (4.3 eV or 5.1 eV), and ­WFOUT varying from 4.3 to 5.1 eV, and the corresponding graph is drawn in Fig. 13. It can be observed from Fig. 13 that for W ­ FIN = 4.3 eV or ­WFIN = 5.1 eV, as ­WFOUT increases, ION decreases, but for ­WFIN = 4.3 eV, the graph is shifted up compared to W ­ FIN = 5.1 eV. Table 2 lists the slope of the ­ION curve obtained from the linear fit of the curves in Fig. 13. A sample of the linear fit of ION versus W ­ FOUT for ­WFIN = 5.1 eV is shown in the inset of Fig. 13. From the linear fit, the slope of the curves (i.e. rate of change of ION w.r.t. ­WFIN with ­WFOUT constant or rate of change of ION w.r.t. ­WFOUT with ­WFIN constant as per the case) is extracted and updated in Table 2. Also, Table 2 lists t he I ON and I OFF for K IN = K OUT = 3.9 F/m, ­W F IN equal to a constant value (4.3 eV or 5.1 eV), and ­WFOUT varying from 4.3 to 5.1 eV. It can be observed from Fig. 13 that for ­WFOUT = 4.3 eV or ­WFOUT = 5.1 eV, as ­WFIN increases, ION decreases, but for ­WFOUT = 4.3 eV, the graph is shifted up compared to ­WFOUT = 5.1 eV. Hence, from Table 2 and Fig. 13 we can conclude that the slope of the blue lines representing fixed ­WFOUT and varying ­WFIN is higher than that for the slope of the red lines representing fixed ­WFIN and varying ­WFOUT. In other words, ­WFIN provides a wider tuning range than ­WFOUT for ION with KIN = KOUT = 3.9 F/m. Fig. 12 ION versus ­ WFIN and W ­ FOUT (all combinations) for KIN = KOUT 13 Journal of Computational Electronics (2021) 20:209–217 Table 2 DC parameters for KIN = KOUT = 3.9 F/m S. no. WFIN (eV) WFOUT (eV) ION (A/um) IOFF (A/um) Slope for ION 1 2 3 4 5 6 7 8 5 6 7 8 5 6 7 8 4.3 4.68 4.9 5.1 4.3 4.68 4.9 5.1 4.3 7.54 × 10–4 5.94 × 10–4 4.77 × 10–4 3.68 × 10–4 2.59 × 10–4 1.77 × 10–4 1.11 × 10–4 5.58 × 10–5 7.54 × 10–4 5.04 × 10–4 3.72 × 10–4 2.59 × 10–4 3.68 × 10–4 1.80 × 10–4 1.05 × 10–4 5.58 × 10–5 4.3 5.1 4.3 4.68 4.9 5.1 4.3 4.68 4.9 5.1 5.1 2.60 × 10–6 1.72 × 10–9 2.96 × 10–11 8.99 × 10–13 2.90 × 10–11 3.50 × 10–15 1.74 × 10–17 1.81 × 10–19 2.60 × 10–6 1.35 × 10–8 6.26 × 10–10 2.90 × 10–11 2.90 × 10–11 3.50 × 10–15 1.74 × 10–17 1.81 × 10–19 − 4.81 × 10–4 − 2.54 × 10–4 − 6.21 × 10–4 − 3.96 × 10–4 Table 3 lists the ION and IOFF for KIN = KOUT = 25 F/m, ­WFIN equal to a constant value (4.3 eV or 5.1 eV), and ­WFOUT varying from 4.3 to 5.1 eV, and the corresponding graph is drawn in Fig. 14. It can be observed from Fig. 14 that for W ­ FIN = 4.3 eV or ­WFIN = 5.1 eV, as ­WFOUT increases, ION decreases. However, for W ­ FIN = 4.3 eV, the graph is shifted up compared to ­WFIN = 5.1 eV. Also, the curves in Fig. 14 have been linearly fitted and their corresponding slopes (i.e. rate of change of ION w.r.t. ­WFIN with ­WFOUT constant or rate of change of ION w.r.t. ­WFOUT with ­WFIN constant as per the case) are extracted and updated in Table 3. Fig. 13 ION versus ­WFIN and ­WFOUT for KIN = KOUT = 3.9 F/m. Inset: linear fit for ION versus ­WFOUT with ­WFIN = 5.1 eV (Color figure online) Author's personal copy Journal of Computational Electronics (2021) 20:209–217 215 Table 3 DC parameters for KIN = KOUT = 25 F/m S. no, WFIN (eV) WFOUT (eV) ION (A/um) IOFF (A/um) Slope for ION 1 2 3 4 5 6 7 8 5 6 7 8 5 6 7 8 4.3 4.68 4.9 5.1 4.3 4.68 4.9 5.1 4.3 1.88 × 10–3 1.56 × 10–3 1.39 × 10–3 1.27 × 10–3 1.97 × 10–4 1.59 × 10–4 9.63 × 10–5 2.91 × 10–5 1.88 × 10–3 9.13 × 10–4 4.67 × 10–4 1.97 × 10–4 1.27 × 10–3 4.44 × 10–4 1.32 × 10–4 2.91 × 10–5 4.3 5.1 4.3 4.68 4.9 5.1 4.3 4.68 4.9 5.1 5.1 9.78 × 10–8 3.99 × 10–10 8.89 × 10–11 3.15 × 10–11 1.22 × 10–14 2.03 × 10–16 4.77 × 10–19 3.10 × 10–21 9.78 × 10–8 4.43 × 10–10 2.47 × 10–12 1.22 × 10–14 3.15 × 10–11 1.21 × 10–16 2.50 × 10–19 3.10 × 10–21 − 7.71 × 10–4 − 2.06 × 10–4 Moreover, the slope for both the blue and red lines in Fig. 14 is higher than that in Fig. 13. In other words, with regard to the tuning range of ION with respect to ­WFIN and ­WFOUT, the tuning parameters are improved at higher KIN and KOUT (see Fig. 14) when compared to the tuning range at lower KIN and KOUT (see Fig. 13). In conclusion, the best tuning range for ION is provided by the gate with higher W ­ FIN, followed by ­WFOUT at a fixed KIN = KOUT. 5 Effect of gate work function and dielectric permittivity without constraint − 2.14 × 10–3 − 1.6 × 10–3 The combined effect of all possible combinations of inner and outer gate work functions (i.e. with W ­ FIN = WFOUT and ­WFIN ≠ WFOUT) and dielectric permittivity values (i.e. with KIN = KOUT and KIN ≠ KOUT) on ION and IOFF of the JLSiNTFET device is investigated in this section. The outcome of this is a design of experiments (DOE) of 144 devices in total [4 (for ­WFIN) × 4 (for ­WFOUT) × 3 (for KIN) × 3 (for KOUT)]. This analysis was performed to obtain a greater number of optimized devices with respect to both ION and IOFF. I Among these devices, the lowest IOFF and highest I ON ratio OFF Fig. 14 ION versus W ­ FIN and ­WFOUT for KIN = KOUT = 25 F/m (Color figure online) Therefore, from Table 3 and Fig. 14 we can conclude that the slope of the blue lines representing fixed W ­ FOUT and varying ­WFIN is higher than that for the slope of the red lines representing fixed W ­ FIN and varying W ­ FOUT. In other words, W ­ FIN provides a wider tuning range for ION compared to ­WFOUT with KIN = KOUT = 25 F/m. Table 4 Dielectric permittivity and gate work function of the junctionless nanotube FET with the lowest IOFF and highest ION are obtained for devices with high inner and outer gate permittivity along with the highest inner and outer gate work function, as shown in Table 4. Also, the highest ION is obtained for the device with the highest inner and outer gate dielectric permittivity and with the lowest outer and inner gate work function (Table 4). However, although ION or IOFF have been optimized, the corresponding IOFF or ION is degraded when compared to the reference device. Hence we need a set of devices which have been optimized with respect to both ION and IOFF. Table 5 presents a list of optimized devices among the 144 devices (3 × 3 × 4 × 4) whose performance was optimized w.r.t. ION or IOFF or both in comparison to the reference device, and with a better ION/IOFF ratio than the reference device. The device with the most optimized ON current and corresponding higher OFF current with respect to the reference device (for KOUT = KIN = 25 F/m and ­WFIN = WFOUT = 4.68 eV) has ION = 737 µA/µm. The device with the most optimized OFF current and ION/IOFF ratio with the corresponding better ON current than the reference device (for KOUT = KIN = 25 F/m, ­WFIN = 4.68 eV, and ­WFOUT = 5.1 eV) has IOFF = 0.12 fA/ µm. The outstanding switching performance of the optimized device makes it an attractive choice for future ultralow-power high-speed digital integrated circuits. S. no. KIN (F/m) KOUT (F/m) WFIN (eV) WFOUT (eV) ION (A/µm) IOFF (A/µm) 1 2 25 25 25 25 5.1 4.3 5.1 4.3 2.91 × 10–5 1.88 × 10–3 3.10 × 10–21 9.78 × 10–8 13 Author's personal copy 216 Journal of Computational Electronics (2021) 20:209–217 Table 5 DC parameters of the optimized junctionless silicon nanotube FETs for various gate work function and permittivity values S. no. KOUT (F/m) KIN (F/m) WFIN (F/m) WFOUT (F/m) ION (A/um) IOFF (A/um) ION/IOFF 1 2 3 4 5 6 7 8 9 10 11 13 14 15 16 17 18 19 3.9 3.9 3.9 3.9 3.9 3.9 3.9 7.5 7.5 7.5 7.5 7.5 7.5 25 25 25 25 25 3.9 7.5 7.5 7.5 25 25 25 3.9 7.5 7.5 25 25 25 3.9 3.9 7.5 7.5 25 4.68 4.3 4.68 4.68 4.68 4.68 4.68 4.68 4.68 4.68 4.68 4.68 4.68 4.3 4.68 4.3 4.68 4.68 4.68 5.4 4.68 4.9 4.68 4.9 5.1 4.68 4.68 4.9 4.68 4.9 5.1 4.9 4.68 5.1 4.68 4.68 3.71 × 10–4 5.70 × 10–4 4.63 × 10–4 3.74 × 10–4 6.23 × 10–4 5.56 × 10–4 4.87 × 10–4 4.14 × 10–4 5.12 × 10–4 3.75 × 10–4 6.76 × 10–4 5.62 × 10–4 4.69 × 10–4 4.30 × 10–4 4.47 × 10–4 6.18 × 10–4 5.62 × 10–4 7.37 × 10–4 20 21 25 25 25 25 4.68 4.68 4.9 5.1 5.57 × 10–4 9.15 × 10–16 4.44 × 10–4 1.21 × 10–16 22 25 25 4.9 4.68 3.75 × 10–4 1.81 × 10–15 Table 6 provides a performance comparison of the optimized device with other junctionless devices using work function engineering. It can be seen that the proposed device structure exhibits a significant improvement in the OFF current (IOFF) and ION/IOFF ratio against existing devices due to its better controllability. 6 Conclusion In the reference work [21], the inner and outer gates of the nanotube are electrically connected together, with their corresponding work functions and dielectric permittivities Table 6 Performance comparison of our optimized device with other reported junctionless devices Device structure LG (nm) VD (V) ION (A/µm) IOFF (A/µm) ION/IOFF 13 1.94 × 10–12 1.84 × 10–12 6.00 × 10–13 1.19 × 10–14 1.74 × 10–13 6.11 × 10–15 6.37 × 10–16 5.59 × 10–13 2.36 × 10–13 3.39 × 10–15 9.03 × 10–14 2.28 × 10–15 2.59 × 10–16 3.93 × 10–13 1.67 × 10–13 1.50 × 10–12 9.07 × 10–14 4.22 × 10–14 Comments 1.91 × 108 Reference device 3.10 × 108 7.72 × 108 3.14 × 1010 3.58 × 109 9.10 × 1010 7.65 × 1011 7.41 × 108 2.17 × 109 1.11 × 1011 7.49 × 109 2.46 × 1011 1.81 × 1012 1.09 × 109 2.68 × 109 4.12 × 108 6.20 × 109 1.75 × 1010 Device with highest ION with lower IOFF than the reference device 6.09 × 1011 3.67 × 1012 Device with lowest IOFF with slightly better ION than the reference device, thereby providing a good ION/IOFF ratio 2.07 × 1011 being equal. In our work, the inner and outer gates are made independent of each other in terms of work function and permittivity. This is done to optimize the device in terms of ION, IOFF, and ION/IOFF ratio. In general, the lowest IOFF is obtained at the highest gate work function (­ WFOUT = WFIN = 5.1 eV) with the highest gate dielectric permittivity (KOUT = KIN = 25 F/m), but the ION is poorer than that of the reference device [21]. Also, the highest ION is obtained at the lowest gate work function ­(WFOUT = WFIN = 4.3 eV) with the highest gate dielectric permittivity (KOUT = KIN = 25 F/m), but the IOFF is poorer than that of the reference device. Ref [5] Ref [6] This work DMG-DGJLT Bulk junctionless FET JLSiNT-FET Optimized JLSiNTFET 30 1.0 1.783 × 10–3 1.767 × 10–9 1.04 × 106 15 1.0 3.26 × 10–3 5.31 × 10–9 6.1 × 105 45 1.0 3.71 × 10–4 1.94 × 10–12 1.91 × 108 45 1.0 7.37 × 10–4 4.22 × 10–14 1.75 × 1010 Author's personal copy Journal of Computational Electronics (2021) 20:209–217 Hence we have enumerated a set of optimized devices with respect to both ION and IOFF with the corresponding ION or IOFF counterpart being better than the reference device. Among these, the device which is most optimized with respect to the ON current with better OFF current than the reference device (for K OUT = KIN = 25 F/m and ­WFIN = WFOUT = 4.68 eV) has ION = 737 µA/µm, which is a 98.6% increase, with the corresponding IOFF decreasing by 97.8%, both in comparison to the reference device. The device with the most optimized OFF current and ION/IOFF ratio and with ON current better than the reference device (for KOUT = KIN = 25 F/m, ­WFIN = 4.68 eV, and ­WFOUT = 5.1 eV) has IOFF = 0.12 fA/µm, which is an almost 99.9% decrease, with the corresponding ION increasing by 19.7%, compared to the reference device. This improved performance of the proposed device makes it one of the most promising candidates for future ultralow-power digital integrated circuits. References 1. Colinge, J.P.: Finfets and Other Multigate Transistors. Springer, Berlin (2007) 2. Ferain, I., Colinge, C.A., Colinge, J.P.: Multigate transistors as the future of classical metal-oxide-semiconductor field-effect transistors. Nature 479(7373), 310–316 (2011) 3. Hisamoto, D., et al.: FinFET-A self-aligned double-gate MOSFET scalable to 20 nm. IEEE Trans. Electron Devices 47(12), 2320–2325 (2000) 4. Manoj, C.R., Nagpal, M., Varghese, D., Rao, V.R.: Device design and optimization considerations for bulk FinFETs’. IEEE Trans. Electron Devices 55(2), 609–615 (2008) 5. Wang, Y., Shan, C., Dou, Z., Wang, L.-G., Cao, F.: Improved performance of nanoscale junctionless transistor based on gate engineering approach. Microelectron. Reliab. 55, 318–325 (2015) 6. Scarlet, S.P.R., Srinivasan: Optimization of nanometer bulk junctionless Trigate FET using gate and isolation dielectric engineering. Mater. Sci. Semicond. Process. 84, 107–114 (2018) 7. Sun, X., Liu, T.J.K.: Scale-length assessment of the trigate bulk MOSFET design. IEEE Trans. Electron Devices 56(11), 2840– 2842 (2009) 8. Sun, X., Moroz, V., Damrongplasit, N., Shin, C., Liu, T.J.K.: Variation study of the planar ground-plane bulk MOSFET, SOI FinFET, and trigate bulk MOSFET designs. IEEE Trans. Electron Devices 58(10), 3294–3299 (2011) 9. Bangsaruntip, S., Cohen, G.M., Majumdar, A., Zhang, Y., Engelmann, S.U., Fuller, N.C.M., Sleight, J.W.: High performance and highly uniform gate-all-around silicon nanowire MOSFETs with wire size dependent scaling. In: Technical Digest—International Electron Devices Meeting, IEDM, pp. 297–300 (2009) 10. Song, J.Y., Choi, W.Y., Park, J.H., Lee, J.D., Park, B.G.: Design optimization of gate-all-around (GAA) MOSFETs. IEEE Trans. Nanotechnol. 5(3), 186–190 (2006) 11. Tekleab, D.: Device performance of silicon nanotube field effect transistor. IEEE Electron Device Lett. 35(5), 506–508 (2014) 12. Tekleab, D., Tran, H.H., Slight, J.W., Sleight, J.W.: Dureseti hidambarrao, Silicon nanotube MOSFET, U.S. Patent 0 217 468, August 2012 217 13. Jain, A.K., Sahay, S., Kumar, M.J.: Controlling L-BTBT in emerging nanotube FETs using dual-material gate. IEEE J. Electron Dev. Soc. 6, 611–621 (2018) 14. Gedam, A., Acharya, B., Mishra, G.P.: Junctionless silicon nanotube TFET for improved DC and radio frequency performance. Silicon (2020). https://doi.org/10.1007/s12633-020-00410-8 15. Colinge, J.P., Kranti, A., Yan, R., Lee, C.W., Ferain, I., Yu, R., Razavi, P.: Junctionless nanowire transistor (JNT): properties and design guidelines. Solid State Electron. 65–66(1), 33–37 (2011) 16. Gundapaneni, S., Ganguly, S., Kottantharayil, A.: Bulk planar junctionless transistor (BPJLT): an attractive device alternative for scaling. IEEE Electron Device Lett. 32(3), 261–263 (2011) 17. Scarlet, P., Nagarajan, K.K., Srinivasan, R.: Optimization of doping profile and isolation oxide thickness in bulk FinFETs using TCAD simulations. In: 2013 International Conference on Circuits, Power and Computing Technologies (ICCPCT), Nagercoil, pp. 959–965 (2013) 18. He, L., Chiang, T., Liou, J.J.: A new analytical subthreshold potential/current model for quadruple-gate junctionless MOSFETs. IEEE Trans. Electron Devices 61(6), 1972–1978 (2014) 19. Colinge, J.-P., Lee, C.-W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Murphy, R.: Nanowire transistors without junctions. Nat. Nanotechnol. 5(3), 225–229 (2010) 20. Scarlet, S.P., Ambika, R., Srinivasan, R.: Effect of eccentricity on junction and junctionless based silicon nanowire and silicon nanotube FETs. Superlattices Microstruct. 107, 178–188 (2017) 21. Ambika, R., Srinivasan, R.: Performance analysis of n-type junctionless silicon nanotube field effect transistor. J. Nanoelectron. Optoelectron. 11(3), 290–296 (2016) 22. Sahay, S., Kumar, M.J.: Nanotube junctionless FET: proposal, design, and investigation. IEEE Trans. Electron Devices 64(4), 1851–1856 (2017) 23. Singh, A., Pandey, C.K., Chaudhury, S. et al.: Tuning of threshold voltage in silicon nano-tube FET using halo doping and its impact on analog/RF performances. In Silicon, September (2020) 24. Singh, A., Chaudhury, S., Kumar Pandey, C., Madhulika Sharma, S., Kumar Sarkar, C.: Design and analysis of high k silicon nanotube tunnel FET device. IET Circuits Devices Syst. 13(8), 1305– 1310 (2019) 25. Yeo, Y.C., Ranade, P., King, T.J., Hu, C.: Effects of high-k gate dielectric materials on metal and silicon gate workfunctions. IEEE Electron Device Lett. 23(6), 342–344 (2002) 26. Wu, C.C., Lin, D.W., Keshavarzi, A., Huang, C.H., Chan, C.T., Tseng, C.H., et al.: High performance 22/20 nm FinFET CMOS devices with advanced high-K/metal gate scheme. In: Technical Digest—International Electron Devices Meeting, IEDM, pp. 27.1.1–27.1.4 (2010) 27. Pravin, J.C., Prajoon, P., Nesamania, F.P., Srikesh, G., Senthil Kumar, P., Nirmal, D.: Nanoscale high-k dielectrics for junctionless nanowire transistor for drain current analysis. J. Electron. Mater. 47, 2679–2686 (2018) 28. Cheng, B., Cao, M., Rao, R., Inani, A., Vande Voorde, P., Greene, W.M., Woo, J.C.S.: The impact of high-κ gate dielectrics and metal gate electrodes on sub-100 nm MOSFETs. IEEE Trans. Electron Devices 46(7), 1537–1544 (1999) 29. Synopsis Sentaurus Device Simulator, www.synopsys.com Publisher’s Note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations. 13