Problem Solutions – Chapter 1

CHAPTER 1

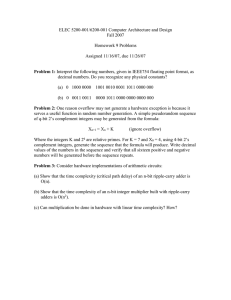

1-1.

39

2

© 2016 Pearson Education, Inc.

(a)

(1) Calm:

68

or

05

(2) 10 mph

:

69

(3) 100 mph

料

群

(b) The microcomputer requires a table or equation for converting from rotations/second to miles/hour. The pulses produced

by the rotating disk must be counted over a known period of time, and the table or equation used to convert the binary count

to miles per hour.

资

1-2.

–34° quantizes to –30° => 1 V => 0001

+31° quantizes to +30° => 7 V => 0111

试

+77° quantizes to +80° => 12 V => 1100

考

+108° quantizes to +110° => 15 V => 1111

1-3.*

17

18

19

20

大

Bin

16

21

22

23

24

25

26

27

28

29

1 0000 1 0001 1 0010 1 0011 1 0100 1 0101 1 0110 1 0111 1 1000 1 1001 1 1010 1 1011 1 1100 1 1101

20

21

22

Hex

10

11

12

23

13

湖

Oct

14

30

31

1 1110

1 1111

25

26

27

30

31

32

33

34

35

36

37

15

16

17

18

19

1A

1B

1C

1D

1E

1F

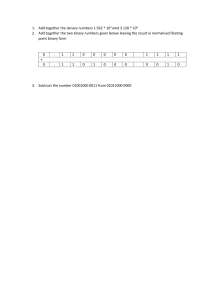

128K 128 210 131,072 Bits

32M 32 220 33,554,432 Bits

8G 8 230 8,589,934,592 Bits

欢

迎

加

入

1-4.

24

南

Dec

学

Decimal, Binary, Octal and Hexadecimal Numbers from (16)10 to (31)10

1

Problem Solutions – Chapter 1

1-5.

39

2

220 = (1,000,00010 + d) where d = 48,576

1Tb = 240 = (220)2 = (1,000,000 + d)2

= (1,000,000)2 + 2(1,000,000) d + d2

97,152,000,000

+

2,359,627,776

68

= 1,000,000,000,000

+

05

= 1,099,511,627,776

:

69

1-6.

11 1 Bits 211 1 2047

群

25 1 Bits 225 1 33, 554, 431

(1001101) 2 26 23 22 20 77

料

1-7.*

(1010011.101) 2 26 24 21 20 21 23 83.625

资

(10101110.1001) 2 27 25 23 22 21 21 24 174.5625

10111011

学

考

1

1

0

1

1

1

0

1

2|2014

2|1007

2|503

2|251

2|125

2|62

2|31

2|15

2|7

2|3

2|1

0

0

1

1

1

1

0

1

1

1

1

1

11111011110

欢

迎

加

入

湖

南

大

2|187

2| 93

2| 46

2| 23

2| 11

2| 5

2| 2

2|1

0

试

1-8.

2

2|891

2|445

2|222

2|111

2|55

2|17

2|13

2|6

2|3

2|1

0

1

1

0

1

1

1

1

0

1

1

2|20486

2|10243

2|5121

2|2560

2|1280

2|640

2|320

2|160

2|80

2|40

2|20

2|10

2|5

2|2

2|1

0

1101111011

0

1

1

0

0

0

0

0

0

0

0

0

1

0

1

101 0000 0000 0110

Problem Solutions – Chapter 1

39

2

1-9.*

Binary

Octal

Hexadecimal

369.3125

101110001.0101

561.24

171.5

189.625

10111101.101

275.5

BD.A

214.625

11010110.101

326.5

62407.625

1111001111000111.101

171707.5

68

Decimal

D6.A

05

F3C7.A

:

69

1-10.*

a)

0.45 × 8 = 3.6 =>

0.60 × 8 = 4.8 =>

0.80 × 8 = 6.4 =>

0.20 × 8 = 3.2 =>

(1938.257)10 = (792.41CB)16

(175.175)10 = (10101111.001011)2

(673.6)8

=

(110 111 011.110)2

考

a)

试

1-11.*

b)

(E7C.B)16

=

(1110 0111 1100.1011)2

=

(7174.54)8

(310.2)4

大

c)

南

=

(11 01 00.10)2

=

(64.4)8

1010

b)

×1100

0110

×1001

0000

0110

0000

0000

1010

0000

1010

0110

1111000

0110110

c)

1111001

×011101

1111001

000000

1111001

1111001

1111001

0000000

迎

加

入

湖

a)

(1BB.C)16

学

=

1-12.

3463

资

c)

3

4

6

3

料

b)

群

8|7562 2

16612

8|945 1

8|118 6

8|14 6

8|1 1

0

(7562.45)10 = (16612.3463)8

欢

110110110101

3

Problem Solutions – Chapter 1

10001

101 1010110

101

000

000

001

000

011

000

110

101

1

39

2

1-13.+

Quotient = 10001

群

:

69

05

68

Remainder = 1

1-14.

6 × 123 + 8 × 122 + 7 × 121 + 4 = 11608

12|7569 9

446912

12|630 6

12|52 4

12|4 4

0

试

资

料

(a)

(b)

0

1

A

B

2

3

4

5

6

7

8

9

C

D

E

F

G

H

I

J

学

a)

考

1-15.

大

b)

20|2007 7

20|100 0

20|5 5

0

50720

南

c) ( BCI .G)20 11 202 12 201 18 200 16 201 (4658.8)10

欢

迎

加

入

湖

1-16.*

a)

(BEE)r = (2699)10

11 r 2 14 r1 14 r 0 2699

11 r 2 14 r 2685 0

By the quadratic equation: r = 15 or ≈ –16.27

ANSWER: r = 15

b)

(365)r = (194)10

3 r 2 6 r1 5 r 0 194

3 r 2 6 r 189 0

By the quadratic equation: r = – 9 or 7

ANSWER: r = 7

4

Problem Solutions – Chapter 1

39

2

1-17.

Errata: The text has an error: 1480 should be 1460. This will be corrected in future printings.

Noting the order of operations, first add (34)r and (24)r

(24) r 2 r1 4 r 0

(34) r (24) r 5 r1 8 r 0

Now, multiply the result by (21)r

Next, set the result equal to (1480)r and reorganize.

10 r 2 21 r1 8 1 r 3 4 r 2 6 r1

1 r 3 6 r 2 15 r1 8 r 0 0

群

Finally, find the roots of this cubic polynomial.

:

69

(2 r1 1 r 0 ) (5 r1 8 r 0 ) 10 r 2 21 r1 8

Solutions are: r = 8, – 1, – 1

资

料

ANSWER: The chicken has 4 toes on each foot (half of 8).

试

1-18.*

考

a) (0100 1000 0110 0111)BCD

学

b) (0011 0111 1000.0111 0101)BCD

南

大

1-19.*

(4867)10

=

(1001100000011)2

=

(378.75)10

=

(101111010.11)2

(694)10

=

(0110 1001 0100)BCD

(835)10

=

(1000 0011 0101)BCD

湖

1

0001

1001

0100

+1000

+0011

+0101

1111

1100

1001

+0110

+0110

+0000

0101

1 0010

1001

欢

迎

加

入

=

0110

5

05

68

(34) r 3 r1 4 r 0

Problem Solutions – Chapter 1

101 100

0111 1000

011 1100

−0011

011 1001

−0011

01 1001

0 1100

−0011

0 1001

0100

010

01

0

Move R

Subtract 3

Move R

Move R

Move R

Move R

Move R

Subtract 3

大

料

考

学

Move R

Move R

Move R

试

0

Move R

Move R

Move R

Subtract 3

1-21.

欢

迎

加

入

湖

南

(a)

1st Move L

2nd Move L

3rd Move L

Add 3

4th Move L

Add 3

5th Move L

6th Move L

Add 3

7th Move L

(b)

102

101

100 column > 0111

110

1110

01110

001110

1001110 Leftmost 1 in BCD number

shifted out: Finished

资

00

0

Move R

Subtract 3

110

101

100

1001

0111

1100

1011

−0011 -0011

1001 1000

1100 1100

−0011 −0011

1001 1001

0100 1100

−0011

0100 1001

0010 0100

001 0010

00

1001

−0011

00 0110

0 0011

0001

000

001

00

Move R

Subtract 3

0

1

101 and 100 columns > 0111

1

01

101 and 100 columns > 0111

01

101

100 column > 0111

群

102

0011

001

(b)

100 column > 0111

68

Subtract 3

0

05

Move R

Subtract 3

:

69

(a)

39

2

1-20.*

1101

01101

001101 100 column > 0111

001101

0001101

10001101

110001101 Leftmost 1 in BCD

number shifted out: Finished

100

1111000

1 111000

11 11000

111 1000

100 column > 100

0011

1010 1000

100 column > 100

1 0101 000

0011

1 1000 000

11 0000 00

110 00000 101 column > 100

0011

1001 0000 0

1 0001 00000 Least significant bit in binary number moved in:Finished

103

102

101

1st Move L

2nd Move L

3rd Move L

4th Move L

Add 3

100

0

01

011

0111

0011

6

01110010111

1110010111

110010111

10010111

0010111

100 column > 100

Problem Solutions – Chapter 1

10th Move L

Add 3

11th Move L

10 0010

100 0101

0011

100 1000

1001 0001

10111

0111

101 & 100 columns > 100

0111

111

11

100 column > 100

11

1

101 &100 columns > 100

39

2

100 column > 100

68

8th Move L

9th Move L

Add 3

10

101

0011

1000

1 0001

10 0010

0010111

010111

10111

05

7th Move L

Add 3

1010

0100

1000

0011

1011

0111

0011

1010

0100

1001

0011

1100

1001

0011

1100

1001

1

10

1

Least significant bit in binary number moved in: Finished

:

69

5th Move L

6th Move L

Add 3

1-22.

群

From Table 1-5, complementing the bit B6 will switch an uppercase letter to a lower case letter and vice versa.

1-23.

0101

0101

0010

0100

0100

资

B

N

M

L

V

A

0100

0010

0010

0100

0100

0101

0000

0000

0100

1110

1101

0010

1100

0101

1110

1101

0100

1010

0000

0100

1101

0010

1110

1010

0000

1100

1100

1100

0101

0100

0100

0101

0110

1100

1001

0100

1110

0100

0001

考

0010

大

湖

入

加

迎

欢

R

T

.

E

I

0100

1000111

G

1101111

o

南

1-24.

0010

0100

1110

0101

1001

0100

学

b)

0010

1110

1101

1100

0110

0001

试

0100

0100

0100

0100

0101

0100

料

a) The name used is Brent M. Ledvina. An alternative answer: use both upper and lower case letters.

E

(SP)

(SP)

D

N

0100000

1000011

C

1100001

a

1110010

r

1100100

d

1101001

i

1101110

n

1100001

a (Errata: This number appears as 110001, which would be “1”)

1101100

l

1110011

s

0100001

!

7

Problem Solutions – Chapter 1

a)

(11111111)2

b)

(0010 0101 0101)BCD

39

2

1-25.*

011 0010

011 0101

011 0101ASCII

d)

0011 0010

1011 0101

1011 0101ASCII with Odd Parity

05

68

c)

a)

U+0040 = 01000000

b)

U+00A2 = 11000010 10100010

c)

U+20AC = 11100010 10000010 10101100

d)

U+1F6B2 = 11110000

群

10011111 10011010 10110010

Binary Numbers from (32)10 to (47)10 with Odd and Even Parity

32

33

34

35

(a) Odd

100000 0

100001 1

100010 1

(b) Even

100000 1

100001 0

100010 0

42

101001 0

101010 0

(b) Even

101000 0

101001 1

101010 1

38

39

100011 0

100100 1

100101 0

100110 0

100111 1

100011 1

100100 0

100101 1

100110 1

100111 0

43

44

45

46

47

101011 1

101100 0

101101 1

101110 1

101111 0

101011 0

101100 1

101101 0

101110 0

101111 1

试

41

101000 1

37

学

考

40

(a) Odd

36

资

Decimal

料

1-27.

Decimal

:

69

1-26.

大

1-28.

Gray Code for Hexadecimal Digits

1

2

0001

0011

迎

加

入

1-29.

欢

3

4

南

0

0000

0010

湖

Hex

Gray

0110

5

6

7

8

9

A

B

C

D

E

F

0111

0101

0100

1100

1101

1111

1110

1010

1011

1001

1000

(a) Wind Direction Gray Code

Direction

Code Word

N

000

S

110

E

011

W

101

NW

100

NE

001

SW

111

SE

010

8

Problem Solutions – Chapter 1

000

NE

001

E

011

SE

010

S

110

SW

111

W

101

NW

100

68

N

05

Code Word

:

69

Direction

39

2

(b) Wind Direction Gray Code (directions in adjacent order)

As the wind direction changes, the codes change in the order of the rows of this table, assuming that the bottom row is “next

to” the top row. From the table, the codes that result due to a wind direction change always change in a single bit.

群

1-30.+

The percentage of power consumed by the Gray code counter compared to a binary code counter equals:

料

Number of bit changes using Gray code

Number of bit changes using binary code

资

As shown in Table 1-6, and by definition, the number of bit changes per cycle of an n-bit Gray code counter is 1 per count =

2n.

试

Number of bit changes using Gray code = 2n

考

For a binary counter, notice that the least significant bit changes on every increment. The second least significant bit

changes on every other increment. The third digit changes on every fourth increment of the counter, and so on. As shown

in Table 1-6, the most significant digit changes twice per cycle of the binary counter.

Number of bit changes using binary code 2n 2n1

学

n

n

2i 2i 1 (2( n 1) 1) 1 2n 1 2

i 1

i 0

2

2n

( n1)

2

100

欢

迎

加

入

湖

南

大

% Power

9

21

Problem Solutions – Chapter 2

CHAPTER 2

39

2

© 2016 Pearson Education, Inc.

2-1.*

b)

Y

Z

XYZ

XYZ

X Y Z

0

0

0

0

1

1

0

0

1

0

1

1

0

1

0

0

1

1

0

1

1

0

1

1

1

0

0

0

1

1

1

0

1

0

1

1

1

1

0

0

1

1

1

1

1

1

0

0

:

69

05

X

X YZ ( X Y ) ( X Z )

Y

Z

YZ

X + YZ

X+Y

0

0

0

0

0

0

0

0

1

0

0

0

1

0

0

0

0

1

1

1

1

1

0

0

0

1

1

0

1

0

1

1

0

0

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

学

考

资

0

0

YZ

XZ

XY YZ XZ

0

0

0

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

0

1

1

0

0

1

0

0

1

1

0

0

0

0

0

1

0

1

0

0

1

1

湖

南

0

YZ

0

0

0

0

1

1

1

0

0

1

0

1

0

1

0

1

1

0

0

1

1

0

0

0

1

1

0

1

0

1

1

1

0

0

0

0

0

0

0

0

入

加

迎

欢

1

1

XY

XY

1

0

XY YZ XZ

Z

1

0

XZ

Y

1

0

XY YZ XZ XY YZ XZ

X

1

(X + Y)(X + Z)

大

c)

X+Z

试

X

料

The Second Distributive Law

2-2.*

68

XYZ X Y Z

Verification of DeMorgan’s Theorem

群

a)

a)

X Y XY XY

=

( X Y X Y ) ( XY XY )

X (Y Y ) Y ( X X )

X Y

1

X Y

b)

AB BC AB BC

=

1

=

X Y Z

=

:

69

Problem Solutions – Chapter 2

( AB AB) ( BC BC )

39

2

B( A A) B (C C )

B B 1

c)

Y XZ XY

68

Y XY XZ

(Y X )(Y Y ) XZ

05

Y X XZ

Y ( X X )( X Z )

X Y Z

d)

XY Y Z XZ XY YZ

XY YZ ( X X ) XZ XY YZ

XY XYZ XYZ XZ XY YZ

群

XY (1 Z ) XYZ XZ XY YZ

XY XZ (1 Y ) XY YZ

XY XZ (1 Y ) YZ

ABC BCD BC CD

=

B CD

考

a)

试

2-3.+

资

XY XZ YZ

料

XY XZ XY ( Z Z ) YZ

XY XZ XYZ YZ (1 X )

X Y XZ YZ

ABC ABC BC BCD BCD CD

学

AB(C C ) BC ( D D) BC CD

AB BC BC CD

大

B AB CD

B CD

欢

迎

加

入

湖

南

b)

WY WYZ WXZ WXY

=

WY WXZ XYZ XYZ

(WY WXYZ ) (WXYZ WXYZ ) (WXYZ WXYZ ) (WXYZ WXY Z )

(WY WXYZ ) (WXYZ WXY Z ) (WXYZ WXYZ ) (WXYZ WXYZ )

WY WXZ (Y Y ) XYZ (W W ) XYZ (W W )

WY WXZ XYZ XYZ

c)

AD AB CD BC

=

( A B C D)( A B C D)

AD AB CD BC

( A D)( A B )(C D)( B C )

( AB AD BD)( BC BD CD)

ABCD ABCD

( A B C D)( A B C D ) ( A B C D )( A B C D )

2

Problem Solutions – Chapter 2

Given:

A B 0, A B 1

Prove:

( A C)( A B)( B C)

=

AB AC BC

05

0 C ( A B)

C ( A B )(0)

C ( A B )( A B )

:

69

C ( AB AB B

BC

2-5.+

(A3, A2, A1, A0)

B

=

(B3, B2, B1, B0)

C

=

(C3, C2, C1, C0)

Define OR1, AND1 and NOT1 so that they conform to the definitions of AND, OR and NOT

presented in Table 2-1.

资

Step 2:

=

群

Define all elements of the algebra as four bit vectors such as A, B and C:

A

料

Step 1:

A + B = C is defined such that for all i, i = 0, ... ,3, Ci equals the OR1 of Ai and Bi.

b)

A B = C is defined such that for all i, i = 0, ... ,3, Ci equals the AND1 of Ai and Bi.

c)

The element 0 is defined such that for A = “0”, for all i, i = 0, ... ,3, Ai equals logical 0.

d)

The element 1 is defined such that for A = “1”, for all i, i = 0, ... ,3, Ai equals logical 1.

e)

For any element A, A is defined such that for all i, i = 0, ... ,3, Ai equals the NOT1 of Ai.

AC ABC BC AC ABC ( ABC BC)

大

a)

学

考

试

a)

2-6.

AC ( ABC ABC BC

南

( AC AC ) BC A BC

迎

加

入

湖

b)

欢

BC

68

( AB AC BC )( B C )

39

2

2-4.+

( A B C )( ABC )

AABC ABBC ABCC

( AA) BC A( BB )C AB (CC )

ABC ABC ABC ABC

c)

ABC AC A( BC C ) A( B C )

d)

ABD ACD BD

( AB B AC ) D

( A AC B) D

( A B) D

e)

( A B)( A C )( ABC )

AAABC ACABC BAABC BCABC

ABC

3

Problem Solutions – Chapter 2

2-7.*

( X Y )( X Z ) X YZ

X Y ( Z X Z ) X Y ( Z XZ ) X Y (Z X )(Z Z ) X YZ XY

b)

WX ( Z YZ ) X (W WYZ ) WXZ WXYZ WX WXYZ

c)

WXZ WXZ WX WX WX X

68

( X X )( X Y ) YZ X Y YZ X Y

39

2

XY XYZ XY X XYZ ( X XY )( X Z ) ( X X )( X Y )( X Z )

a)

05

( AB AB)(CD CD) AC ABCD ABCD ABCD ABCD A C

d)

:

69

ABCD A C A C A( BCD) A C C ( BD) A C BD

2-8.

F ABC AC AB

a)

F ABC AC AB

b)

料

群

( A B C ) ( A C ) ( A B)

c) Same as part b.

资

2-9.*

F ( A B)( A B)

b)

F ((V W ) X Y )Z

c)

F [W X (Y Z )(Y Z )][W X YZ YZ ]

d)

F ABC ( A B)C A( B C )

学

考

试

a)

2-10.*

X

Y

Z

a

A

B

C

b

W

X

Y

Z

c

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

1

0

0

0

1

1

0

0

0

1

0

0

1

0

0

0

1

0

0

0

0

1

0

1

0

1

1

1

0

1

1

1

0

0

1

1

0

1

0

0

0

1

0

0

0

0

1

0

0

0

1

0

1

1

1

0

1

0

0

1

0

1

0

1

1

0

1

1

1

0

0

0

1

1

0

1

1

1

1

1

1

1

1

1

0

1

1

1

0

1

0

0

0

0

1

0

0

1

0

1

0

1

0

1

1

0

1

1

0

1

1

0

0

1

1

1

0

1

1

1

1

1

0

1

1

1

1

1

1

欢

迎

加

入

湖

南

大

Truth Tables a, b, c

4

( ABC )( AC )( AB)

Problem Solutions – Chapter 2

a)

Sum of Minterms:

XYZ XYZ XYZ XYZ

b)

Sum of Minterms:

ABC ABC ABC ABC

Product of Maxterms: ( A B C )( A B C )( A B C )( A B C )

Sum of Minterms:

WXYZ WXYZ WXYZ WXY Z WXYZ WXYZ WXYZ

68

c)

39

2

Product of Maxterms: ( X Y Z )( X Y Z )( X Y Z )( X Y Z )

Product of Maxterms: (W X Y Z )(W X Y Z )(W X Y Z )

05

(W X Y Z )(W X Y Z )(W X Y Z )

:

69

(W X Y Z )(W X Y Z )(W X Y Z )

2-11.

a)

E m(1, 2, 4, 6) M (0, 3, 5, 7),

b)

E m(0, 3, 5, 7),

c)

E F m(0, 1, 2, 4, 6, 7),

d)

E XYZ XYZ XY Z XYZ ,

e)

E Z ( X Y ) XYZ ,

a)

( AB C )( B CD) AB ABCD BC AB BC s.o.p.

F m(1, 3, 5, 6)

群

F XY Z XYZ XY Z XYZ

料

F Z ( X Y ) XYZ

试

b)

E F m(2, 4)

资

2-12.*

B( A C ) p.o.s.

F m(0, 2, 4, 7) M (1, 3, 5, 6)

X X ( X Y )(Y Z ) ( X X )( X ( X Y )(Y Z ))

考

( X X Y )( X Y Z ) p.o.s.

(1 Y )( X Y Z ) X Y Z s.o.p.

( A BC CD)( B EF ) ( A B C )( A B D)( A C D)( B EF )

学

c)

( A B C )( A B D)( A C D)( B E )( B F ) p.o.s.

大

( A BC CD)( B EF ) A( B EF ) BC ( B EF ) CD( B EF )

2-13.

a)

A

入

B

湖

南

AB AEF BCEF BCD CDEF s.o.p.

b)

c)

Y

Z

A

Z

加

C

D

C

Y

A

X

B

W

C

A

C

B

D

A

Y

C

X

Z

欢

迎

B

5

B

Problem Solutions – Chapter 2

2-14.

X 1

1

1

X 1 1

Z

XY + XZ + YZ

1 1

C

C + AB

1

1 1

1

1

C

AB + AC + BC

BC + AB + AC

or

2-15.*

1

1

1

1

1

1

1

c)

1

1

A

C

CB

AA+CB

1 1

1

A 1 1

1

C

BB+CC

资

Z

XZ

XZ

+ XY

B

料

X

B

b)

群

Y

a)

:

69

05

Z

X Y + YZ+XYZ

1

1

A 1

1

1

A 1

B

d)

B

c)

39

2

1

1

Y

b)

68

Y

a)

a)

b)

C

1

B

1

1

1 1

学

A

大

D

Y

1

1

1

1

1

1

1

A

1

B

X

1 1

W

1

1

1

1

1

D

Z

AC AD ABC

X Z Y Z WXY W XYZ

南

BD ABC ACD

c)

C

1

考

1

1 1

试

2-16.

湖

2-17.

Y

a)

1

1

W

C

1

X

1

1

1

1

A

1

Z

1

1

1 1

1

B

1 1

D

F BC ACD ABD ABC ( ABD or ACD)

F XZ Y Z W XY W XYZ

欢

迎

加

入

1 1

b)

6

Problem Solutions – Chapter 2

b)

1

1

W

Z

m 3 5 6 7

m(3, 5, 6, 7)

1

1

1

1 1

X

A

1

b) Prime CD, AC, BD, ABD, BC

c)

Essential AC , BD, ABD

Prime AB, AC, AD, BC , BD, CD

Essential AC, BC , BD

2-20.

b) Prime WY , XY ,WXZ ,W X , XYZ ,WYZ

料

a) Prime BD, ACD, ABC, ABC, ACD

Essential WY , XY

Redundant BD

Redundant W X , XYZ ,WYZ

F ACD ABC ABC ACD

F WY XY WXZ

考

Essential W Z , X Z

Redundant =W XY ,W XZ ,WXY

a)

F

大

2-21.

Y

0

0

0

0

C

0

X

A

湖

W

0

F

b)

南

0

0

学

F W Z X Z WYZ XYZ

试

资

Essential ACD, ABC, ABC, ACD

Prime W Z , X Z ,WYZ , XYZ ,W XY ,W XZ ,WXY

c)

1

B

群

Essential XZ , XZ

1

1

D

m 0 2 6 7 8 10 13 15

m(0, 2, 6, 7, 8, 10, 13, 15)

Z

m 3 4 5 7 9 13 14 15

m(3, 4, 5, 7, 9, 13, 14, 15)

2-19.*

a) Prime XZ , WX , XZ , WZ

1

1

1

05

X

1

:

69

1

C

1

1

1

Y

1

c)

Y

68

a)

39

2

2-18.*

0

0

0 0

B

0 0

0

0

D

入

Z

0

0

F m(0, 2, 6, 7, 8, 9, 10, 12, 14, 15)

加

F m(3,4,5,6,7,9,11,13)

F BD BC ABC AD

F (W X )(W Y Z )( X Y Z )

F ( B D)( B C)( A B C )( A D)

迎

F W X WYZ XYZ

欢

2-22.*

a) s.o.p.

p.o.s.

CD AC BD

(C D)( A D)( A B C )

b) s.o.p.

p.o.s.

AC BD AD

(C D)( A D)( A B C )

7

c) s.o.p.

p.o.s.

BD ABD ( ABC or ACD)

( A B)( B D)( B C D)

Problem Solutions – Chapter 2

2-23.

ABD ABC ABD ABC

b) s.o.p.

or

ACD BCD ACD BCD

p.o.s.

X YZ W Z

( X Y Z )(W X Z )

( A B D)( A B C )( A B D)( A B C )

p.o.s.

68

or ( A C D)( B C D)( A C D)(B C D)

b)

1

X X

A 1 X

1 X

A

C

c)

C

B

X

1

X 1

1

B

1

1

D

X

X

X

1

群

Z

F AD ( ABD BCD) or

F AC

1

W

X X

X

Y

1

1

1 X X

:

69

a)

05

2-24.

F XY Z W XY WYZ XYZ

料

( ACD BCD) or ( ABD ABC )

资

2-25.*

Y

b)

a)

A

1

1

1 X 1

W

考

X

C

a)(1)

入

1

0 1

X X

1 X

加

0

0 X

Z

迎

F WY Y Z

WYZ WX Z

1

1

X X

1

X

A

X

学

X

W

Y

X X

0 1

0 X

1

X X

1 X

0 1

0

0 X

b)(1)

C

b)(2)

X 0 X

0 1 X 0

B

0 1 1 0

A

Z

X

X 0

D

F ( XY or X Z ) WYZ WY Z (WXZ or WYZ )

F ((X Y) or (X+Z))(W+Y+Z)(W+Y+Z)

((W+X+Z) or (W+Y+Z))

8

1

1

1 X

1

X X

B

F BD

X

C

X 0 X

0 1 X 0

B

0 1 1 0

X

X

X

X 1

D

Primes

C,AD

Primes

AB=, AB

C, AD

BD BD

Essential

=

C

AD

Essential C , AD

F = C + AD + BD or AB

F C AD( BD or AB)

大

0 X

X X

0 1

W

a)(2)

湖

Y

1

C

1

1 X

X

c)

Z

= ,XZ

XZ, WXY

WXY, WXY

PrimesPrimes

XZ , XZ

WXY

WY Z, WYZ

WYZ WYZ

Essential

Essential

XZ = XZ

F = XZ + WXY + WXY

F XZ WXY WXY

南

= ,AB

AC

BC ABC

PrimesPrimes

AB, AC

BC

, ABC

Essential

= ,AB

AC BC

Essential

AB, AC

BC

F = AB + AC + BC

F AB AC BC

2-26.

试

1

B

欢

39

2

a) s.o.p.

A

X

X 0

D

F BD

F BD

X

Problem Solutions – Chapter 2

39

2

2-27.*

X Y XY XY

Dual(X Y ) Dual( XY XY )

68

( X Y )( X Y )

XY XY

05

XY XY

:

69

X Y

2-28.

ABCD AD AD ABCD ( A D)

群

Note that X Y ( X Y ) XY

Letting X ABCD and Y A D,

料

We can observe from the map below or determine algebraically that XY is equal to 0.

C

1

1

试

1

1

考

A

1

资

1

1

1

B

1

D

For this situation,

学

X Y ( X Y ) XY

( X Y ) 0

大

X Y

南

So, we can write F ( A, B, C, D) X Y ABCD ( A D)

A

B

F

加

The longest path is from input C or D.

0.073 ns + 0.073 ns + 0.048 ns + 0.073 ns = 0.267 ns

欢

迎

2-29.*

C

入

湖

D

9

Problem Solutions – Chapter 2

39

2

2-30.

68

a)

05

b)

0

1.0

2.0

4.0

3.0

5.0

7.0

6.0

2-31.

t PLH-C, D to F 2t PHL 2t PLH 2(0.20) 2(0.36) 1.12 ns

t PHL-B to F 2t PHL t PLH 2(0.20) (0.36) 0.76 ns

t PLH-B to F 2t PHL t PLH 2(0.36) (0.20) 0.92 ns

b) t pd-C, D to F 4 t pd 4(0.28) 1.12 ns

t pd-B to F 3 t pd 3(0.28) 0.78 ns

资

学

t pd-A, B, C to F 2 t pd 2(0.28) 0.56 ns

考

t pd-A, B, C to F 0.56 ns

试

t PHL-A, B, C to F t PLH t PHL 0.36 0.20 0.56 ns

t PLH-A, B, C to F t PHL t PLH 0.20 0.36 0.56 ns

9.0 ns

料

t pd 1.12 ns

t pd-B to F 0.76 0.92 0.84 ns

8.0

群

a) t PHL-C, D to F 2t PLH 2 t PHL 2(0.36) 2(0.20) 1.12 ns

:

69

c)

大

c) For paths through an odd number of inverting gates with unequal gate tPHL and tPLH, path tPHL, tPLH, and tpd are different.

For paths through an even number of inverting gates, path tPHL, tPLH, and tpd are equal.

南

2-32.

欢

迎

加

入

湖

If the rejection time for inertial delays is greater than the propagation delay, then an output change can occur before it

can be predicted whether or not it is to occur due to the rejection time.

For example, with a delay of 2 ns and a rejection time of 3 ns, for a 2.5 ns pulse, the initial edge will have already

appeared at the output before the 3 ns has elapsed at which whether to reject or not is to be determined.

10

Problem Solutions – Chapter 2

39

2

2-33.+

68

a) The propagation delay is tpd max(tPHL 0.05, tPLH 0.10) 0.10 ns.

a) The propagation delay istpd = max(

tPHL = 0.05, tPLH = 0.10) = 0.10 ns.

a) The

tPHLpulse,

= 0.05,

= 0.10)

= 0.10occurs:

ns.

Assuming that the

gatepropagation

is an inverter,delay

for aistpositive

output

thet following

actually

pd = max(

Assuming that the gate is an inv, erter

f or

a positiv ePLH

output pulse, the f ollowing actually occurs:

Assuming that the gate is an inv, erter

f or a positiv e output pulse, the f ollowing actually occurs:

05

0.05 ns

0.10 ns0.05 ns

0.10 ns

:

69

If the input pulse is narrower than 0.05 ns, no output pulse occurs so the rejection time is 0.05 ns.

If the

input pulse

is narrower the

thanf ollowing

0.05 ns,results,

no output

pulse

occurs

so the delay

rejection

time

The

resulting

model

which

f erdif

ftime

rom

behav

, ioris 0.05 ns.

If the input pulse

is narrower

than

0.05predicts

ns, no output pulse

occurs so the rejection

isthe

0.05actual

ns. The resulting

model

The

resulting

model

predicts

the

f

ollowing

results,

which

f

er

dif

f

rom

the

actual

delay

behav

but models

rejection

behav

: delay behavior, but models the rejection behavior: : , ior

predicts the following

results,the

which

differ from

theior:

actual

but models the rejection behav ior: :

群

0.10 ns

0.10 ns 0.10 ns

0.10 ns

料

b) For a negative output pulse, the following actually occurs:

b) For a negative output pulse, the following actually occurs:

b) For a negative output pulse, the following actually occurs:

考

试

资

0.05 ns

0.15 ns 0.050.10

ns ns

0.10 ns

0.15 ns

The model predicts the f ollowing results, which

f ers

dif f rom the actual delay behav ior and f rom

The model predicts the following results, which differs from the actual delay behavior and from the actual rejection

the

actual

rejection

behavior:

The

model

predicts

the

f

ollowing

results,

which

f

ers

dif

f rom the actual delay behav ior and f rom

behavior:

the actual rejection behavior:

南

大

学

0.10 ns0.10 ns

0.10 ns0.10 ns

Overall, the model is inaccurate for both cases a and b, and provides a faulty rejection

model fthe

or model

case b.

Using anfor

avboth

erage

of

and

t b,

f or

t provides

would improv

e rejection

the delay

Overall,

is inaccurate

cases

at and

and

a faulty

PHL

PLH

pd

Overall, the model is inaccurate

for

both

and

b, and

provides

aof

faulty

rejection

model

for

case

b.fails.

Using

an

accuracy

thecases

model

for circuit

applications,

but

the

rejection

model

still

model

f orof

case

b. a Using

an av

erage

and

t

t

f

or

t

would

improv

e

the

delay

PHL

PLH

pd

average of tPHL and tPLH for

t

would

improve

the

delay

accuracy

of

the

model

for

circuit

applications,

but

the

rejection

pd

accuracy of the model for circuit applications, but the rejection model still fails.

model still fails.

X1

N1

N2

X2

N6

N3

N4

X3

N5

X4

迎

2-35.

加

入

湖

2-34.*

欢

-- Figure 4-40: Structural VHDL Description

library ieee;

use ieee.std_logic_1164.all;

entity nand2 is

port(in1, in2: in std_logic;

out1 : out std_logic);

end nand2;

11

f

Problem Solutions – Chapter 2

39

2

architecture concurrent of nand2 is

begin

out1 <= not (in1 and in2);

end architecture;

architecture concurrent of nand3 is

begin

out1 <= not (in1 and in2 and in3);

end concurrent;

料

群

library ieee;

use ieee.std_logic_1164.all;

entity nand4 is

port(in1, in2, in3, in4: in std_logic;

out1 : out std_logic);

end nand4;

-- The code above this point could be eliminated by using the library, func_prims.

:

69

05

68

library ieee;

use ieee.std_logic_1164.all;

entity nand3 is

port(in1, in2, in3 : in std_logic;

out1 : out std_logic);

end nand3;

考

试

资

library ieee;

use ieee.std_logic_1164.all;

entity fig440 is

port(X: in std_logic_vector(2 to 0);

f: out std_logic);

end fig440;

architecture structural_2 of fig440 is

南

component NAND3

port(in1, in2, in3: in std_logic;

out1: out std_logic);

end component;

大

学

component NAND2

port(in1, in2: in std_logic;

out1: out std_logic);

end component;

加

入

湖

signal T: std_logic_vector(0 to 4);

begin

g0: NAND2 port map (X(2),X(1),T(0));

g1: NAND2 port map (X(2),T(0),T(1));

g2: NAND2 port map (X(1),T(0),T(2));

g3: NAND3 port map (X(1),T(1),T(2),T(3));

g4: NAND2 port map (X(1),T(2),T(4));

g5: NAND2 port map (T(3),T(4),f);

end structural_2;

欢

迎

F =X0X 2 + X 1X 2

F X0X2 X1X0

12

Problem Solutions – Chapter 2

2-36.begin

X = D + BC

g0: begin

NOT _1 port map (D, x1);

Y = A BCD

g1: AND_2

map (B,

C,map

x2);

g0: port

NOT_1

port

2-38.*

料

资

g

大

学

begin

F <= (X and Z) or ((not Y) and Z);

end;

f

考

a

b

a

c

b

c

b

a

c

d

试

2-37.

群

:

69

05

68

39

2

X D BC

Y ABCD

(D, x1);

g2: NOR_2

map (A,

x1,map

x3); (B, C, x2);

g1: port

AND_2

port

g3: NAND_2

port mapport

(x1, x3,

x4);

g2: NOR_2

map

(A, x1, x3);

g4: OR_2

port

map

(x1,

x2,

x5);

g3: NAND_2 port map (x1, x3, x4);

g4: port

OR_2

g5: AND_2

mapport

(x4, map

x5, X);(x1, x2, x5);

g5: port

AND_2

portx5,map

g6: AND_2

map (x3,

Y); (x4, x5, X);

g6: AND_2 port map (x3, x5, Y);

end structural_1;

end structural_1;

南

2-39.*

X1

N1

N2

N6

N3

N4

X3

N5

X4

欢

迎

加

入

湖

X2

13

f

Problem Solutions – Chapter 2

2-40.

39

2

module circuit_4_50(A, B, C, D, X, Y);

input A, B, C, D;

output X, Y;

68

wire n1, n2, n3, n4, n5;

05

not

go(n1, D);

:

69

nand

g1(n4, n1, n3);

群

and

g2(n2, B, C),

g3(X, n4, n5),

g4(Y, n3, n5);

or

料

g5(n5, n1, n2);

nor

资

g6(n3, n1, A);

欢

迎

加

入

湖

南

大

学

考

试

endmodule

14

Problem Solutions – Chapter 2

2-41.

39

2

module circuit_4_51(X, F);

input [2:0]

module circuit_4_51(X,

F);X;

output

F;

input [2:0]

X;

output F;

[0:4] T;

nand

nand

g0(T[0],X[0],X[1]),

g0(T [0],X[0],X[1]),

g1(Tg1(T[1],X[0],T[0]),

[1],X[0],T [0]),

g2(Tg2(T[2],X[1],T[0]),

[2],X[1],T [0]),

g3(Tg3(T[3],X[2],T[1],T[2]),

[3],X[2],T [1],T [2]),

g4(T [4],X[2],T [2]),

g4(T[4],X[2],T[2]),

g5(F

,T [3],T [4]);

endmodule g5(F,T[3],T[4]);

endmodule

料

群

:

69

05

68

wire [0:4]wire

T;

试

考

a

b

a

c

b

c

b

a

c

d

资

2-42.

学

g

大

2-43.*

f

欢

迎

加

入

湖

南

module circuit_4_53(X, Y, Z, F);

input X, Y, Z;

output F;

assign F = (X & Z) | (Z & ~Y);

endmodule

15

Problem Solutions – Chapter 3

CHAPTER 3

39

2

© 2016 Pearson Education, Inc.

3-1.

05

68

Place a 1 in each K-map cell where 2 or more inputs are equal to 1.

Place a 1 in each K-map cell where 2 or more inputs are equal to 1.

Y

This is the same function as the carry

1

This is the same function as the

= XZ

F =FXZ

+ XY+ +XY

YZ+ YZ

for the full adder.

carry f or the f ull adder

.

1

1

1

X

:

69

Z

3-2.*

1

B

1 1

F = AB + AC

料

1

A

群

C

1 1

资

D

试

3-3.

G1G0

00 01 11 10

00 01 11 10

G3G2

00

01 1

1 1

10 X X

X X

X X

G1G0

G1G0

00 01 11 10

G3G2

00

01 1

10 X X

B2 G3G2

1 1

00

01 1

X X

X X

11

1

11

00 01 11 10

G3G2

B1 G2G1 G3G2 G1

1

1

1

1 X X

10 X X X X

B0 G3G0 G2G1G0 G2G1 G0

G2 G1G0 G3G2 G1 G0

入

B3 G3

1

11

南

10 X X

X X

X X

湖

11 1 1

大

00

01

学

G1G0

G3G2

考

Assuming inputs G3, G2, G1, G0 and outputs B3, B2, B1, B0, with G3 and B3 being the most significant bits, and treating the invalid

input combinations as don’t cares:

3-4.

加

a) For the 3 x 3 pattern, there are exactly three row, three column and two diagonal combinations that represent a win for the X

player: W = X1 X2 X3 + X4 X5 X6 + X7 X8 X9 + X1 X4 X7 + X2 X5 X8 + X3 X6 X9 + X1 X5 X9 + X3 X5 X7 Gate Input cost = 32

迎

b) W = X5 (X1 X9 + X2 X8 + X3 X7 + X4 X6) + X1 X2 X3 + X1 X4 X7 + X7 X8 X9 + X3 X6 X9 Gate Input Cost = 30

3-5.

欢

a) For the 4 x 4 pattern, there are exactly four row, four column and two diagonal combinations that represent a win for the X

player: W = X1 X2 X3 X4 + X5 X6 X7 X8 + X9 X10 X11 X12 + X13 X14 X15 X16 + X1 X5 X9 X13 X2 X6 X10 X14 + X3 X7 X11

X15 + X4 X8 X12 X16 + X1 X6 X11 X16 + X4 X7 X10 X13 Gate Input cost = 50

b) W = X1(X2 X3 X4 + X5 X9 X13 + X6 X11 X15) + X7(X5 X6 X8 + X3 X11 X15 + X4 X10 X13) + X9 X10 X 11 X12

+ X13 X14 X15 X16 + X2 X6 X10 X14 + X4 X8 X12 X16 Gate Input Cost = 48

1

Problem Solutions – Chapter 3

1

0110

1

0111

1

0101

0

0100

0

1100

0

1101

0

1111

0

1110

0

1010

0

1011

0

1001

0

1000

0

0

1

0

0

GNS

GNS

GNS

GNS = AC + AB

GNSGNS

AC= AC

AB+ AB

GNS = AC + AB

A

A

B

A

B

C

B

C

D

C

D

D

料

1

0010

资

1

0011

试

0001

考

1

B

B

B

A

A

A

C

C

C

YNS

YNS

YNS

YNS = ABCD

YNS = ABCD

YNS

= ABCD

YNS

ABCD

B

B

C

B

C

D

C

D

A

D

A

A

RNS

RNS

RNS

+ BCD

RNS = A

RNS = A + BCD

RNS = A + BCD

RNS A BCD

学

0000

YNS RNS

YEW REW

YNS ABCD

RNS GNS

GEW

YEWGEWREW

ABCD

GNS

REW

0000

1 YNS

0 RNS

0 0 GEW

0 YEW

1

0 ABCD

0 GNS

0

10 REW

YNS

RNS

GEW

0000

1

0

0

0 YEW

0

1

0001

1

0

0

0

0

1

0000

11 0 00

00 0 00

11

0

0

100

0001

0011

1

0

0

0

0

1

0001

11 0 00

00 0 00

11

0011

0

0

0

100

0010

1

0

0

0

1

0011

11

0

00

00

00

11

0010

0110

1 00

0

00 0

1

0

0

10

0010

11

0

00

00

00

11

0110

01110

1 00

0

00 0

0

1

0

1

0110

11

00

00

00

00

11

0111

0101

0

1

0

0

0

1

0

0

100

0111

10 0 01

00 0 00

11

0101

0100

0

0

1

0

0

1

0101

00 0 10

01 0 00

11

0100

0

1

0

100

1100

0

0

1

1

0

0100

00

0

11

01

00

10

1100

1101

0 00

0

10 1

0

0

1

10

1100

00

0

11

11

00

00

1101

11111

0 10

0

10 1

0

0

0

0

1101

00

00

11

11

00

00

1111

1110

0

0

1

1

0

0

0

000

1111

00 1 00

11 0 11

00

11101

1010

0

0

1

1

0

0

1110

00 1 00

11 0 11

00

0

1

000

1010

0

1011

0

0

1

1

0

1010

00

0

11

11

00

00

1011

0

1

01

1001

0 10

0

10 0

0

1011

00

0

11

10

01

00

1001

1000

0 10

0

10 0

0

1

0

1

0

1001

00

00

11

00

10

01

1000

0

1

1

0

0

1000

0

0

1

0

0

1

0

1

0

1

0

1

大

GNS

群

3-7.+

ABCD

B

C

S5 S4 S3 S2 S1 S0

S0 C

0

0

0

0

0

0

0

0

0

S1 0

0

0

1

0

0

0

0

0

1

S2 ABC ABC

0

1

0

0

0

0

1

0

0

S3 ABC ABC

0

1

1

0

0

1

0

0

1

S4 AB AC

1

0

0

0

1

0

0

0

0

S5 AB

1

0

1

0

1

1

0

0

1

1

1

0

1

0

0

1

0

0

1

1

1

1

1

0

0

0

1

欢

迎

加

入

A

湖

南

3-8.

2

68

If odd parity is chosen, then an

alternative result for Z is:

Z X1 X 2 X 3

Z

0

1

1

0

1

0

0

1

:

69

X1 X2 X3

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

05

a) Detecting a change in one-out-ofthree inputs can be done using a parity

function as Z. The truth table shown is

for even parity. For this case,

Z X1 X 2 X 3

39

2

3-6.

B

B

B

GEW

A

GEW

A

GEW

A

C

C GEW = AB + AC

CGEW

GEW

= AB

AB

AC+ AC

A

A

B

A

B

C

B

C

D

C

D

D

B

B

C

B

C

D

C

D

A

D

A

A

GEW = AB + AC

YEW

YEW

YEW

YEW = ABCD

YEW = ABCD

YEW

= ABCD

YEW

ABCD

REW = A + BCD

REW = A + BCD

REW = A + BCD

REW A BCD

Problem Solutions – Chapter 3

A

B

C

D

S2

S1

S0

0

0

0

0

0

0

0

S0 BCD BCD AB ACD ABCD

0

0

0

1

0

0

1

0

0

1

0

0

0

1

S1 AB AB ACD BCD

0

0

1

1

0

1

0

0

1

0

0

0

1

0

0

1

0

1

0

1

0

0

1

1

0

0

1

0

0

1

1

1

0

1

1

1

0

0

0

0

1

1

1

0

0

1

0

1

1

1

0

1

0

0

1

1

1

0

1

1

0

1

1

1

1

0

0

0

1

1

1

1

0

1

1

0

0

1

1

1

0

1

0

0

1

1

1

1

1

0

0

A

B

C

D

W

X

Y

Z

W AC BD BD

0

0

0

0

0

0

1

1

X BCD BC+BD

0

0

0

1

0

1

0

0

0

0

1

0

Y CD +CD

0

0

1

1

0

1

0

0

0

1

0

0

1

1

0

1

1

1

05

:

69

群

料

资

考

试

3-10.

1

0

1

0

1

1

0

0

1

1

1

1

1

0

0

0

0

1

0

0

1

1

1

1

0

1

0

0

0

0

1

0

1

1

0

0

1

1

1

0

0

南

大

学

0

1010 to

XXXX

欢

迎

加

入

湖

1111

68

S2 ABC ABD

39

2

3-9.+

3

ZD

Problem Solutions – Chapter 3

0

0

0

0

0

0

0

0

0

1

0

1

0

1

0

1

1

0

1

0

1

0

1

0

1

1

1

1

0

1

1

0

0

1

1

1

0

1

0

0

1

1

1

1

1

0

0

RL

0

0

1

1

0

0

1

0

0

0

0

0

0

0

0

0

PL PS

LL = PSLS RS+ PSLS RR

LL PS LS RS PS LS RR

RL = PSLS RS + PSRS RR

RL PS LS RS PS RS RR

b)

1

1

1

1

C

1

1

1

1 1

1

1

B

A

1

1

1

D

B

A

a

1

1

1

1

1 1

1

1

C

1

南

1

1

入

D

e

C

1

A

A

1

1

1

B

1

D

c

d

C

1 1

B

A

1

1

1

1

D

C

1

1

1

B

1

B

湖

1

A

大

b

a

C

1

学

D

1

考

1

试

C

a)

资

3-12.

A

PL = PS

39

2

PL LL

0 0

LL RL

0 0

0 00

0

0 00

0

0

0 11

0

0 11

0 0

1

0

0 1

1

1 00

0 01

1

1

1 00

1

0 00

1 0

0

0

1 0

0

1 00

0 00

1

0

0

68

RR

0

PL

1

00

01

00

01

0

0

1

00

01

00

11

0

1

1

10

11

1

LS

05

PS LS RS

0 0 0

RS RR

0 0 0

0 0 0 01

0 0 0 11

0 1 1 00

0 1 1 10

0 1 1

0

0

0 1 1

0

1 0 10

1 1 0 00

1 1 0 11

1 0 0 01

1 1 0

0

1

1 1 0

1

1 1 01

1 1 1 11

0

0

PS

料

a)

:

69

a)

群

3-11.

1

1

1

1

1

D

D

f

g

B

加

b)

ab)

= AC + ABD + ABD + ABC

ba=

=AC

AB

++

ACD

+ +ABC

BD

ABD++ACD

AB C

迎

cb=

= AB

AB ++ BC

B C++AD

A C D + ACD

欢

B+ B +

A

C ABC

+ AD+ ABD + ABC + ACD

dc=

= ABCD

BCD ++ACD

A

AB C + A B D + A BC + ACD

ed=

= BCD

D+

+ ABD

ACD + ABC + ACD

fe=

=BC

ABC

f=

AB

C

+

A

BD

++A

BC ++ ACD

ACD

g = ABC + ABC

ABC

g=ABC + ABC + A BC + ACD

c)c)The

following

input

counts

include

input

inverters

and and

shareshare

ANDAND

gates.

The

followinggate

gate

input

counts

include

input

inverters

gates.

Total gate inputs for this solutions = 74. Total gate inputs for book solution is 70. The book solution is better by 4 gate inputs.

Total gate inputs for this solutions = 74. Total gate inputs for book solution is 70. The book solution is better by 4 gate inputs.

4

Problem Solutions – Chapter 3

X

Hierarchy

Y

X

Y

Z

W=XZ + YZ

39

2

3-13.

W

Z

W

W

G = B(CE + DE) + BC

3-14.

H

BC+BD

Hierarchy

3-15.+

BC+BD

c)

c)

Part b requires 6 fewer gates.

Part b requires 6 f ewer gates.

b)

欢

迎

加

入

湖

南

大

学

a)

= ABC + ABD + ABC + ABD

= ABC + ABD + ABC + ABD

试

H

考

X

Y

Z

G = A(BC

BD) + A(BC

+ BD)

G

A(BC+ +BD)+

A(BC

+BD)

资

X

Y

Z

H

料

Hierarchy

群

Hierarchy

X

Y

Z

:

69

X

Y

Z

05

F = A(CE + DE) + AD

Hierarchy

Hierarchy

X

Y

Z

W

68

Hierarchy

X

Y

Z

5

Problem Solutions – Chapter 3

GG

AA

BB

CC

A

B

C

DD

EE

FF

D

E

F

G

A

B

C

DD

EE

FF

D

E

F

b)b)Replacement

with

b) Replacement

withalents

equiv

Replacement

withequiv

equiv

alentsalents

b) Replacement with equivalents

GG

c)c)Cancel

inv

c) Cancel

inv erters

Cancel

inverters

erters

c) Cancel inverters

G

B

C

D

G

E

E

F

F

F

c) Manipulate inv erters

c) Manipulate inv erters

c) Manipulate inv erters

c) Manipulate inv erters

c) Manipulate inverters

G

E

F

F

F

A

A

B

A

BC

BG CD G

GC DE

D

E

E

F

F

F

欢

迎

加

入

湖

F

学

B

C

D

大

B

C

D

A

A

A

B

BC

CD

D

E

E

南

A

考

a) Original

circuit

a) Original

circuit

a) Original circuit

a) Original circuit

a) Original circuit

A

B

C

D

资

G

G

A

A

A

B

BC

CD

D

E

E

试

A

B

C

D

E

F

A

AB

BC

CD

DE

EF

F

料

3-17.

A

B

C

D

E

F

G

群

AA

BB

CC

G

05

a)a)Original

circuit

a) Original

Original

circuitcircuit

a) Original circuit

GG

68

A

B

C

D

E

F

:

69

AA

BB

CC

DD

EE

FF

39

2

3-16.

6

E

G

G

G

G

F

b) Replacement with equiv alents

b) Replacement with equiv alents

b)

Replacement

withequiv

equivalents

b) Replacement with

alents

b)BReplacement with equiv alents

A

C

D

G

G

E

G

F

d) Cancel inv erters

d) Cancel inv erters

d) Cancel inv erters

d) Cancel inverters

d) Cancel inv erters

G

Problem Solutions – Chapter 3

3-18.

:

69

05

68

39

2

a) Using Inverter, 2NAND, 3NAND and 4NAND gates.

试

资

料

群

1) Original circuit using AND, OR, Inverter

考

2) Mapped to Inverter, 2NAND, 3NAND, and 4NAND

欢

迎

加

入

湖

南

大

two literals become available ( AB,BC )

学

b) Using Inverter and 2NAND gates. There is not a one to one correspondence to the above schematics because common terms with only

7

Problem Solutions – Chapter 3

3-19.

群

:

69

05

68

39

2

For original circuit, see 3-18 part (a) above.

a) Mapped to Inverter, 2NOR, 3NOR, and 4NOR

南

大

学

考

试

资

料

b) Mapped to 2NOR and Inverter

3-20.

湖

X

T2

T1

F

T3

欢

加

Y0 = ABCE

Y1 = ABCE

G1

Y 0 = ABCE

Y2 = ABCE

G2A

迎

3-21.

入

Y

G2B

E

=EG1

G2A

G2B

= G1

G2A

G2B

E

Y 1= ABCE

Y3 = ABCE

Y2

ABCE

Y4

==

ABCE

Y5

==

ABCE

Y3

ABCE

Y6 = ABCE

Y 4 = ABCE

Y7 = ABCE

Y 5 = ABCE

Y 6 = ABCE

Y 7 = ABCE

8

T 1 XY T1 = X Y

T2 = X Y

T 2 XY T3 = X Y

T 3 XY F = XY + X Y

F XY XY

Except f or G1 = 1 and G2A and G2B = 0,

Y 0 through Y 7 are all 1’s. Oth

Except forthe

G1 outputs

= 1 and G2A

and G2B =

erwise,

one

of Y7

Y 0are

through

0, the outputs Y0 through

all 1’s. Y 7 is equal to 0

with

all

others

equal

to

Oth-erwise, one of Y0 through Y71.isThe output that is

0 hasequal

index

i =The

decimal v alue of

equal to 0 equal

with alltoothers

to 1.

aluestoof0 has

(A,B,C)

output thatthe

is vequal

indexini binary

= . E.g., if

(A,B,C)

= (1,1,0),

Y 6 = 0.

decimal value

of the

values ofthen

(A,B,C)

in binary. E.g., if (A,B,C) = (1,1,0), then

Y6 = 0.

Problem Solutions – Chapter 3

:

69

05

68

39

2

3-22.

3-23.

试

资

料

群

a)

Treating the input values 1010-1111 as don’t cares changes the behavior for those values:

a A C BD BD, b B CD CD, c B C D, d A CD BC BD BCD,

欢

迎

加

3-24. *

入

湖

The equations in this case are:

南

大

学

考

b)

e BD CD, f A CD BC BD, g A BC BC CD

a)

b)

VDD

F7

A

G7

F6

A

G6

F5

0

G5

F4

1

G4

F3

A

G3

F2

A

G2

F1

1

G1

F0

1

G0

9

Problem Solutions – Chapter 3

3-25.

a)

b)

F7

2

F

F4

G6

G5

8

G4

F3

G3

1

0

F2

G2

G1

F0

G0

05

F1

3-26.

a)

12

5

4

3

2

1

0

6

G(3:0)

G

F(3:0)

M

考

3-28.

DECODER

A0

A1

A2

0

1

2

3

4

5

6

7

D0

D1

D2

D3

D4

南

大

学

A0

A1

A2

D5

DECODER

A0

A1

A2

D8

0

1

2

3

4

5

6

7

D9

D 10

D 11

D 12

欢

迎

加

入

湖

D6

D7

A3

8

H

L

V

C

试

( S S S 2 M

S3 S 4 S 5 M

V = A = S0 S1 V

S2 AS

3 S04 S1 5 +

C V

C = V

S5

S4

S3

S2

S1

S0

3:0

资

S3 S4 S5 M

A = S 0 S1 S 2 SA3 S( S40 SS51 S+2 M

L

A

L = A

7:4

4

料

3-27.

)

4

群

F

b)

11

9

7

5

3

1

68

F5

:

69

A

G7

3

F6

39

2

VDD

VDD

D 13

D 14

D 15

10

Problem Solutions – Chapter 3

3-29.

DECODER

DECODER

A0

A1

EN

EN

En

0

1

2

3

0

1

2

3

D0

D1

D2

D3

DECODER

A0

A1

A0

A1

En

0

1

2

3

D4

D5

D6

D7

68

A2

A3

A0

A1

39

2

A0

A1

En

0

1

2

3

D8

D9

D10

D11

DECODER

A0

A1

A0

A1

D12

D13

D14

D15

群

En

0

1

2

3

:

69

A0

A1

05

DECODER

A0

A1

欢

迎

加

入

湖

南

大

学

考

试

资

料

3-30.*

11

Problem Solutions – Chapter 3

3-31.

(Errata: Replace “4” with “3” in “4-to-6-line decoder”)

DECODER

A0

A1

0

1

2

3

D0

39

2

A0

A1

D1

DECODER

A2

A0

68

D2

D3

0

1

05

D4

料

群

:

69

D5

a) The Truth Table:

Note: a = g, b = f , and c = e.

Note: a = g, b = f, and c = e.

资

f

d

0

g

0

d

0

0

1

1

1

1

d

1g

1d

10

1

d

1

1

1

1

d

g

d

0

1

1

1

1

1

d

DECODER

学

大

A

X2

Note: a = g, b

XX0

B

A0

A1

A2

X1

X2

d

X2

1

1

1

d

0

1

2

3

4

5

6

=7 f ,

a

g

b

f

c

e

and c = e.

0 C

1

d

2

3

4

5

1

6X

7 2

DECODER

0

X1

1

D

d

B = X1 + X2

C = X1X 2

C

X0

X0

B

Gate input cost: b = 4 compared to a = 27 + 11 = 38

1

d

d

d

1 1

1

1

A

A = XX00

X1

X2

1

d

X1

1

1X+1 X2X 2

BB

=X

X2 1

d

X1

X1

CC

=

X1X

X12X 2

Gate input cost: b = 4 compared to a = 27 + 11 = 38

Gate input cost: b = 4 compared to a = 27 + 11 = 38

12

X0

a

g

d

X0

d

d

X0

A = X0

欢

迎

加

入

湖

b) A = {d}

B = {a,g}

C = {c. e}

D = {b, f}

南

D = {b, f}

A0

A1

A2

X0

X1

X2

考

X 2Truth

X 1 Table:

X0 a b c d e

a) The

0 0 0 d d d d d

X2 X01 X00 1

a 0

b 0c 0

d 1

e 0f

0 0

0 1

0 0

d 1

d 0

d 0

d 0

d 0

d

0 1 1 1 0 0 1 0

0 0 1 0 0 0 1 0 0

1 0 0 1 1 0 0 0

0 1

1 0

0 1

1 1

0 1

0 0

0 1

0 0

0

a)

0 The

1 1

0 1

0 1 0 1

0

1 Truth

1 Table:

0

1X 2 1

0X 1 1

0X 0 1

1a d

1b d

0c d

0d d

0e d

1f

10 00 10 1d 1d 0d 1d 0d 1d

b) A = {d}

X

1 10 10 A

1 0 1 0B =0{a,g}

1 0 0 1 01 0 1 0

0 1C = {c.

0 e} 1 0 0 d 01 0 0

1 1 D =1{b, f}d d d d d d

0 1 1 1 0 0 1 0 0

1 0 0 1 1 0 01 0 1

b) 1A =0{d}1 1 1 0 1 d 0X 1 1

1B =1{a,g}

0 1 1X 2 1 0 1 1

C

=

{c.e}

1 1 1 d d d d1 d d

试

3-32.

X2

b

f

c

e1

d

d1

1

X1

D = X2

X0

D

d

X2 1 d

1

1

DD = X

X22

X1

Problem Solutions – Chapter 3

A0

D0

A1

:

69

D4

D5

D6

D7

群

EN

料

3-34.

K-Map for GE5: BCD = (C3,C2, C1, C0)

1

d

1

1

d

d

试

1

d

C2

考

C3

1

资

C1

d

C0

C2

GE5

C3

欢

迎

加

入

湖

南

Equations for output logic:

P0 = D0 + GE5·D1

P1 = D2 + GE5·D1

P2 = D3 + GE5·D4

P3 = D5 + GE5·D4

P4 = D6 + GE5·D7

P5 = D8 + GE5·D7

P6 = D9 + GE5·D10

P7 = D11 + GE5·D10

P8 = D12+ GE5·D13

P9 = D14 + D15 + GE5·D13

大

C1

C0

学

GE5 = C3 + C2 (C1 + C0)

05

D3

A2

68

D1

D2

d

39

2

3-33.

13

Problem Solutions – Chapter 3

X

X

1

A1

D0

X0

01

0

0

0

10

A

A 10

XX

00

0

1

1

10

V

A0

X0

01

1

1

0

11

D1

A1

V

0

1

1

1

1

D0

D1

X

1

D3

D2

1

1

D0

0

V

= 0D 0 +0 D1 1+ D 21+ D13

V A

D00 = DD

D32

1

0 D21+D

D2

A0

V

A0

D3

D3

D1

1

1

X

A0 AD

1 0 (=D1D0 D 12

A1 D0 D1

A1

68

X

D D

D3 1D2 D0 1

0 0 0 0 00

X X X X 1X

X X 1

X 1

0

X 1 0

1 1 0 0 00

1

1

1

D2

群

D0

05

0

D2

:

69

D3

39

2

3-35.*

料

3-36.

8

7

6

5

4

3

2

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

1

X

0

0

0

1

3-37.

入

a)

A3

A2

A1

A0

V

0

X

X

X

X

0

0

1

0

0

0

0

1

0

1

X

0

0

0

1

1

0

1

X

X

0

0

1

0

1

1

X

X

X

0

0

1

1

1

1

X

X

X

X

0

1

0

0

1

X

X

X

X

X

0

1

0

1

1

X

X

X

X

X

0

1

1

0

1

大

0

学

考

0

1

X

X

X

X

X

X

X

0

1

1

1

1

X

X

X

X

X

X

X

X

1

0

0

0

1

X

X

X

X

X

X

X

1

0

0

1

1

S2

S

0

1

南

X

1

X

湖

1

0

试

9

Binary Outputs

资

Decimal Inputs

b)

DECODER

欢

迎

加

S0

S1

S2

A0

A1

A2

0

1

2

3

4

5

6

7

I0

4x1 MUX

S0

S1

I0

I1

I2

I3

I1

I2

I3

S0

S1

0

1

2

3

Y

Y

4x1 MUX

I4

S0

S1

I4

I5

I6

I7

I5

I6

S0

S1

0

1

2

3

2x1 MUX

Y

Y

Y

I7

14

© 2016 Pearson Education, Inc., Hoboken, NJ. All rights reserved. This material is protected under all copyright laws as they currently

exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

Problem Solutions – Chapter 3

3-39.

试

资

T

a his

th nd wo

o eir is rk

w r sa co pro is

ill le u vi pr

de o rse de ot

st f a s d s ec

ro n an o te

y y p d le d

th a a ly by

e rt ss fo U

in o e r

te f t ss th nite

gr hi in e

ity s w g us d S

of or stu e o tat

th k ( de f i es

e in nt ns co

w cl le tr p

or ud a uc y

r

k

an ing rnin tors igh

d on g. in t la

is

w

D

no the iss tea s

t p W em ch

er or in ing

m ld a

itt W tio

ed id n

.

e

W

eb

)

料

群

:

69

05

68

39

2

3-38.

0

1

2

3

4

5

6

7

欢

迎

加

入

湖

南

大

学

A0

A1

A2

考

DECODER

S0

S1

S2

IA0

IA1

IA2

IA3

YA

IA4

IA5

IA6

IA7

IB0

IB1

IB2

IB3

YB

IB4

IB5

IB6

IB7

15

© 2016 Pearson Education, Inc., Hoboken, NJ. All rights reserved. This material is protected under all copyright laws as they currently

exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

Problem Solutions – Chapter 3

料

群

:

69

05

68

39

2

3-40.

欢

迎

3-42.*

加

入

湖

南

大

学

考

试

资

3-41.

8x1 MUX

D(7:0)

D(7:0) Y

0

A(2:0)

S(2:0)

8x1 MUX

D(14:8)

D(6:0) Y

0

D(7)

S(2:0)

A(3)

3 OR gates

16

Problem Solutions – Chapter 3

D0

D1

D2

D3

0

0

0

0

0

0

0

1

1

0

0

0

0

1

0

0

0

0

0

0

1

1

0

1

0

0

1

0

0

0

0

0

0

1

0

1

0

0

1

0

1

1

0

0

0

0

0

1

1

1

0

0

0

1

Consider E as the data input and A0, A1 as the

select lines. For a given combination on (A1,

A0), the value of E is distributed to the

corre-sponding D output. For example for

(A1, A0) = (10), the value of E appears on D2,

while all other outputs have value 0.

68

E

0

05

A0

0

3-44.

DECODER

0

1

2

3

4

5

6

7

F1

F2

群

A0

A1

A2

F3

料

X

Y

Z

a) LR = LT·BL + LT·BR + EM·BL = BL·(LT + EM) + LT·BR

RR = R

+ RT·BR

+ EM·BL

= BR·(R

+ EM)

+ RT·BR

a) LR LT·BL

T·BL

LT·BR

EM·BL

BL·(LT

TEM)

LT·BR

0

0

0

1

1

1

1

1

1

1

1