Introduction to Electronics Textbook

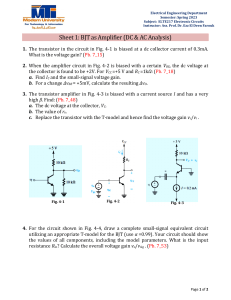

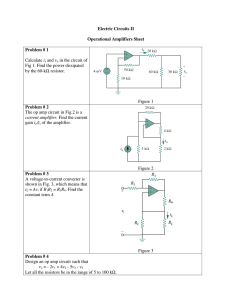

advertisement