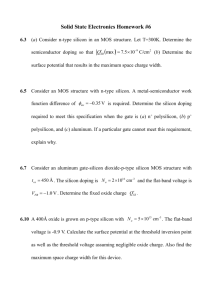

Problems 433 3. Why does the space charge region in the semiconductor of a MOS capacitor reach a maximum width once the inversion layer is formed? 4. Define surface potential. Does the surface potential change significantly with gate voltage once threshold is reached? 5. Sketch the energy-band diagram through a MOS structure with a p-type substrate and an n polysilicon gate under zero bias. 6. Define the flat-band voltage. Sketch the energy-band diagram in a MOS capacitor at flat band. 7. Define the threshold voltage. What is the surface potential at the threshold voltage? 8. Sketch the C–V characteristics of a MOS capacitor with an n-type substrate under the low-frequency condition. How do the characteristics change for the high-frequency condition? 9. Indicate the approximate capacitance at flat band on the C–V characteristic of a MOS capacitor with a p-type substrate under the high-frequency condition. 10. What is the effect on the C–V characteristics of a MOS capacitor with a p-type substrate if the amount of positive trapped oxide charge increases? 11. Qualitatively sketch the inversion charge density in the channel region when the transistor is biased in the nonsaturation region. Repeat for the case when the transistor is biased in the saturation region. 12. Define VDS(sat). 13. Define enhancement mode and depletion mode for both n-channel and p-channel devices. 14. Sketch the charge distribution through a MOS capacitor with a p-type substrate when biased in the inversion mode. Write the charge neutrality equation. 15. Discuss why the threshold voltage changes when a reverse-biased source-to-substrate voltage is applied to a MOSFET. PROBLEMS (Note: In the following problems, assume the semiconductor and oxide in the MOS system are silicon and silicon dioxide, respectively, and assume the temperature is T 300 K unless otherwise stated. Use Figure 10.16 to determine the metal–semiconductor work function difference.) Section 10.1 The Two-Terminal MOS Structure 10.1 10.2 10.3 The dc charge distributions of four ideal MOS capacitors are shown in Figure P10.1. For each case: (a) Is the semiconductor n or p type? (b) Is the device biased in the accumulation, depletion, or inversion mode? (c) Draw the energyband diagram in the semiconductor region. (a) Calculate the maximum space charge width xdT and the maximum space charge density Q SD (max) in a MOS capacitor with a p-type silicon substrate at T 300 K for doping concentrations of (i) Na 7 1015 cm3 and (ii) Na 3 1016 cm3. (b) Repeat part (a) for T 350 K. (a) Consider a MOS capacitor at T 300 K with an n-type silicon substrate. Determine the silicon doping concentration such that Q SD (max) 1.25 108 C/cm2. (b) What is the surface potential that results in the maximum space charge width? nea29583_ch10_371-442.indd 433 12/11/10 12:40 PM 434 CHAPTER 10 M Fundamentals of the Metal–Oxide–Semiconductor Field-Effect Transistor O S M O (a) M O S (b) S (c) M O S (d) Figure P10.1 | Figure for Problem 10.1. 10.4 10.5 10.6 10.7 10.8 nea29583_ch10_371-442.indd 434 Determine the metal–semiconductor work function difference ms in a MOS structure with p-type silicon for the case when the gate is (a) aluminum, (b) n polysilicon, and (c) p polysilicon. Let Na 6 1015 cm3. The silicon impurity doping concentration in an aluminum–silicon dioxide-silicon MOS device is Na 4 1016 cm3. Using the parameters in Example 10.2, determine the metal–semiconductor work function difference ms. Consider a MOS capacitor with an n-type silicon substrate. A metal–semiconductor work function difference of ms 0.30 V is required. Determine the silicon doping concentration required to meet this specification when the gate is (a) n polysilicon, (b) p polysilicon, and (c) aluminum. If a particular gate cannot meet this specification, explain why. (a) Consider the MOS capacitor described in Problem 10.5. For an oxide thickness of tox 20 nm 200 Å and an oxide charge of Q ss 5 1010 cm2, calculate the flat-band voltage. (b) Repeat part (a) for an oxide thickness of tox 8 nm 80 Å. (a) Consider an n polysilicon–silicon dioxide–n-type silicon MOS structure. Let Nd 4 1015 cm3. Calculate the ideal flat-band voltage for tox 20 nm 200 Å. (b) Considering the results of part (a), determine the shift in flat-band voltage for (i) Q ss 4 1010 cm2 and (ii) Q ss 1011 cm2. (c) Repeat parts (a) and (b) for an oxide thickness of tox 12 nm 120 Å. 12/11/10 12:40 PM Problems 10.9 10.10 10.11 10.12 10.13 10.14 10.15 10.16 10.17 10.18 *10.19 *10.20 435 Consider an aluminum gate–silicon dioxide–p-type silicon MOS structure with tox 450 Å. The silicon doping is Na 2 1016 cm3 and the flat-band voltage is VFB 1.0 V. Determine the fixed oxide charge Q ss . Consider a MOS device with a p-type silicon substrate with Na 2 1016 cm3. The oxide thickness is tox 15 nm 150 Å and the equivalent oxide charge is Q ss 7 1010 cm2. Calculate the threshold voltage for (a) an n polysilicon gate, (b) a p polysilicon gate, and (c) an aluminum gate. Repeat Problem 10.10 for an n-type silicon substrate with a doping of Nd 3 1015 cm3. A 400-Å oxide is grown on p-type silicon with Na 5 1015 cm3. The flat-band voltage is 0.9 V. Calculate the surface potential at the threshold inversion point as well as the threshold voltage assuming negligible oxide charge. Also find the maximum space charge width for this device. A MOS device with an aluminum gate is fabricated on a p-type silicon substrate. The oxide thickness is tox 22 nm 220 Å and the trapped oxide charge is Q ss 4 1010 cm2. The measured threshold voltage is VT 0.45 V. Determine the p-type doping concentration. Consider a MOS device with the following parameters: p polysilicon gate, n-type silicon substrate, tox 18 nm 180 Å, and Q ss 4 1010 cm2. Determine the silicon doping concentration such that the threshold voltage is in the range 0.35 VTP 0.25 V. Repeat Problem 10.13 for an n-type silicon substrate if the measured threshold voltage is VT 0.975 V. Determine the n-type doping concentration. An n polysilicon gate–silicon dioxide–silicon MOS capacitor has an oxide thickness of tox 18 nm 180 Å and a doping of Na 1015 cm3. The oxide charge density is Qss 6 1010 cm2. Calculate the (a) flat-band voltage and (b) threshold voltage. An n-channel depletion mode MOSFET with an n polysilicon gate is shown in Figure 10.41. The n-channel doping is Nd 1015 cm3 and the oxide thickness is tox 500 Å. The equivalent fixed oxide charge is Q ss 1010 cm2. The n-channel thickness tc is equal to the maximum induced space charge width. (Disregard the space charge region at the n-channel–p-substrate junction.) (a) Determine the channel thickness tc and (b) calculate the threshold voltage. Consider a MOS capacitor with an n polysilicon gate and n-type silicon substrate. Assume Na 1016 cm3 and let EF Ec 0.2 eV in the n polysilicon. Assume the oxide has a thickness of tox 300 Å. Also assume that (polysilicon) (singlecrystal silicon). (a) Sketch the energy-band diagrams (i) for VG 0 and (ii) at flat band. (b) Calculate the metal–semiconductor work function difference. (c) Calculate the threshold voltage for the ideal case of zero fixed oxide charge and zero interface states. The threshold voltage of an n-channel MOSFET is given by Equation (10.31a). Plot VT versus temperature over the range 200 T 450 K. Consider both an aluminum gate and an n polysilicon gate. Assume the work functions are independent of temperature and use device parameters similar to those in Example 10.4. Plot the threshold voltage of an n-channel MOSFET versus p-type substrate doping concentration similar to Figure 10.21. Consider both n and p polysilicon gates. Use reasonable device parameters. *Asterisks next to problems indicate problems that are more difficult. nea29583_ch10_371-442.indd 435 12/11/10 12:40 PM 436 CHAPTER 10 *10.21 10.22 Plot the threshold voltage of a p-channel MOSFET versus n-type substrate doping concentration similar to Figure 10.22. Consider both n and p polysilicon gates. Use reasonable device parameters. Consider an NMOS device with the parameters given in Problem 10.12. Plot VT versus tox over the range 20 tox 500 Å. Section 10.2 10.23 10.24 *10.25 Fundamentals of the Metal–Oxide–Semiconductor Field-Effect Transistor Capacitance–Voltage Characteristics An ideal MOS capacitor with an n polysilicon gate has a silicon dioxide thickness of tox 12 nm 120 Å on a p-type silicon substrate doped at Na 1016 cm3. Determine the capacitance Cox, CFB, Cmin, and C(inv) at (a) f 1 Hz and (b) f 1 MHz. (c) Determine VFB and VT. (d) Sketch CCox versus VG for parts (a) and (b). Repeat Problem 10.23 for an ideal MOS capacitor with a p polysilicon gate and an n-type silicon substrate doped at Nd 5 1014 cm3. Using superposition, show that the shift in the flat-band voltage due to a fixed charge distribution (x) in the oxide is given by t x (x) 1 _ VFB _ dx Cox 0 tox ox 10.26 10.27 10.28 10.29 Using the results of Problem 10.25, calculate the shift in flat-band voltage for tox 20 nm 200 Å for the following oxide charge distributions: (a) Q ss 8 1010 cm2 is entirely located at the oxide–semiconductor interface, (b) Q ss 8 1010 cm2 is uniformly distributed throughout the oxide, and (c) Q ss 8 1010 cm2 forms a triangular distribution with the peak at the oxide– semiconductor interface and is zero at the metal–oxide interface. An ideal MOS capacitor is fabricated by using intrinsic silicon and an n polysilicon gate. (a) Sketch the energy-band diagram through the MOS structure under flat-band conditions. (b) Sketch the low-frequency C–V characteristics from negative to positive gate voltage. Consider a MOS capacitor with a p-type substrate. Assume that donor-type interface traps exist only at midgap (i.e., at EFi). Sketch the high-frequency C–V curve from accumulation to inversion. Compare this sketch to the ideal C–V plot. Consider an SOS capacitor as shown in Figure P10.29. Assume the SiO2 is ideal (no trapped charge) and has a thickness of tox 500 Å. The doping concentrations are Nd 1016 cm3 and Na 1016 cm3. (a) Sketch the energy-band diagram through the device for (i) flat band, (ii) VG 3 V, and (iii) VG 3 V. (b) Calculate the flat-band voltage. (c) Estimate the voltage across the oxide for (i) VG 3 V and (ii) VG 3 V. (d) Sketch the high-frequency C–V characteristic curve. tox VG n type SiO2 p type Figure P10.29 | Figure for Problem 10.29. nea29583_ch10_371-442.indd 436 12/11/10 12:40 PM Problems 437 C (pF) 200 CFB 20 VFB 0 0.8 V VG Figure P10.30 | Figure for Problem 10.30. C 5 4 3 1 2 0 VG Figure P10.31 | Figure for Problem 10.31. 10.30 10.31 The high-frequency C–V characteristic curve of a MOS capacitor is shown in Figure P10.30. The area of the device is 2 103 cm2. The metal–semiconductor work function difference is ms 0.50 V, the oxide is SiO2, the semiconductor is silicon, and the semiconductor doping concentration is 2 1016 cm3. (a) Is the semiconductor n or p type? (b) What is the oxide thickness? (c) What is the equivalent trapped oxide charge density? (d) Determine the flat-band capacitance. Consider the high-frequency C–V plot shown in Figure P10.31. (a) Indicate which points correspond to flat-band, inversion, accumulation, threshold, and depletion modes. (b) Sketch the energy-band diagram in the semiconductor for each condition. Section 10.3 The Basic MOSFET Operation 10.32 An expression that includes the inversion charge density is given by Equation (10.59). Consider the definition of threshold voltage and show that the inversion charge density goes to zero at the drain terminal at saturation. (Hint: Let Vx VDS VDS(sat).) nea29583_ch10_371-442.indd 437 12/11/10 12:40 PM 438 CHAPTER 10 10.33 10.34 10.35 10.36 10.37 10.38 10.39 10.40 10.41 10.42 10.43 Fundamentals of the Metal–Oxide–Semiconductor Field-Effect Transistor Consider an n-channel MOSFET with the following parameters: k n 0.18 mA/V2, WL 8, and VT 0.4 V. Determine the drain current ID for (a) VGS 0.8 V, VDS 0.2 V; (b) VGS 0.8 V, VDS 1.2 V; (c) VGS 0.8 V, VDS 2.5 V; and (d) VGS 1.2 V, VDS 2.5 V. A p-channel MOSFET has the following parameters: kp 0.10 mA/V2, WL 15, and VT 0.4 V. Calculate the drain current ID for (a) VSG 0.8 V, VSD 0.25 V; (b) VSG 0.8 V, VSD 1.0 V; (c) VSG 1.2 V, VSD 1.0 V; and (d) VSG 1.2 V, VSD 2.0 V. The parameters of an n-channel MOSFET are kn 0.6 mA/V2 and VT 0.8 V. The drain current is 1 mA with applied voltages of VGS 1.4 V, VSB 0, and VDS 4 V. (a) What is the WL value? (b) What is the value of ID for VGS 1.85 V, VSB 0, and VDS 6 V? (c) Determine the value of ID for VGS 1.2 V, VSB 0, and VDS 0.15 V. Consider a p-channel MOSFET with the following parameters: kp 0.12 mA/V2 and WL 20. The drain current is 100 A with applied voltages of VSG 0, VBS 0, and VSD 1.0 V. (a) Determine the VT value. (b) Determine the drain current ID for VSG 0.4 V, VSB 0, and VSD 1.5 V. (c) What is the value of ID for VSG 0.6 V, VSB 0, and VSD 0.15 V? An ideal n-channel MOSFET has the following parameters: VT 0.45 V, n 425 cm2/V-s, tox 11 nm 110 Å, W 20 m, and L 1.2 m. (a) Plot ID versus VDS for 0 VDS 3 V and for VGS______ 0, 0.6, 1.2, 1.8, and 2.4 V. Indicate on each curve the VDS (sat) point. (b) Plot ID (sat) versus VGS for 0 VGS 2.4 V. (c) Plot ID versus VGS for 0 VGS 2.4 V and for VDS 0.1 V. Consider an ideal p-channel MOSFET with the following parameters: VT 0.35 V, p 210 cm2/V-s, tox 11 nm 110 Å, W 35 m, and L 1.2 m. (a) Plot ID versus VSD for 0 VSD 3 V and for VSG______ 0, 0.6, 1.2, 1.8, and 2.4 V. Indicate on each curve the VSD (sat) point. (b) Plot ID (sat) versus VSG for 0 VSG 2.4 V. (c) Plot ID versus VSG for 0 VSG 2.4 V and for VSD 0.1 V. Consider an n-channel MOSFET with the same parameters as described in Problem 10.37 except that VT 0.8 V. (a) Plot______ ID versus VDS for 0 VDS 3 V and for VGS 0.8, 0, 0.8, and 1.6 V. (b) Plot ID (sat) versus VGS for 0.8 VGS 1.6 V. Consider an n-channel enhancement mode MOSFET biased as shown in Figure P10.40. Sketch the current–voltage characteristics, ID versus VDS, for (a) VGD 0, (b) VGD VT2, and (c) VGD 2VT. Figure P10.41 shows the cross section of an NMOS device that includes source and drain resistances. These resistances take into account the bulk n semiconductor resistance and the ohmic contact resistance. The current–voltage relations can be generated by replacing VGS by VGIDRS and VDS by VDID(RS RD) in the ideal equations. Assume transistor parameters of VT 1 V and Kn 1 mA/V2. (a) Plot the following curves on the same graph: ID versus VD for VG 2 V and VG 3 V over the range 0 VD 5 V for (i ) RS RD 0 and __ (ii) RS RD 1 k. (b) Plot the following curves on the same graph: ID versus VG for VD 0.1 V and VD 5 V over the range 0 ID 1 mA for (i) RS RD 0 and (ii) RS RD 1 k. An n-channel MOSFET has the same parameters as given in Problem 10.37. The gate terminal is connected to the drain terminal. Plot ID versus VDS for 0 VDS 5 V. Determine the range of VDS over which the transistor is biased in the nonsaturation and saturation regions. The channel conductance for a p-channel MOSFET is defined as ID gd _ VSD nea29583_ch10_371-442.indd 438 VSD→0 12/11/10 12:40 PM Problems VD VG S 439 VGD G S D VDS G ID Channel D n RD RS n p type p type Figure P10.40 | Figure for Problem 10.40. 10.44 10.45 10.46 Figure P10.41 | Figure for Problem 10.41. Plot the channel conductance for the p-channel MOSFET described in Problem 10.38 for 0 VSG 2.4. The transconductance of an n-channel MOSFET is found to be gm ID VGS 1.25 mA/V when measured at VDS 50 mV. The threshold voltage is VT 0.3 V. (a) Determine the conductance parameter Kn. (b) What is the current at VGS 0.8 V and VDS 50 mV? (c) Determine the current at VGS 0.8 V and VDS 1.5 V. The experimental characteristics of an ideal n-channel MOSFET biased in the saturation region are shown in Figure P10.45. If WL 10 and tox 425 Å, determine VT and n. One curve of an n-channel MOSFET is characterized by the following parameters: ID (sat) 2 104 A, VDS (sat) 4 V, and VT 0.8 V. (a) What is the gate voltage? (b) What is the value of the conduction parameter? (c) If VG 2 V and VDS 2 V, determine ID. (d) If VG 3 V and VDS 1 V, determine ID. (e) For each of the conditions given in (c) and (d), sketch the inversion charge density and depletion region through the channel. 0.05 ID (A12) 0.04 0.03 0.02 0.01 0 1 VGS (V) 2 3 Figure P10.45 | Figure for Problem 10.45. nea29583_ch10_371-442.indd 439 12/11/10 12:40 PM 440 CHAPTER 10 10.47 10.48 10.49 10.50 10.51 10.52 10.53 10.54 (a) An ideal n-channel MOSFET has parameters tox 18 nm 180 Å, n 450 cm2/V-s, and VT 0.4 V. The measured current in the saturation region is ID (sat) 0.8 mA when biased at VGS 2.0 V. Determine the (i) process conduction parameter and (ii) width-to-length ratio. (b) An ideal p-channel MOSFET has the same oxide thickness as given in part (a), a mobility of p 210 cm2/V-s, and a threshold voltage of VT 0.4 V. The measured current in the saturation region is also ID (sat) 0.8 mA when biased at VSG 2.0 V. Determine the (i) process conduction parameter and (ii) width-to-length ratio. Consider the n-channel MOSFET described in Problem 10.37. (a) Calculate gmL for VDS 0.10 V. (b) Find gms for VGS 1.5 V. Consider the p-channel MOSFET described in Problem 10.38. (a) Calculate gmL for VSD 0.10 V. (b) Find gms for VSG 1.5 V. An n-channel MOSFET has the following parameters: Na 5 1016 cm3, tox 15 nm 150 Å, n 450 cm2/V-s, VFB 0.5 V, L 1.2 m, and W 8 m. ______ (a) Determine the body-effect coefficient. (b) Plot ID (sat) versus VGS over the range 0 ID 0.5 mA for source-to-body voltages of (i) VSB 0, (ii) VSB 1 V, (iii) VSB 2 V, and (iv) VSB 4 V. (c) What are the threshold voltages for the conditions given in part (b)? The substrate doping and body-effect coefficient of an n-channel MOSFET are Na 1016 cm3 and 0.12 V12, respectively. The threshold voltage is found to be VT 0.5 V when biased at VSB 2.5 V. What is the threshold voltage at VSB 0? A p-channel MOSFET has an oxide thickness of tox 20 nm 200 Å and a substrate doping of Nd 5 1015 cm3. (a) Find the body-effect coefficient. (b) Determine the body-to-source voltage, VBS, such that the shift in threshold voltage, VT, from the VBS 0 curve is VT 0.22 V. An NMOS device has the following parameters: n poly gate, tox 400 Å, Na 1015 cm3, and Qss 5 1010 cm2. (a) Determine VT. (b) Is it possible to apply a VSB voltage such that VT 0? If so, what is the value of VSB? Investigate the threshold voltage shift due to substrate bias. The threshold shift is given by Equation (10.81). Plot VT versus VSB over the range 0 VSB 5 V for several values of Na and tox. Determine the conditions for which VT is limited to a maximum value of 0.7 V over the range of VSB. Section 10.4 10.55 10.56 Fundamentals of the Metal–Oxide–Semiconductor Field-Effect Transistor Frequency Limitations Consider an ideal n-channel MOSFET with a width-to-length ratio of (WL) 10, an electron mobility of n 400 cm2 /V-s, an oxide thickness of tox 475 Å, and a threshold voltage of VT 0.65 V. (a) Determine the maximum value of source resistance so that the saturation transconductance gms is reduced by no more than 20 percent from its ideal value when VGS 5 V. (b) Using the value of rs calculated in part (a), how much is gms reduced from its ideal value when VGS 3 V? An n-channel MOSFET has the following parameters: n 400 cm2 /V-s L 2 m VT 0.75 V nea29583_ch10_371-442.indd 440 tox 500 Å W 20 m 12/11/10 12:40 PM Reading List 10.57 441 Assume the transistor is biased in the saturation region at VGS 4 V. (a) Calculate the ideal cutoff frequency. (b) Assume that the gate oxide overlaps both the source and drain contacts by 0.75 m. If a load resistance of RL 10 k is connected to the output, calculate the cutoff frequency. Repeat Problem 10.56 for the case when the electrons are traveling at a saturation velocity of vsat 4 106 cm /s. Summary and Review *10.58 *10.59 *10.60 *10.61 Design an ideal silicon n-channel MOSFET with a polysilicon gate to have a threshold voltage of VT 0.65 V. Assume an oxide thickness of tox 300 Å, a channel length of L 1.25 m, and a nominal value of Q ss 1.5 1011 cm2. It is desired to have a drain current of ID 50 A at VGS 2.5 V and VDS 0.1 V. Determine the substrate doping concentration, channel width, and type of gate required. Design an ideal silicon n-channel depletion mode MOSFET with a polysilicon gate to have a threshold voltage of VT 0.65 V. Assume an oxide thickness of tox 300 Å, a channel length of L 1.25 m, and a nominal value of Q ss 1.5 1011 cm2. It is desired to have a drain current of ID (sat) 50 A at VGS 0. Determine the type of gate, substrate doping concentration, and channel width required. Consider the CMOS inverter circuit shown in Figure 10.59a. Ideal n- and p-channel devices are to be designed with channel lengths of L 2.5 m and oxide thicknesses of tox 450 Å. Assume the inversion channel mobilities are one-half the bulk values. The threshold voltages of the n- and p-channel transistors are to be 0.5 V and 0.5 V, respectively. The drain current is to be ID 0.256 mA when the input voltage to the inverter is 1.5 V and 3.5 V with VDD 5 V. The gate material is to be the same in each device. Determine the type of gate, substrate doping concentrations, and channel widths. A complementary pair of ideal n-channel and p-channel MOSFETs is to be designed to produce the same I–V characteristics when they are equivalently biased. The devices are to have the same oxide thickness of 250 Å and the same channel length of L 2 m. Assume the SiO2 layer is ideal. The n-channel device is to have a channel width of W 20 m. Assume constant inversion layer mobilities of n 600 cm2 /V-s and p 220 cm2 /V-s. (a) Determine p-type and n-type substrate doping concentrations. (b) What are the threshold voltages? (c) What is the width of the p-channel device? READING LIST Dimitrijev, S. Principles of Semiconductor Devices. New York: Oxford University, 2006. 2. Hu, C. C. Modern Semiconductor Devices for Integrated Cicuits. Upper Saddle River, NJ: Pearson Prentice Hall, 2010. 3. Kano, K. Semiconductor Devices. Upper Saddle River, NJ: Prentice Hall, 1998. 4. Muller, R. S., and T. I. Kamins. Device Electronics for Integrated Circuits. 2nd ed. New York: Wiley, 1986. 1. nea29583_ch10_371-442.indd 441 12/11/10 12:40 PM