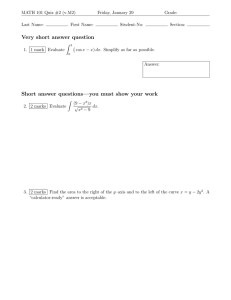

CS/EE-220 Digital Logic Circuits Assignment2 CS/EE-220 Digital Logic Circuits – Assignment 2 Instructor: Dr JI Due Date: 27/02/23 Due Time: 5:00pm Total Marks:100 Note: 1. Draw neat diagrams or truth tables (if needed), as neatness would carry marks. 2. You are supposed to submit hard copies in the drop box. No online submissions would be accepted. 3. Late submissions would be penalized by 25% per day, and no submission is allowed after 2 days. Q.No.1) Write the minimized SOP expression for the following expressions using Kmaps. Also, identify the essential prime implicants and prime implicants. 30 marks a) 𝐹(𝑊, 𝑋, 𝑌, 𝑍) = ∏ 𝑀(1, 3, 5, 6, 8, 15) b) 𝑊(𝐴, 𝐵, 𝐶, 𝐷) = ∑ 𝑚(1, 5, 6, 8, 9, 11, 15) + 𝑑(10, 12) c) 𝐺(𝐸, 𝐹, 𝐺, 𝐻) = ∏ 𝑀( 2, 3, 6, 7) + 𝑑(10, 14) Q.No.2) Design a 3x8 decoder using AND gates and NOT gates. 10 marks Q.No.3) Draw the internal circuit of a 16x1 multiplexer. 10 marks Q.No.4) Implement the following Boolean function using a decoder of appropriate size and a single multi-input NAND gate and inverters. F (A, B, C, D) = ∑m (0, 2, 3, 6, 7, 8, 10, 12, 15) 10 marks Q.No.5) Implement the following logic function using only 8-to-1 MUX. Out = Σ m (0,1,3,5,7,11,13,17,19,23,29,31) 10 marks Q. No.6) For the minterms F (A, B, C, D) = Σ m (1,3,4,6,8,10,13,14). Derive and draw the following mappings: a) Map the function F on 3:8 Decoders b) Map the function F on 4:1 MUXs 20 marks Q.No.7) Design a 20-to-1 MUX using any number of 8-to-1,4-to-1 and 2-to-1 MUX with no additional gates. No input or select line should be grounded. 10 marks Q.No.8) In the following figure a 4-to-1 MUX is used to implement a 4-input logic function. Draw the K-map that represents the output of this circuit. Spring Semester 2022-23 Page 1 of 2 CS/EE-220 Digital Logic Circuits Assignment2 10 marks Spring Semester 2022-23 Page 2 of 2