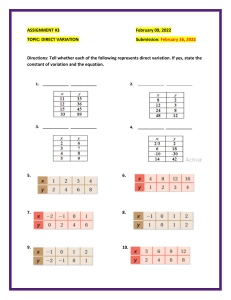

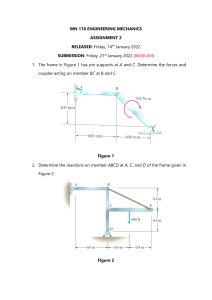

半導體製程作業 Issued: Mon. Sep. 05, 2022 Due: Mon. Sep. 12, 2022 18:00 Homework #0 (English Version) 本作業之目的在於促使同學思考半導體製程技術與各位過去或正在修習的機械 相關課程之關係. 請就我們第一周的課程 (overview 部分), 試著思考 The purpose of Hw #0 is for forcing you to think the correlations between semiconductor processing technologies and key mechanical engineering department courses you have taken or currently studied. Based on our class contents of the first week, please try to answer the following questions. 1. 下列科目, 是您已經修過, 或是正在修習. 到學期末, 您會完全了解熟習這些 科目對半導體工業的重要性 (Note: 半導體工業包括上游之原料供應, 儀器 設備, 中游之晶片製造, 以及下游之封裝檢測). 但剛開學, 您或許並不完全 清楚 (或者不清楚). 但是在此, 請以你目前上過第一周課程之認知, 試著盡 力下列課程(組)對於半導體產業何重要性? 請試著舉例申論說明之. (舉例請 勿一筆帶過, 需詳細說明以支持您的觀點). The following listed courses, you have either taken or is currently studying. Nevertheless, at the end of this semester, you shall understand the importance of these subjects to the semiconductor industries (including semiconductor materials, equipment, chip manufacture, and final packaging and inspections). At this moment, however, you might not get the points. Please based on the course introduction taught during the first week, try your best to tell us the importance and applications of the following courses to the state of the arts IC manufacturing. 普通化學 (General Chemistry) 機械材料 (engineering materials), 材料力學 (mechanics of materials) 流體力學 (fluid mechanics), 熱傳學(heat transfer) 控制系統 (automatic control) 動力學(dynamics),機動學(mechanism), 機械振動學(mechanical vibrations) 2. 修課同學有大三大四, 其中大三才剛開始上電子學, 可能對基礎元件工作原 理不是很清楚, 但希望能主動蒐集資料與閱讀, 釐清電子元件之工作原理. 如此, 方可知其製作過程的必要性. 因此, 請說明二極體 (p-n diode), 電晶體 (Bipolar Junction Transistor (BJT), i.e., npn and pnp), 以及場效電晶體 (field effect transistor (FET)) 的工作原理. Please try your best (you have either taken electronics or is studying currently) to tell us the working principles of p-n diode, BJT transistors (npn & pnp), and field effect transistors (JFETs or MOSFETs). If you did not learn them before, you can still to get ideas from literature or network survey. Issued: Mon. Sep. 12, 2022 Due: Wed. Sep. 21, 2022 18:00 半導體製程作業 Homework #1 (70 Points) 註: 作業於繳交日 18:00 前繳畢(至 710),遲交一律不與計分 Problem 1: IC technology scaling (15 Points) The number of square dice per wafer can be estimated to be N=(R-S)2/S2 where R is the radius of the wafer and S is the length of one side of the dice. Suppose that the cost of processing a single 8-inch diameter wafer in a particular process (0.25 m minimum feature size) is $1500, and that 90% of the dice fabricated are good. (a) Determine the cost per good die, for a die size of 0.5cm. (b) By scaling the technology for the 0.25 m minimum feature size to 0.18 m minimum feature size, the chip size can be proportionately reduced. However, the yield goes down to 70%. Determine the cost per good die for the scaled technology. (c) Suppose the cost of processing a 12-inch-diameter wafer in the 0.18 m process is $2500. What is the minimum yield required in order to make it worthwhile to run 12-inch wafers instead of 8-inch wafers? Problem 2: Doping (15 Points) Heavily doped regions are employed in IC devices, e.g., to provide low-resistance contacts between the semiconductor device and metal wiring. These heavily doped regions can be subjected to high-temperature annealing during the device-fabrication process. Dopant diffusion is enhanced when the semiconductor material is extrinsic. 19 Consider a Si sample doped with phosphorus at a concentration -3 of 510 cm . (a) What is the resistivity of this sample at room temperature (300 K)? (Hint: use the resistivity chart in handout 2. If you have Jeager’s book, it is at page 77) (b) At what temperature does this sample become intrinsic? (Assume that ni must be 10 times ND). Is this temperature possible? (c) Consider the pn diode shown below. Calculate the sheet resistivity of the n region, formed by masked implantation of phosphorus into boron-doped Si and subsequent thermal annealing. You may assume that the n and p regions are uniformly doped. n (1017 cm-3) p (1016 cm-3) 0.5 m Si Problem 3: (RC Time Constant vs. Device dimension) (You should ask me about this problem if I did not give you a detailed description) (15 Points) 導線的電阻乘上與其相串聯之介電層之電容, 為其 time constant. 若該導線為多晶矽, 1 Issued: Mon. Sep. 12, 2022 Due: Wed. Sep. 21, 2022 18:00 半導體製程作業 resistivity 為 800-cm, 長度為 1m, 厚度為 2000 Å, 且介電層為 SiO2, 為 3.90 (0= 8.85410-14 Farady/cm), 厚度為 150 Å。 The RC time constant for interconnection could be approximated as the resistance of conductive wires times the dielectric layer between the corresponding wires. Now, assume the wires are made of polysilicon with a resistivity of 800-cm and its length and thickness are 1m and 2000 Å, respectively. On the other hand, the dielectric layer is made of SiO2 with a relative permittivity of 3.90. (0= 8.85410-14 Farady/cm), The thickness of the dielectric layer is 150 Å。 1. 求該導線之 RC time constant 以及系統的 cut-off frequency (即 time constant 的倒數, 注意單位). Please estimate the RC time constant and the cut-off frequency of the interconnection. 2. 很明顯的, 如何增加電路的 cut-off frequency 有賴於如何降低, RC time constant. 請就 可行的工程方法, 提出您的策略. 以及這些策略可能帶來的問題. (注意, 身為未來的 工程師, 您的策略必須符合 IC 發展之趨勢以及您在上司眼中之評價 (i.e., 切勿不負責 任的亂提構想, 這只會搗毀您的 credit), 例如, 加大元件面積即是一個完全不可採用的 策略) Obviously, how to increase the cut-off frequency is equivalent to how to reduce the RC time constant. Based on your engineering judgements, please propose your strategy (and also faithfully evaluates the possible negative influences your method induced) to satisfy the requirement. Notice that you are expected as a gifted and respectful engineer and your proposal should be with a responsible attitude since this is not a game and your proposal will cause TSMC bloomed or bankrupted. Problem 4: (Doping Problem, Again) (15 Points) A Si crystal is homogeneously doped with phosphorus to a concentration of 1 1016/cm3. By mistake, a second impurity --either boron or arsenic (but not both ) is added. The overall hole concentration is determined to be 21016/cm3. (a) Is the Si p-type or n-type after adding the second impurity? What is the minority carrier concentration? (b) Is the second impurity boron or arsenic? What is the concentration added mistakenly? (c) The crystal is then doped further with the addition of arsenic (concentration = 1018/cm3). Find the resultant electrical resistivity. Problem 5: (Required Amount of Impurity) (10 Points) For 60 Kg pure silicon, it is desired to add some boron to convert this amount of silicon to a p-type silicon with a hole concentration of 1017/cm3. How many grams of boron should be added? (The following information might be useful: Molar weight of silicon = 28g/mole, boron = 10.8 g/mole, density of silicon = 2.33 g/cm3) 2 Issued: Mon. Sep. 19, 2022 Due: Wed Sep. 28, 2022 半導體製程作業 Homework #2 (75 Points) 註: 作業於繳交日 18:00 前繳畢,遲交一律不與計分 Problem 1: (Diode Fabrication Sequence Design starting from UNDOPED substrate) (20 Pts) Sol: You may including an extra mask for the purpose of n-type doping. The other processes remain the same. oxide pure Si thermal oxidation n-Si p-Si metal PR coating; Lithography (Mask #1); etching; strip PR n-type ion (e.g., phosphorus) implantation; drive in, anneal mask #1 PR coating, lithography (mask #2), p-type ion (e.g., Boron) )implantation, strip PR, drive in, anneal CVD oxide or re-oxidation mask #2 PR coating, lithography (mask #3); etching, PR strip sputtering metals mask #3 PR coating, lithography (mask #4); etching, PR strip mask #4 Issued: Mon. Sep. 19, 2022 Due: Wed Sep. 28, 2022 半導體製程作業 Problem 2: Silicon structures (15 Pts) Sol: Problem 3: Design an MOS Capacitor (25 Pts) Sol: Please refer to the flowchart shown in the next page for illustration. You are free to determine the physical dimensions. However, there is a rule of thumb and you should keep in mind that the size of the microelectronic devices usually in a few microns to hundreds of microns. So your final size of the capacitor should be in this range. In addition, your gate oxide thickness should also in the typical range (i.e., 0.01 – 0.1 microns). Finally, you should also very carefully to check the consistency of your units during calculation. Any inconsistency would result in significant errors. Issued: Mon. Sep. 19, 2022 Due: Wed Sep. 28, 2022 半導體製程作業 oxide n- Si n-Si p-Si thermal oxidation metal PR coating; Lithography (Mask #1); etching; strip PR gate oxidation mask #1 LPCVD p+ polysilicon PR coating, Lithography (Mask #2), etching; strip PR mask #2 etching oxide re-oxidation mask #3 PR coating, lithography (Mask #3), etch, strip PR sputtering metal mask #4 PR Coating, lithography (Mask #4), etching, strip PR Problem 4: Czochralski Growth (15 Points) 半導體製程作業 Issued: Mon. Sep. 19, 2022 Due: Wed Sep. 28, 2022 (a) All common impurities have different solubilities in the solid and in the melt. The segregation coefficient relates the concentration ratio of impurities between solid and melt phases. For the coefficients below unity, implying that the impurities preferentially segregate to the melt and the melt becomes progressively enriched with these impurities as the crystal is being pulled (and vice versa). This could result in doping concentration problem for wafers within the same batch. (b) When silicon is grown by the Czochralski method the melt is contained in a silica (quartz) crucible. During growth the walls of the crucible dissolve into the melt and Czochralski silicon therefore contains oxygen impurities with a typical concentration of 1018cm − 3. Perhaps surprisingly, oxygen impurities can have beneficial effects. Carefully chosen annealing conditions can allow the formation of oxygen precipitates. These have the effect of trapping unwanted transition metal impurities in a process known as gettering. Additionally, oxygen impurities can improve the mechanical strength of silicon wafers by immobilising any dislocations which may be introduced during device processing. (c) 略: obviously, key courses are: mechanical materials, heat transfer, and mechanics of materials. then identify the key technical contents related to crystal growth. You can Issued: Mon. Sep. 26, 2022 Due: Wed. Oct., 19 2022 半導體製程作業 Homework #3 Oxidation and Diffusion SOLUTION 註: 作業於繳交日 18:00 前繳畢,遲交一律不與計分 Problem 5. Constant Source Diffusion (20 Pts) A boron predeposition step is carried out at 900 C for 30 minutes for an n-type silicon wafer with a uniform background doping concentration of 1016 cm-3. a) What is the boron dose introduced into the silicon? b) What is the resulting p+/n junction depth? c) What is the sheet resistance of the diffused boron region? For this part problem, you should use the so-called “Irvin’s curves”; these plot the surface dopant concentration as a function of the sheet resistance-junction depth product, Rsxj, for various doping profiles (erfc or Gaussian) and background dopant concentrations. Note that you may use the solid solution limit of boron as the surface concentration used in this problem. Sol: 1 Issued: Mon. Sep. 26, 2022 Due: Wed. Oct., 19 2022 半導體製程作業 (c) Problem 6: Two-Step Diffusion (20 Pts) The n-well in a CMOS process is to be formed by a two-step phosphorus diffusion into a 5-ohm-cm p-type substrate. The final sheet resistance of the well is to be 1000 ohms per square and the final junction depth is to be 3 m. a) What is the final surface concentration in the n-well? (You should use the Irvin’s curves for this part of the problem.) b) Design a reasonable diffusion schedule for the drive-in step which produces the n-well. c) What is the phosphorus dose required to form the well? The following information may be useful for you: D0 and EA for phosphorus diffusion in silicon is 10.5 cm2s-1 and 3.69eV, respectively. And the diffusion coefficient can be expressed as D D0 exp( E A / kT ) . Sol: 2 半導體製程作業 Issued: Mon. Sep. 26, 2022 Due: Wed. Oct., 19 2022 3 半導體製程作業 Issued: MON. Oct. 24, 2022 Due: WED. Nov. 09, 2022 Homework #5 Ion Implantation 50 Points 註: 作業於繳交日 18:00 前繳畢 (此次請繳至 91A07),遲交一律不與計分 Problem 1: A MOSFET threshold voltage adjust implant is done through a gate oxide 0f 150 Å. The implant species is boron at 30 keV. Estimate the fraction of boron implanted in the oxide. (15 Pts) Problem 2: A typical high current implanter operates with an ion beam of 2 mA. How long would it take to implant a 150 mm diameter wafer with O+ to a dose of 11018cm-2? (15 Pts) Problem 3: Implanted Profile Boron (B + ) is implanted into a Si wafer, which is uniformly doped with 10 15 cm -3 Phosphorus, at an energy of 40 keV and a dose of 1x10 13 cm -2 . Afterwards, the Boron is activated during a 10-second rapid thermal anneal (RTA) at 1000 o C. (20 Pts) Note that the profile after RTA should be modified from N P Q /( 2 R P ) to a) N P Q /( 2( R P2 2 Dt ) ) . Sketch the final Boron and Phosphorus doping profiles (dopant concentration vs. depth). Concentration should be plotted on a logarithmic scale, and depth should be plotted on a linear scale. b) What is the resulting p-n junction depth? c) Estimate the sheet resistance of the Boron-doped layer. d) What is the minimum photoresist thickness that would block the Boron implant effectively? Assume that the stopping power of photoresist is 1.8X lower than that of Si. “Blocking the implant” means that the maximum concentration of the implanted Boron profile in the Si underneath the oxide is less than 1% of the background concentration. e) Suppose a 0.25 m-thick SiO2 layer is used to mask the Boron implant. What dose (Boron atoms per cm 2 ) is transmitted through this mask into the Si? Where DB,1000C = 2.6110-14 cm2/sec. 半導體製程作業 Issued: Oct. 31, 2022 Due: Nov. 16, 2022 Homework #6 Etching (65 Pts) Problem 1 Etching Profile with Mask (20 Pts) Solution: 半導體製程作業 Problem 2: Etch Selectivity (15 Pts) Solution: Issued: Oct. 31, 2022 Due: Nov. 16, 2022 半導體製程作業 Problem 3: Worst-Case Design Considerations for Etching (30 Pts) Solution: Issued: Oct. 31, 2022 Due: Nov. 16, 2022 Issued: Mon. Nov.14, 2022 Due: Wed Nov. 30, 2022 半導體製程作業 Homework #7 Thin Film Process (75 Pts) 註: 作業於繳交日 18:00 前繳畢,遲交一律不與計分. Problem 1 Contact Hole step coverage (20 Points) Metal films like Al are usually deposited with evaporation or sputtering. Step coverage over contact holes is one of the major problems in IC processing. In terms of the step coverage problem, especially when the contact hole is etched by anisotropic dry etching, indicate whether the following process changes will help (by entering a "+" ), hurt ( by entering a "-" ), or have no effect ( by entering a "0"). Give a brief explanation for your conclusions. ______ Use a wet chemical etch for the contact holes Explanation: ______ Increase substrate temperature during Al deposition Explanation: ______ Thicken the oxide around the contact holes while keeping contact size same Explanation: ______ Develop a CVD Al process Explanation: ______ Perform an oxide reflow step before metal deposition Explanation: Problem 2: CVD Conformal Deposition (15 Points) Conformal coverage will have the film thickness along the walls being the same as the flat surfaces. Sketch the cross-sections of the deposited film for a completely conformal deposition on the substarte shown below. Indicate the film topography when the deposited thickness is (i) 0.5 m, (ii) 1.0 m, (iii) 1.5 m, and (iv) 2.0 m. Problem 3 Poly Refill Planarization (25 Points) Suppose we would like to fabricate the following structure for oxide isolation. The poly-Si is just used as a filler to planarize the surface. Issued: Mon. Nov.14, 2022 Due: Wed Nov. 30, 2022 半導體製程作業 Suggest a process sequence which can achieve such a structure. Starting with a Si wafer, only ONE lithography step is allowed. You have to be specific with the processing techniques used in the DESCRIPTION column and sketch the cross-sections at each critical step. Problem 4: Residual stresses (15 Points) a) Germanium is a semiconductor with properties similar to silicon. The melting temperature of Ge (937 o C) is much lower than that of Si (1415 o C), so processing temperatures required for thin-film Ge deposition, dopant diffusion and thermal annealing are correspondingly lower. It is therefore possible to achieve low-stress, low-resistivity polycrystalline Ge (poly-Ge) films with significantly lower processing temperatures than required for poly-Si films, and hence it may be possible to fabricate MEMS devices using poly-Ge as the structural material, on wafers which have completed IC circuits (i.e. with Al metal interconnections formed). The thermal expansion coefficient of Ge (5.8x10 -6 /K) is much higher than that of the Si substrate material (2.6x10 -6 /K), however, which can result in significant residual stress, however. Estimate the residual stress (at room temperature) in a poly-Ge film deposited and subsequently annealed at 550 o C to eliminate intrinsic stress. The Young’s Modulus of poly-Ge is 130 GPa and the Poisson’s Ratio of poly-Ge is 0.25. b) Consider a released cantilever beam consisting of a bilayer of SiO2 and Al, shown in cross-section below: Al SiO2 air gap Si substrate Prior to release (masked etch of Si substrate, to undercut the beam), the SiO2 layer is under compressive stress, while the Al layer is under tensile stress. Would you expect the beam to bend up or down at the tip upon release? What would you expect to happen as the wafer (beam and Si substrate) is heated up? Provide a brief explanation of your answers. 半導體製程作業 Issued: Mon. Nov. 28, 2022 Due: Wed. Dec. 28, 2022 Homework #8 Metalization (80 Points) 註: 作業於繳交日 18:00 前繳畢,遲交一律不與計分. Problem 1 Metalization 15 Points (a) Why is a post-deposition anneal at ~450 C usually performed after aluminum deposition? (b) Why is it necessary to prevent aluminum “spiking” during the post-deposition anneal? (c) Two approaches to eliminating the aluminum spiking problem are: - addition of Si to the aluminum film - the use of a barrier layer between the Si and the aluminum film. Taking into consideration the information provided in the graph at right, discuss the advantages and disadvantages of each approach. Problem 2: Simple resistance and capacitance calculations 15 points (a) What is the sheet resistance of a 1-m-thick aluminum-copper-silicon line with a resistivity of 3.2 ohm-cm? (b) What would be the resistance of a line 500 m long and 10 m wide? (c) What is the capacitance of this line to the substrate if it is on an oxide which is 1 m thick? You can assume the substrate is heavily doped so that you can use the parallel-plate capacitance formula. 1 半導體製程作業 Issued: Mon. Nov. 28, 2022 Due: Wed. Dec. 28, 2022 (d) What is the RC product associated with this 500 m line? (e) If the oxide is replace by a gap filled with air (relatively permittivity =1), what is the new RC time constant? Problem 3: 15 Points Issues with Al metallization The right cartoon shows some major problems of using Al as the metal for multilevel metallization. Describe your understanding of the origins AND methodologies used to minimize/eliminate such problems. (a) Hillock and Void formation in interconnects (b) Al spiking into silicon substrate (c ) Step coverage problem SOL: (a)Hillock and void formation. Electron flux will transfer momentum to interconnect lattice atoms, creating atomic motions along direction of electron low. When there is a local divergence of the atomic flux (e.g. unequal grain boundary diffusion paths), mass accumulation (formation of hillocks) or mass depletion (formation of voids) can occur. There can lead to shorting of neighboring interconnects or complete open of an interconnect. The common practice to improve interconnect reliability is to create alloying precipitates (e.g. Al-Cu) along the grain boundaries which block grain boundary diffusion. (b) Aluminum spiking. A sintering step around 400-450C in a forming gas ambient is used after metallization ( to ensure better metal-Si contact and also to reduce Si/SiO2 interface states) . Substrate Si atoms dissolved in Al during sintering step, leaving voids behind. Al diffuses in to fill up the void, forming spiking. Solution is to saturate the Al with ~2% Si as the metal material. ( c) Step Coverage. Al or alloys are usually deposited by sputtering. Due to self-shadowing and geometrical shadowing, sidewalls and corner of steps will receive less flux, creating thinner deposition at sidewall and bottom corners. Solutions to minimize step coverage is to use a higher substrate temperature to enhance surface diffusion during Al deposition , or 2 半導體製程作業 Issued: Mon. Nov. 28, 2022 Due: Wed. Dec. 28, 2022 tilt and rotate substrate during deposition. A better approach is to use a W-plug (deposited by CVD) to fill up the contact hole before Al deposition. Problem 4 Copper interconnect process 15 Points Copper is proposed as an interconnect material in newer generation of ICs because of its low electrical resistivity. There is no reliable process recipe to etch copper by RIE. Propose and a process flow to fabricate copper interconnects in a planarized multilevel metallization scheme. Which method will you use to deposit copper? How will you pattern copper interconnects? . Starting with a SiO2 layer on Si substrate, show your steps with process description and cross-sections. SOL: 1) Starting material : Oxide on Si substrate 2) Deposit CVD oxide, pattern oxide trenches (RIE for vertical sidewalls) 3) Deposit Cu by platimg or CVD 4) Planarize Cu surface by CMP 3 半導體製程作業 Issued: Mon. Nov. 28, 2022 Due: Wed. Dec. 28, 2022 5) Deposit next layer of CVD oxide Problem 5 Planarization 20 Points The following cross-section (Fig.A) shows a poorly planned planarization process with planarization starting only at the Planarized Oxide step. (a) What difficulties you will encounter when etching contact holes through the Planarized Oxide to reach the Metal-1 (M1) surface ? (b) Instead of using LOCOS to form the Field Oxide, propose another isolation oxide structure to achieve better planarization. Sketch Fig.A again with your proposed isolation. (c) Continue with your structure in part(b), let us improve the planarization by performing a planarization step after the interlevel dielectric layer is deposited. Sketch Fig.A again. (d) After part(c) , you find you can still improve the planarization by putting a tungsten plug between M1 and the substrate N+ or P+ contact. Sketch Fig.A again with this improvement. Fig. A 4 半導體製程作業 Issued: Mon. Nov. 28, 2022 Due: Wed. Dec. 28, 2022 Sol: (a) The contact holes will have different depths to reach from planarized surface to M1 surface. We need very highly selectivity between metal and oxide etch to avoid excessive M1 etching. We also need very high degree of anisotropy for oxide etch to ensure consistent contact hole area on M1 surface. 5