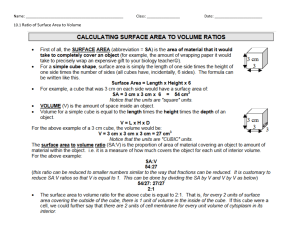

ENCS3330 Integrated Circuits HomeWork#3 2-INPUT NAND Gate and 4-bit Full Adder Microwind and PSPICE Student Name: NoorAldeen Tirhi Student ID: 1190081 Instructor: Dr.Khader Mohammad Part 1: CMOS 2-input Nand Gate Width ratio in PSPICE is 1:1. Parallel PMOS 6um Series NMOS 12um This will lead to approximately equal rise and fall time. Part1 2-Input NAND Gate 1a. PSPICE Simulation 5.0V 4.0V (281.100m,2.5005) (275.005m,2.5005) 3.0V 2.0V 1.0V 0V 0s V(V4:+) V(V5:+) 50ms V(C1:2) 100ms 150ms 200ms 250ms 300ms 350ms 400ms 450ms 500ms 450ms 500ms Time Both inputs act in the same way, starting at 0 volts, after 250ms both voltages start rising to 5 volts at constant rate, it takes 50ms to 5 volts. The output starts at 5 volts, while both inputs move towards 5 volts, the output voltage starts falling to 0 volts. 5.0V 4.0V (274.999m,2.5001) (276.419m,2.5003) 3.0V 2.0V 1.0V 0V 0s V(C1:2) V(V7:+) 50ms V(V5:+) 100ms 150ms 200ms 250ms 300ms 350ms 400ms Time Input A is 5 volts and Input B starts at 5 volts and starts changing to 0 volts at 250 ms at a constant rate, it needs 50 ms to complete this transition. The output starts at 0 volts, while Input B moves towards 0 volts, the output voltage starts rising to 5 volts. b. Microwind Layout Foundry is 0.035, 5 lambda is 175nm In the Palette window we can choose the materials and paint them on the layout, but also for a more accurate design we can use the choose “MOS Generator” option. From this window we can also choose ports, such as Vdd,Vss, Inputs and Outputs. We will choose clocks as Inputs and name them A,B. And choose the “visible node” option so we can see the output on the simulation. NMos Layout Generator: We have the NMOS at width 2u, and L at 0.35u. PMOS Layout Generator: We have the PMOS at width 1u, and L at 0.35u. With the two Devices generated, we will connect them as needed to produce the required results, here is the layout: 2- Check design rules, we can check the design rules from the buttons shown in the following picture: No errors. 3- Microwind Simulation X axis is Time in ns Y is voltage in volts 4- To migrate to smaller process, we can change to smaller foundry Part2 2-bit Full-Adder bit full adder is made of 1-bit full adders. it is made from 2 XOR gates and 2 AND gates and an OR gate. So, we need a layout and schematic for the XOR, AND and the OR gates XOR A 0 0 1 1 B 0 1 0 1 Out 0 1 1 0 A ⊕ B = ~AB + ~BA, hard to implement easier to implement XNOR ~(A ⊕ B) = ~A~B + BA A ⊕ B = ~(~A~B + BA) So we need to invert the two bits first, then we need to pass them to an “XOR” Gate, could not simulate using PSPICE, circuit is too big. AND A 0 0 1 1 B 0 1 0 1 Out 0 0 0 1 An AND Gate is hard to implement so it’s much easier to do a NAND gate and then inverting the output A.B = ~ (~ (A.B)) 6.0V 4.0V 2.0V 0V 0s V(V5:+) 0.1ms V(V4:+) 0.2ms V(C1:2) 0.3ms 0.4ms 0.5ms Time 0.6ms 0.7ms 0.8ms 0.9ms 1.0ms OR A 0 0 1 1 B 0 1 0 1 Out 0 1 1 1 An OR Gate is hard to implement so it’s much easier to do a NOR gate and then inverting the output A+B = ~ (~ (A+B)) The resulting schematic can be seen in Fig (2.3) OR Gate Schematic Fig(2.3) 6.0V 4.0V 2.0V 0V 0s V(V5:+) 0.1ms V(V4:+) 0.2ms V(C1:2) 0.3ms 0.4ms 0.5ms Time 0.6ms 0.7ms 0.8ms 0.9ms 1.0ms Layout XOR layout For the XOR N width = 10 Lambda, P width = 10 Lambda For the Inverter N width = 10 Lambda, P width = 10 Lambda Stick Diagram: Simulation AND Layout For the NAND N width = 20 Lambda, P width = 10 Lambda For the Inverter N width = 10 Lambda, P width = 10 Lambda OR Layout For the NOR N width = 10 Lambda, P width = 20 Lamda For the Inverter N width = 10 Lambda, P width = 10 Lambda Building the Full Adder Layout Block View Simulation 2-Bit Full Adder Simulation and test Cases: A =01, B = 01, C0 = 0 Result = 010 A=11, B=10, C0 =1 Result = 110 Time to produce output is about 400ps. This is the correct answer to both test cases, the 2 bit Full Adder is functioning correctly.