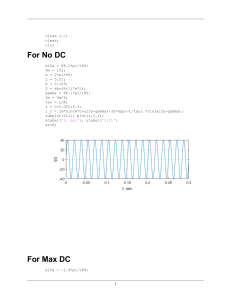

Name: Beeramgunta Ganesh M.Tech VLSI Design Roll.no:EC22M1004 ASSIGNMENT-2 DIGITAL IC DESIGN DATE: 5/12/2022 AIM: To design and implement CMOS Full adder circuit (using Mirroring property, Transmission Gate) & Plot the respective timing diagrams virtually using Ngspice Electronic Circuit Simulation tool. SOFTWARE TOOLS REQUIRED: Simulation Tool : Ngspice Electronic Circuit Simulator. EQUATIONS: Sum = ABC+(A+B+C) (Cout)' Cout = AB+BC+AC MIRRORING PROPERTY: LOGIC DIAGRAM: Page | 1 (No of Transistors = 28) INPUT-OUTPUT NODES: • • • • Node ‘1’ is fixed to VDD. Node ‘0’ is fixed to GROUND. Inputs A, B, C are given to nodes 2,3,4 respectively. Outputs Sum, Cout are taken from nodes 18,10 respectively. CODE: Full Adder Circuit 1 .MODEL CMOSN NMOS VT0=0.8V .MODEL CMOSP PMOS VT0=-0.9V vdd 1 0 dc 1.8v va 2 0 pulse 0v 5v 1ns 1ns 1ns 10ns 20ns vb 3 0 pulse 0v 5v 1ns 1ns 1ns 20ns 40ns vc 4 0 pulse 0v 5v 1ns 1ns 1ns 30ns 60ns mn1 7 2 0 0 cmosn w=100u l=10u mn2 7 3 0 0 cmosn w=100u l=10u mn3 6 4 7 0 cmosn w=100u l=10u mn4 9 3 0 0 cmosn w=100u l=10u mn5 6 2 9 0 cmosn w=100u l=10u mn6 10 6 0 0 cmosn w=100u l=10u mn7 12 2 0 0 cmosn w=100u l=10u mn8 12 3 0 0 cmosn w=100u l=10u mn9 12 4 0 0 cmosn w=100u l=10u mn10 13 6 12 0 cmosn w=100u l=10u mn11 17 4 0 0 cmosn w=100u l=10u mn12 16 3 17 0 cmosn w=100u l=10u mn13 13 2 16 0 cmosn w=100u l=10u mn14 18 13 0 0 cmosn w=100u l=10u mp1 5 2 1 1 cmosp w=200u l=10u mp2 5 3 1 1 cmosp w=200u l=10u mp3 6 4 5 1 cmosp w=200u l=10u mp4 8 2 1 1 cmosp w=200u l=10u mp5 6 3 8 1 cmosp w=200u l=10u mp6 10 6 1 1 cmosp w=200u l=10u mp7 11 2 1 1 cmosp w=200u l=10u mp8 11 3 1 1 cmosp w=200u l=10u mp9 11 4 1 1 cmosp w=200u l=10u mp10 13 6 11 1 cmosp w=200u l=10u mp11 15 2 1 1 cmosp w=200u l=10u mp12 14 3 15 1 cmosp w=200u l=10u mp13 13 4 14 1 cmosp w=200u l=10u mp14 18 13 1 1 cmosp w=200u l=10u Page | 2 .tran 0.1n 100n 1p 50p .control run set color0=black set color1=green set xbrushwidth=3.5 plot v(2) plot v(3) plot v(4) plot v(10) plot v(18) .endc .end Ngspice CODE Dialogue Box: Page | 3 SIMULATION OUTPUT: (A) (B) Page | 4 (C) (Sum) Page | 5 (Cout) TRANSMISSION GATE: LOGIC DIAGRAM: Page | 6 (No of Transistors = 24) INPUT-OUTPUT NODES: • • • • Node ‘1’ is fixed to VDD. Node ‘0’ is fixed to GROUND. Inputs A, B, C are given to nodes 2,3,4 respectively. Outputs Sum, Cout are taken from nodes 11,12 respectively. CODE: Full Adder Circuit 2 .MODEL CMOSN NMOS VT0=0.8V .MODEL CMOSP PMOS VT0=-0.9V vdd 1 0 dc 1.8v va 2 0 pulse 0v 5v 1ns 1ns 1ns 10ns 20ns vb 3 0 pulse 0v 5v 1ns 1ns 1ns 20ns 30ns vc 4 0 pulse 0v 5v 1ns 1ns 1ns 30ns 60ns mn1 5 2 0 0 cmosn w=100u l=10u mn2 6 3 5 0 cmosn w=100u l=10u mn3 7 3 2 0 cmosn w=100u l=10u mn4 3 5 6 0 cmosn w=100u l=10u mn5 3 2 7 0 cmosn w=100u l=10u mn6 8 4 0 0 cmosn w=100u l=10u mn7 9 7 8 0 cmosn w=100u l=10u mn8 9 6 4 0 cmosn w=100u l=10u mn9 10 7 5 0 cmosn w=100u l=10u mn10 10 6 8 0 cmosn w=100u l=10u mn11 11 9 0 0 cmosn w=100u l=10u mn12 12 10 0 0 cmosn w=100u l=10u mp1 5 2 1 1 cmosp w=200u l=10u mp2 6 3 2 1 cmosp w=200u l=10u mp3 7 3 5 1 cmosp w=200u l=10u mp4 3 2 6 1 cmosp w=200u l=10u mp5 3 5 7 1 cmosp w=200u l=10u mp6 8 4 1 1 cmosp w=200u l=10u mp7 9 6 8 1 cmosp w=200u l=10u mp8 9 7 4 1 cmosp w=200u l=10u mp9 10 6 5 1 cmosp w=200u l=10u mp10 10 7 8 1 cmosp w=200u l=10u mp11 11 9 1 1 cmosp w=200u l=10u mp12 12 10 1 1 cmosp w=200u l=10u .tran 0.1n 100n 1p 50p .control run set color0=black Page | 7 set color1=green set xbrushwidth=3.5 plot v(2) plot v(3) plot v(4) plot v(11) plot v(12) .endc .end Ngspice CODE Dialogue Box: Page | 8 SIMULATION OUTPUT: (A) (B) Page | 9 (C) (Sum) Page | 10 (Cout) RESULT: Therefore, CMOS Full adder circuit (using Mirroring property, Transmission Gate) has been designed, implemented & the respective timing diagrams are plotted virtually using Ngspice Electronic Circuit Simulation tool. Page | 11