electronics

Article

Open-Loop Class-BD Audio Amplifiers with Balanced

Common-Mode Output

Wojciech Kołodziejski * , Stanisław Kuta * and Jacek Jasielski *

Department of Electronics, Telecommunications and Mechatronics, University of Applied Sciences in Tarnow,

33-100 Tarnow, Poland

* Correspondence: w_kolodziejski@pwsztar.edu.pl (W.K.); st_kuta@pwsztar.edu.pl (S.K.);

j_jasielski@pwsztar.edu.pl (J.J.)

Citation: Kołodziejski, W.; Kuta, S.;

Jasielski, J. Open-Loop Class-BD

Audio Amplifiers with Balanced

Common-Mode Output. Electronics

2021, 10, 1381. https://doi.org/

10.3390/electronics10121381

Academic Editor: Raed A.

Abd-Alhameed

Abstract: This paper presents new architectures and implementations of original open-loop Class-BD

audio amplifiers with balanced Common-Mode output. The output stage of each proposed amplifier

includes the typical H-bridge with four MOSFETs and four additional MOSFET switches that balance

and keep the Common-Mode output constant. The presented amplifiers employ the extended NBDD

PWM or PSC PWM modulation scheme. When the output stage is built only on NMOSFET transistors,

gate drivers require a floating power supply, using a self-boost charge pump with capacitive isolation

of the control signal. The use of complementary MOSFETs in the output stage greatly simplifies

gate control systems. The proposed amplifiers were compared to the typical Class-BD configuration,

using the optimal NBDD modulation with respect to audio performance of the Differential-Mode

(DM) and Common-Mode (CM) outputs. Basic SPICE simulations and experimental studies have

shown that the proposed Class-BD amplifiers have similar audio performance to the prototype with

the optimal NBDD modulation scheme, while at the same time having a balanced constant voltage

CM output, thus eliminating the main contributor to radiation emission. As a result, the filtering of

the DM output signals can be greatly simplified, while the filtering of the CM output signals can be

theoretically eliminated. Practically, due to the timing errors added by the gate drivers, spikes are

generated at the CM output, which are very easy to filter out by the reduced LC output filter, even at

very low L.

Keywords: Class-BD audio amplifier; Common-Mode (CM) and Differential-Mode (DM) output

signals; Natural sampling Class-BD Double sided modulation (NBDD PWM); Phase Shifted Carrier

PWM (PSC PWM)

Received: 27 April 2021

Accepted: 7 June 2021

Published: 9 June 2021

Publisher’s Note: MDPI stays neutral

with regard to jurisdictional claims in

published maps and institutional affiliations.

Copyright: © 2021 by the authors.

Licensee MDPI, Basel, Switzerland.

This article is an open access article

distributed under the terms and

conditions of the Creative Commons

Attribution (CC BY) license (https://

creativecommons.org/licenses/by/

1. Introduction

Many works have been dedicated to different kinds of improved PWM methods and

Class D power amplifier topologies in order to achieve two of the most important features:

high fidelity and high efficiency.

Class-D amplifier architectures can generally be divided into two categories: openloop Class-D amplifiers with natural pulse width modulation (NPWM), or its discretetime version known as uniform PWM (UPWM); and closed-loop ones with Sigma–Delta

modulation (SDM) and bang–bang control modulation.

Depending on the sampling method, PWM schemes are generally categorized in

three of the most important classes: natural NPWM, uniform UPWM and linearized PWM

(LPWM) [1,2].

In addition, each PWM sampling method also distinguishes one-edge or two-edge

PWM, as well as two-level (Class-AD) or three-level (Class-BD) switching. Among four

fundamental NPWM schemes, NBDD (Natural sampling Class-BD Double sided) modulation, which is equivalent to the level-three version of Phase Shifted Carrier Pulse Width

Modulation (PSC PWM) [1,2], is the best in terms of the DM output and has by far the most

4.0/).

Electronics 2021, 10, 1381. https://doi.org/10.3390/electronics10121381

https://www.mdpi.com/journal/electronics

Electronics 2021, 10, 1381

most attractive spectral characteristic, which contains much less unwanted spectral com‐

ponents than all other PWM methods.

17

The H‐bridge output stage of the Class‐BD amplifier with the appropriate2 ofNBDD

modulator and time domain waveforms of the control signals and output voltages are

shown in Figure 1.

attractive

spectral

characteristic,

whichtime

contains

much the

less switch

unwanted

spectral

components

The control

signals

contain dead

between

states

where

all switches

than all other PWM methods.

are off to achieve zero voltage switching (ZVS) and to prevent shoot‐through currents.

The H-bridge output stage of the Class-BD amplifier with the appropriate NBDD

The DM and CM outputs of the NBDD modulation can be expressed after some con‐

modulator and time domain waveforms of the control signals and output voltages are

version

by in

theFigure

following

Double Fourier Series (DFS) expressions [1–3]:

shown

1.

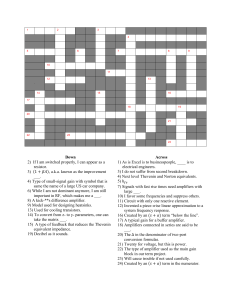

1. Class-BD

amplifier,

using

NBDD

PWM

modulator:(a)

(a)Block

Block diagram;

diagram; (b)

waveforms

of: NBDD

Figure Figure

1. Class‐BD

amplifier,

using

NBDD

PWM

modulator:

(b)time

timedomain

domain

waveforms

of: NBDD

and voltages

at DM

outputs.

output output

signalssignals

and voltages

at DM

andand

CMCM

outputs.

The control signals contain dead time between the switch states where all switches

zero voltage switching (ZVS) and to prevent shoot-through currents.

The

M and CM outputs of the NBDD modulation

mDM

can be expressed after some

J

n

(

m

n

)

n

n

2

by sin

the following

(DFS)

expressions [1–3]:

m c n Series

4conversion

m )t

sin Double

sin Fourier

DM

FNBDD

(t ) are

M cos(

m t )achieve

offto

m

DM

FNBDD (t) =

M cos( m t ) ∞

∞

m 1 n 1

2

2

2

M

(ωm t)−

cosmπM

Jn ( 2 )

(m+n)π

nπ

nπ

sin

sin 2 sin mΩ

=

∑ ∑

mπ

2

2 m4 M

−

c + nωm )t − 2

J

m=1 n=±

1

n

2

m

2

n

1

2

t )+

sin 2 m 2 n 1 t

sin ( ω

4 = M cos

m

m

c

2 m ∞ ±∞

2

2

m 1 n 0

2mπM

[2m+(2n+1)]π Jn ( 2 )

c + (2n + 1)ωm } t + π

+4 ∑ ∑

sin

sin

2mΩ

{

2mπ

2

2

(1)

(1)

m =1 n =0

mπM

∞

m M

J 0 FCM (t) = 2 ∑ J0 ( mπ2 ) sin mπ cos(mΩc t)+

NBDD

2

m

2

CM

sin m=1cos (m2 t )

FNBDD

(t ) 2

(2)

c m ∞ ∞ 2 Jn( mπM

(m+n)π

m 1

2 )

+2 ∑ ∑

sin

1

+

cos

nπ

cos

mΩ

+

nω

)

t

(

)

[(

]

mπ

c

m

2

2

2 m=1 n=±1

(2)

M2πF

Ωm=

c —switching angle frequency, ωm = 2π fm —audio angle frequency, M—

where

c

J

m n

n

2 index,

sin M ∈ [0, 1], 1Jn—Bessel

modulation

function

n-th

order.

2

cos n cos

(m c ofn

m )t

m

2 that

m 1 n 1 Equation (1) shows

effective sampling frequency

of the DM output signal is

2without increasing the transition frequency onthe output, and all harmonics

doubled

around odd multiples of the switching frequency are eliminated. However, the CM output

(Equation

some drawback,

as the frequency

spectrum of the NBDD output

—switching

angle frequency,

where c 2(2))

Fc reveals

m 2 f m —audio angle frequency,

contains the odd harmonics of the switching frequency and their even intermodulation

M—modulation

index, 𝑀 ∈ 0,1 , 𝐽 —Bessel function of n‐th order.

(IM) components. The CM output components are present at full scale, even at a very low

Equation

shows that

effective sampling frequency of the DM output signal is dou‐

level

of the (1)

modulating

signal.

bled without increasing the transition frequency on the output, and all harmonics around

Electronics 2021, 10, 1381

3 of 17

Fast switching of the output transistors, nearly rail-to-rail high swings, and wide frequency spectrum of PWM signals can lead to high-frequency RF emissions and interference

from the output stage, printed circuit board traces, filter and speaker cables, which become

inadvertent antennas [4–7].

A properly designed external LC filter, placed as close as possible to the switching

output stage, suppresses the unwanted RF effects, limits the amount of the output ripple

current, protects the speaker by attenuating the switching frequency, and also reduces

EMI [8–10]. The LC filter for the Class-BD amplifier with NBDD modulation must be

designed separately for DM and CM components. Filtration of unwanted components of

the spectrum at the DM output is very easy because the NBDD frequency spectrum has no

harmonics of the switching frequency, and no IM components around odd multiples of the

switching frequency. In terms of DM output, NBDD is the best and has, by far, the most

attractive spectral characteristics for all the other NPWM methods.

However, the frequency spectrum of the NBDD CM output contains the odd harmonics of the switching frequency, and their even IM components (2). The CM output

components are present at full scale, even at a very low level of the modulating signal.

The IM components around the first harmonic of the switching frequency are the most

undesirable because they put strong demands on the CM output signals filtering. The

output filter of the Cass-BD amplifier uses, most often, a common mode choke coil instead

of two normal inductors, which results in more effective CM output signal suppression

because the CM choke coil exhibits much larger impedance for the CM output current than

for the DM one [9,10].

In the last decade, filterless Class-D amplifiers have become very popular [10–12]. The

output of the filterless Class-D amplifier is directly connected to a load (speaker), and the

load itself provides filtering.

In many recent studies, the theory behind PWM and different modulation schemes, as

well as new linearization methods, have been discussed; thus, high-fidelity improvements

and EMI reduction of the filterless Class-D amplifiers have been proposed [6,7,12–16].

An original, Common-Mode Free BD (CMFBD) modulation that keeps the CM output

constant is presented in [7]. The DM output of this amplifier has the same performance

as that using the optimal NBDD modulation; however, the switching frequency of the

power MOSFETs creating the new H-bridge output stage is doubled. A detailed analysis of

the presented CMFBD modulation shows that it is equivalent to the Phase Shifted Carrier

Pulse Width Modulation (PSC PWM) that is considered as a multi-level PWM method for

Class-BD amplifiers [1,2].

Figure 2 shows the circuit diagram of the Class-BD output stage, using the PSCPMW

modulation scheme and the block diagram of the PSC PWM modulator that generates all

control S1 –S3 signals [2,7]. The H-bridge contains two additional series switches, M5 and

M6, connected parallel with the load, which are used to shunt the bi-directional inductive

load current when M1–M4 are off and to set both outputs at VDD /2 with the help of shunt

resistor Rb connected parallel with M1–M4 transistors. The DM and CM outputs of the

PSC PWM modulation can be expressed after some conversion by the following DFS

expressions [2,3]:

DM ( t ) = M cos( ω t )+

FFSC

m

mπM

∞ ±∞

Jn ( 2 )

(m+n)π

=

+2 ∑ ∑

sin

1

−

cos

(

nπ

)]

sin

m

Ω

+

nω

)

t

[

[

]

c

m

mπ

2

m=1 n=±1

= M cos(ωm t)+

∞ ±∞ Jn ( 2mπM )

[2m+(2n+1)]π

2

+4 ∑ ∑

sin

sin

2mΩ

+

2n

+

1

ω

t

[{

(

)

]

}

c

m

2mπ

2

(3)

m =1 n =0

CM

FFSC

(t) =

1

2

(4)

Electronics 2021, 10, 1381

Electronics

2021, 10, x FOR PEER REVIEW

4 of 17

4 of 17

2. Class-BD

amplifier

based

PSC

PWM

modulationscheme:

scheme: (a)

ofof

PSC

PWM

modulator;

(b) the

FigureFigure

2. Class‐BD

amplifier

based

on on

PSC

PWM

modulation

(a) Block

Blockdiagram

diagram

PSC

PWM

modulator;

(b) the

output

stage;

(c)

time

domain

waveforms

at

the

outputs

of

the

modulator

and

amplifier.

output stage; (c) time domain waveforms at the outputs of the modulator and amplifier.

Comparing Equations (1) and (2) with the corresponding Equations (3) and (4), as well

with Figure 2c, we can see that the DM output of the Class-BD amplifier with

the PSC PWM

is identical to that one for the

mmodulation

M

optimal NBDD PWM; however,

J

n

n) constant.

keeps

2 the

(m output

PSC

PWM

CM

sin

2

1 cos(n ) sin m c n m )t

m

of 2PSC PWM modulation is the need to use two additional series

mThe

1 n 1

disadvantage

switches,M5 and M6, as well as switching power transistors

with twice the frequency(3)

of

M cos(m t )

NBDD modulation, which results in higher switching power losses. In addition, power

in

2mshunt

M resistors R connected in parallel with the M1–M4 to set both outputs

losses occur

J

n

2m 2n b 1

2

atV4DD

/2, which alsosinincrease

the rise and

times

of the PWM

output pulses, contributing

sin fall

2m

c 2 n 1 m t

2m

2

1 n 0

switching

to a mfurther

increase

in

power

losses.

The organization of this paper is as follows. Section 2 presents original architectures

and implementations CM

of Class-BD

1 audio amplifiers with the balanced CM output. The

FFSC (t ) amplifier includes the typical H-bridge with four MOSFETs

(4)

output stage of each proposed

2

and four additional MOSFET switches that balance and keep the Common-Mode output

constant.

The Equations

presented amplifiers

the corresponding

extended NBDDEquations

PWM or PSC

PWM

Comparing

(1) and (2)employ

with the

(3) and

(4), as

modulation

schemes.

Section

3

presents

basic

SPICE

simulations

and

experimental

studies

well as Figure 1b with Figure 2c, we can see that the DM output of the Class‐BD amplifier

thePSC

proposed

amplifiers

implemented

the

complementary

MOSFET

pairs.how‐

withofthe

PWMClass-BD

modulation

is identical

to that on

one

for

the optimal NBDD

PWM;

Conclusions are given in Section 4.

DM

FFSC

(t ) as

M Figure

cos(m t ) 1b

ever, PSC PWM keeps the CM output constant.

disadvantage

of with

PSC Balanced

PWM modulation

the need to

two additional

2.The

Class-BD

Amplifiers

CM OutputisEmploying

theuse

Extended

NBDD series

PWM

or

PSC

PWM

Modulation

Scheme

switches, M5 and M6, as well as switching power transistors with twice the frequency of

Figure 3a shows

a slightly

improved

version

of the Class-BD

audio amplifier

withpower

a

NBDD modulation,

which

results

in higher

switching

power losses.

In addition,

balanced

CM

output

[3],

using

the

extended

NBDD

PWM

modulator

(Figure

3c).

losses occur in shunt resistors Rb connected in parallel with the M1–M4 to set both outputs

at V DD 2 , which also increase the rise and fall times of the PWM output pulses, contrib‐

uting to a further increase in switching power losses.

The organization of this paper is as follows. Section 2 presents original architectures

and implementations of Class‐BD audio amplifiers with the balanced CM output. The

output stage of each proposed amplifier includes the typical H‐bridge with four MOSFETs

Conclusions are given in Section 4.

Electronics 2021, 10, 1381

2. Class‐BD Amplifiers with Balanced CM Output Employing the Extended NBDD

PWM or PSC PWM Modulation Scheme

5 of 17

Figure 3a shows a slightly improved version of the Class‐BD audio amplifier with a

balanced CM output [3], using the extended NBDD PWM modulator (Figure 3c).

3. Class-BD

audio

amplifier

with

balancedCM

CMoutput,

output, using

using the

PWM

modulator:

(a) Topology

FigureFigure

3. Class‐BD

audio

amplifier

with

balanced

theextended

extendedNBDD

NBDD

PWM

modulator:

(a) Topology

the output

stage,

(b) time

domain

waveformsatatthe

theoutputs

outputs of the

amplifier.

(c) Block

diagram

of theof the

of the of

output

stage,

(b) time

domain

waveforms

themodulator

modulatorand

and

amplifier.

(c) Block

diagram

extended

NBDD

PWM

modulator.

Floatinggate

gatedriver

driver with

with galvanic

of of

thethe

control

signal.

galvanicisolation

isolation

control

signal.

extended

NBDD

PWM

modulator.

(d)(d)

Floating

This amplifier consists of a typical H-bridge output stage with four MOSFETs, and

This amplifier consists of a typical H‐bridge output stage with four MOSFETs, and

four additional MOSFET switches (M5, M6 and M7, M8), separating the H-bridge from

fourtheadditional

MOSFET switches (M5, M6 and M7, M8), separating the H‐bridge from

power supply, and switching the bridge’s power rails to the half-voltage VDD /2, at the

the time

power

supply,

and switching

the bridge’s

poweror

rails

the half‐voltage

VDD/2,

intervals

in which

the MOSFETs

of the high-side

the to

low-side

of the H-bridge

areat the

time

intervals

in

which

the

MOSFETs

of

the

high‐side

or

the

low‐side

of

the

H‐bridge

closed simultaneously. At these states, when M1, M3 transistors of the high-side are on, M7 are

closed

At these

states,

when

M1, M3

transistors

are on,

is offsimultaneously.

and M8 is on, whereas

when

M2, M4

transistors

of the

low-side of

arethe

on, high‐side

M5 is off and

is on.

frequency

of all

MOSFETs

is the same

as for

NBDD are

modulation,

M7M6

is off

andThe

M8switching

is on, whereas

when

M2,

M4 transistors

of the

low‐side

on, M5 is off

asThe

low switching

as that for PSC

PWM modulation

as shown

in Figure

2b.for NBDD modula‐

andi.e.,

M6twice

is on.

frequency

of all MOSFETs

is the

same as

When

all

gate

drivers

UCC27537

have

the

same

turn-on

and

turn-off

propagation

tion, i.e., twice as low as that for PSC PWM modulation as shown in Figure

2b.

delays (according to the datasheet, it is 17 ns), the modulated PWM waveform at the

H-bridge output is undistorted and is only delayed in relation to the control signals. These

delays do not have to be the same, as it is necessary to introduce an appropriate delay

time on the rising edges of all control signals turning on the MOSFETs, with respect to the

falling edges of all control signals turning off the MOSFETs. This allows a zero-switching

Electronics 2021, 10, 1381

6 of 17

voltage to be achieved to prevent shoot-through currents during switching processes;

however, dead time in particular has the most significant contribution of nonlinearity in the

H-bridge output. The optimal turn-on delay time for MOSFETs is a compromise between

low shoot-through currents and low switching power losses, and an acceptable THD level

at the output of the class D amplifier.

To implement this delay, an input AND gate with two Schmitt Trigger inputs of the

UCC27537 were used (Figure 3c). Time constant Rd Cd of the circuit connected to one

of the inputs of this gate determines the appropriate delay time on the rising edges of

control signal turning on the MOSFET. The gate driver output is connected to the gate

of the transistor via a resistor RG and an anti-parallel Schottky diode, providing turn-off

speed enhancement. The ground GND1 of the PWM controller is isolated from the floating

ground GND of the driver, using the digital isolator ISO7420 with an insulating barrier

made of silicon dioxide (SiO2).

Figure 3c also shows a self-boost charge pump circuit [16], generating the floating

power supply for the gate driver of the M2 transistor; the same solution applies to all

other MOSFETs. Continuous switching of MCP1 ensures that the isolated and floating

charge pump bias supply is available at all times to the corresponding driver, regardless

of the modulation index M and without any interference with the desired phase-leg

switching sequence.

Much simpler solutions for gate control systems can be used when the output stage of

the amplifier is implemented on complementary MOSFET pairs.

As shown in Figure 4, the gate drivers of all MOSFETs share a common ground GND1

and are directly driven from the NBDD modulator outputs. The block diagram of the

NBDD PWM modulator is also simpler (Figure 4d) because the output stage implemented

on complementary MOSFET pairs does not need pairs of complementary control signals.

Taking into account that M6 and M8 transistors are supplied with a half voltage

VDD /2, the supply voltage VDD of this system should be within a limited range, described

by the following inequalities:

2|VGS min ||at R

DS(on) max

>

VDD

2

;

VDD < |VGS max | and VDD < |VDS max |

(5)

At the higher gate voltage |VGSmin |, the drain to source resistance R DS(on)max in the on

state is less than a certain value at which the conduction power losses are still acceptable.

|VDSmax | and |VGSmax | are the maximum values for complementary MOSFETs, the most

common |VGSmax | < |VDSmax |, which result in the following condition: VDD < |VGSmax |.

Therefore, it is not possible to use the supply voltage higher than VDSmax : VDD < |VDSmax |.

Figure 4c shows a gate drive circuit with a shifted reference voltage level for the

control signals that is suitable for the applications with complementary power MOSFETs

with the following supply voltage:

VDD < |VGS max + VZ | and VDD < |VDSmax |

(6)

Shown in Figure 4c, the gate driver has the ability to control turn-on and turn-off

speeds independently for NMOSFET and PMOSFET. The RG resistor allows adjustment of

the MOSFET turn-on speed (RGn allows to adjust the delay time of the rising edges of the

PWM signal, while RGp allows to adjust the delay time of the falling edges) independently.

During turn-off, the antiparallel Schottky diode shunts out serial resistor RG ; in addition,

the gate charge is taken from the parallel CB capacitor charged to the Zener voltage VZ ,

providing turn-off speed enhancement. During the on-time of the switch, a small DC

current flows in the level shifter, keeping the driver biased in the right state.

An original Class-BD audio amplifier with a balanced CM output, implemented on

complementary MOSFET pairs and employing an extended PSC PWM modulation scheme,

is shown in Figure 5a.

Electronics

2021,

10, 1381

Electronics

2021, 10,

x FOR

PEER REVIEW

7 of 17

7 of 17

4. Class-BD

audio

amplifierwith

with balanced

balanced CM

output,

using

the extended

NBDD NBDD

PWM modulator

and implemented

FigureFigure

4. Class‐BD

audio

amplifier

CM

output,

using

the extended

PWM modulator

and imple‐

on

complementary

MOSFET

pairs:

(a)

Topology

of

the

output

stage.

(b)

Time

domain

waveforms

at

the

amplifier

outputs,

mented on complementary MOSFET pairs: (a) Topology of the output stage. (b) Time domain waveforms at the

amplifier

andand

PWM

control

signals

with delayed

turn-onturn‐on

times for

the NMOS

PMOS

transistors.

(c) Implementation

of the

and

PMOS transistors.

(c) Implementation

outputs,

PWM

control

signals

with delayed

times

for the and

NMOS

times

of of

thethe

NMOS

and and

PMOS.

(d) Block

diagram

of the extended

NBDD PWM

modulator.

of the turn-on

turn‐ondelay

delay

times

NMOS

PMOS.

(d) Block

diagram

of the extended

NBDD

PWM modulator.

Figure 5b shows the voltage waveforms at the DM and CM outputs of the amplifier, as

Shown in Figure 4c, the gate driver has the ability to control turn‐on and turn‐off

well as logical combinations of the control signals S1 , S2 and S3 with delayed turn-on times

speeds

independently

for NMOSFET

and PMOSFET.

RGtheresistor

allows adjustment

for the

NMOS and PMOS

transistors. Additionally,

in thisThe

case,

use of complementary

of the

MOSFET

turn‐on

speed

(R

Gn

allows

to

adjust

the

delay

time

of

the

rising

edges of

transistors in the power stage significantly simplify their control because the gate

drivers

the ofPWM

signal, share

whilea common

RGp allows

to adjust

timedriven

of thefrom

falling

edges) inde‐

all MOSFETs

ground

GND1 the

and delay

are directly

the extended

PSC PWM

modulator

outputs.

pendently.

During

turn‐off,

the antiparallel Schottky diode shunts out serial resistor RG;

Instead

shunting

resistors

Rb from

to setthe

both

outputsCat

VDD /2 (ascharged

in Figureto2b),

in addition,

theofgate

charge

is taken

parallel

B capacitor

theanZener

additional

H-bridge

was

created

by

M5,

M7

and

M6,

M8

transistors;

however,

the

lower

voltage VZ, providing turn‐off speed enhancement. During the on‐time of the switch, a

and upper sides of the new H-bridge are connected to the same power supply VDD /2 via

small DC current flows in the level shifter, keeping the driver biased in the right

state.

oppositely polarized Schottky diodes. Two parallel branches of the serial-connected two

An original Class‐BD audio amplifier with a balanced CM output, implemented on

NMOSFETs (M6, M8) or PMOSFETs (M5, M7) are connected parallel with the load, and are

complementary

MOSFET

pairsinductive

and employing

extended

PSC

modulation

used to shunt the

bi-directional

load currentan

when

M1–M4 are

offPWM

and to set

both

scheme,

is at

shown

in The

Figure

5a.implementation of the turn-on delay times of the NMOS and

outputs

VDD /2.

same

Figure

5b showsasthe

voltage

waveforms

at to

the

DM the

anddelay

CM time

outputs

ofrising

the amplifier,

PMOS

transistors,

shown

in Figure

4c, allows

adjust

of the

and

falling

edges

of

the

PWM

signal

independently.

The

architecture

presented

in

Figure

5a

as well as logical combinations of the control signals S 1 , S 2 and S 3 with delayed can

turn‐on

be implemented

using

NMOSFETs,

but galvanic

isolation

the case,

transmission

of

times

for the NMOS

andonly

PMOS

transistors.

Additionally,

ininthis

the usepath

of comple‐

the

control

signals

as

well

an

isolated

and

floating

bias

power

supply

for

gate

drivers

must

mentary transistors in the power stage significantly simplify their control because the gate

be provided.

drivers of all MOSFETs share a common ground GND1 and are directly driven from the

extended PSC PWM modulator outputs.

Instead of shunting resistors Rb to set both outputs at V DD 2 (as in Figure 2b), an

additional H‐bridge was created by M5, M7 and M6, M8 transistors; however, the lower

and upper sides of the new H‐bridge are connected to the same power supply V DD 2 via

oppositely polarized Schottky diodes. Two parallel branches of the serial‐connected two

Electronics 2021, 10, 1381

both outputs at V DD 2 . The same implementation of the turn‐on delay times of the NMOS

and PMOS transistors, as shown in Figure 4c, allows to adjust the delay time of the rising

and falling edges of the PWM signal independently. The architecture presented in Figure

5a can be implemented using only NMOSFETs, but galvanic isolation in the transmission

8 of 17

path of the control signals as well an isolated and floating bias power supply for gate

drivers must be provided.

Figure

5. Class-BD

audio

amplifier

withbalanced

balanced CM

PSC

PWM

modulation

scheme.

(a) A new

topology

of

Figure

5. Class‐BD

audio

amplifier

with

CM output,

output,using

using

PSC

PWM

modulation

scheme.

(a) A

new topology

output

stage.(b)

(b)Implementation

Implementation of

times

of the

NMOS

and and

PMOS.

(c) Time

waveforms

at

of thethe

output

stage.

ofthe

theturn-on

turn‐ondelay

delay

times

of the

NMOS

PMOS.

(c) domain

Time domain

waveforms

the

amplifier

outputs

and

PWM

control

signals

with

delayed

NMOS

and

PMOS

turn-on

times

(directly

at

the

gates

of

these

at the amplifier outputs and PWM control signals with delayed NMOS and PMOS turn‐on times (directly at the gates of

diagram

of the

extended

PSC PWM

modulator.

these transistors).

transistors).(d)

(d)Block

Block

diagram

of the

extended

PSC PWM

modulator.

3. Simulation and Measurement Results

3. Simulation and Measurement Results

SPICE simulations and experimental studies were used to compare the parameters

simulations

and

experimental

studies were

used to

compare

the parameters

of SPICE

the proposed

class BD

amplifiers

with a balanced

CM output

with

a prototype,

using

of the

proposed

class

BD

amplifiers

with

a

balanced

CM

output

with

a

prototype,

an optimal NBDD modulation scheme. All Class-BD amplifiers were tested for twousing

an different

optimalswitching

NBDD modulation

All Class‐BD

amplifiers

tested

for two dif‐

frequencies: Fscheme.

or Fc2 = 164

kHz, usingwere

with each

switching

c1 = 328 kHz

frequency

two different

sets ofFload

resistance

as

well

as

the

parameter

values

of

the

LC

ferent

switching

frequencies:

or

,

using

with

each

switching

328

kHz

F

164

kHz

c1

c2

output

filter:

(1)

R

=

4

Ω,

L

=

15

µH,

C

=

1.8

µF;

(2)

R

=

8

Ω,

L

=

30

µH,

C

=

1

µF

[8].

L

L

frequency two different

sets of load resistance as well

as the parameter values of the LC

Since the proposed amplifiers in Figures 4 and 5 are built on complementary MOSFETs,

output filter: (1) RL = 4 Ω, L = 15 μH, C = 1.8 μF ; (2) RL = 8 Ω, L = 30 μH, C = 1 μF [8].

and the applied supply voltage VDD = 24 V exceeds the VGSmax voltage (inequality 6), it

Since the proposed amplifiers in Figures 4 and 5 are built on complementary

was necessary to use a voltage level shifting circuit with a Zener diode (VZ = 6.2 V) to lower

MOSFETs,

and

the applied

supply

voltage

VDD (with

= 24 Vthe

exceeds

theof

VGSmax

voltage

(inequal‐

the control

voltage

from the

gate driver

output

exception

MOSFETs,

whose

ity sources

6), it was

to the

usehalf

a voltage

shiftingVirtual

circuitGND

with“0”

a Zener

diode (VZ = 6.2

are necessary

connected to

voltage level

VDD /2—i.e.,

V).

V) to lower

from the

driver

output

(with

the exception

of

Figure the

6a,b control

show thevoltage

time waveforms

of gate

the PWM

control

signals

generated

in one

selected period Tc , as well as the drain currents I(M1:D)–I(M4:D) and I(M5:D)–I(M8:D) of

the power MOSFETs in Figures 4 and 5, respectively. Optimal turn-on delay times of the

transistors were adjusted by selecting the resistance values RGn and RGp (Figures 4c and 5b).

Electronics 2021, 10, 1381

(a)

MOSFETs, whose sources are connected to the half voltage VDD/2—i.e., Virtual GND “0”

V).

Figure 6a,b show the time waveforms of the PWM control signals generated

in one

9 of 17

selected period Tc, as well as the drain currents I(M1:D)–I(M4:D) and I(M5:D)–I(M8:D) of

the power MOSFETs in Figures 4 and 5, respectively. Optimal turn‐on delay times of the

transistors were adjusted by selecting the resistance values RGn and RGp (Figures 4c and

In our design, for RGp = 68 Ω and RGn = 150 Ω, we obtain the optimal turn-on delay times

5b).ofIn

our design, for RGp = 68 Ω and RGn = 150 Ω, we obtain the optimal turn‐on delay

the transistors and significant limitation of the shoot-through currents.

times of the transistors and significant limitation of the shoot‐through currents.

(b)

Figure 6. Time waveforms of the PWM control signals generated in one selected period Tc, and the

Figure 6. Time waveforms of the PWM control signals generated in one selected period Tc , and the drain currents of the

drain currents of the power MOSFETs in the circuits shown: (a) in Figure 4, (b) and Figure 5, respec‐

power MOSFETs in the circuits shown: (a) in Figure 4, (b) and Figure 5, respectively.

tively.

Figure

7a–cshows

shows the efficiency

thethe

output

power

versus

modulation

index Mindex

as

Figure

7a–c

efficiencyand

and

output

power

versus

modulation

M

well

as

THD

as

a

function

of

the

signal

frequency

for

three

Class-BD

amplifiers:

Figure

7a,

as well as THD as a function of the signal frequency for three Class‐BD amplifiers: Figure

thethe

conventional

NBDD

modulator;

Figure

7b, shown

in Figure

4

7a, shown

shownininFigure

Figure1 with

1 with

conventional

NBDD

modulator;

Figure

7b, shown

in Figure

withthe

the extended

extended NBDD

and

Figure

7c, 7c,

shown

in Figure

5 with

the the

4 with

NBDDPWM

PWMmodulator;

modulator;

and

Figure

shown

in Figure

5 with

extended PSC PWM modulator. These characteristics were determined for two different

extended PSC PWM modulator. These characteristics were determined for two different

switching frequencies, with two sets of load resistance value as well as LC output filter

switching

frequencies,

withfrequency.

two setsAs

ofwe

load

value

as well

as LC output

parameter

values, for each

canresistance

see, the output

power

characteristics

of all filter

parameter

values,

for

each

frequency.

As

we

can

see,

the

output

power

characteristics

three amplifiers are almost identical, while the efficiencies of the two proposed amplifiers, of

Electronics 2021, 10, x FOR PEER REVIEW

Electronics 2021, 10, 1381

10 of 17

10 of 17

all three amplifiers are almost identical, while the efficiencies of the two proposed ampli‐

fiers, containing four additional transistor switches to balance the CM outputs, are slightly

containing four additional transistor switches to balance the CM outputs, are slightly

lower to the efficiency of the prototype NBDD modulator amplifier, due to the additional

lower to the efficiency of the prototype NBDD modulator amplifier, due to the additional

power

conduction states

states and

and in

in the

theswitching

switchingprocesses

processesofofthese

theseadditional

additional

power losses

losses in

in the

the conduction

transistor

switches.

transistor switches.

(a) Class‐BD amplifier shown in Figure 1 with conventional NBDD modulator

(b) Class‐BD amplifier shown in Figure 4 with extended NBDD PWM modulator

(c) Class‐BD amplifier shown in Figure 5 with extended PSC PWM modulator

Figure 7. Efficiency and output power vs. modulation index M, as well as THD as a function of the audio signal frequency

Figure 7. Efficiency and output power vs. modulation index M, as well as THD as a function of the audio signal frequency

for three amplifiers shown (a) in Figure 1, (b) in Figure 4, and (c) in Figure 5, respectively.

for three amplifiers shown (a) in Figure 1, (b) in Figure 4, and (c) in Figure 5, respectively.

Electronics 2021, 10, x FOR PEER REVIEW

Electronics 2021, 10, 1381

11 of 17

11 of 17

As we can see in Figure 7, all tested amplifiers show, however, slight distortions at

the DM outputs, caused by distorted switching sequences generated by the output stages

of these amplifiers. Switching timing error in a gate signal, due to turn‐on delay times of

As we can

in Figurehas

7, allthe

tested

amplifiers

show,

however, slight

at the

the transistors,

in see

particular,

most

significant

contribution

of distortions

nonlinearity

in DM

DM outputs, caused by distorted switching sequences generated by the output stages of

output stages. Based on Figure 7a–c, we can observe the following interesting properties.

these amplifiers. Switching timing error in a gate signal, due to turn-on delay times of the

Thetransistors,

proposed in

Class‐BD

amplifiers

have

a slightly

higher THD

than the prototype

ampli‐

particular,

has the most

significant

contribution

of nonlinearity

in DM output

fier stages.

in Figure

1 with

the conventional

NBDD modulation.

is because

the proposed

Based

on Figure

7a–c, we can observe

the following This

interesting

properties.

The

amplifiers

are

controlled

by

modulators

generating

control

signals

with

extended

proposed Class-BD amplifiers have a slightly higher THD than the prototype amplifiertiming,

in

giving

more

timing

errors added

in each

switching

period

Tc bythe

the

gate drivers,

such as

Figure

1 with

the conventional

NBDD

modulation.

This

is because

proposed

amplifiers

aretime,

controlled

modulators

generating

with is

extended

dead

of all control

tested signals

amplifiers

higher timing,

for thegiving

highermore

switch‐

ton toffbyand

tr t f . THD

timing errors added in each switching period T by the gate drivers, such as dead time,

ing frequency Fc1 328 kHz than for Fc 2 164ckHz because relative timing errors are

ton /to f f and tr /t f . THD of all tested amplifiers is higher for the higher switching frequency

.

greater

for

shorter

switching

Tcbecause

Fc1 =

328

kHz than

for Fc2 =period

164 kHz

relative timing errors are greater for shorter

For example,

8a–c shows the simulated THD + N frequency responses in the

switching

periodFigure

Tc .

Figure

simulated

THD + at

N frequency

responses

in the

band upFortoexample,

30 kHz

for 8a–c

the shows

three the

tested

amplifiers

two switching

frequencies

kHzFfor

the

three

tested

amplifiers

at

two

switching

frequencies

F

=

328

kHz M

c1

and

,

modulating

frequency

,

modulation

index

Fc1 band

328 up

kHzto 30

164

kHz

f

1

kHz

c2

m

and Fc2 = 164 kHz, modulating frequency f m = 1 kHz, modulation index M = 0.95, load

= 0.95, load resistance RL = 8 Ω, and filter parameters L = 30 μH and C = 1 μF.

resistance RL = 8 Ω, and filter parameters L = 30 µH and C = 1 µF.

(a) Class‐BD amplifier shown in Figure 1 with conventional NBDD modulator

(b) Class‐BD amplifier shown in Figure 4 with extended NBDD PWM modulator

Figure 8. Cont.

Electronics 2021, 10, x FOR PEER REVIEW

Electronics

2021,

10, 1381

Electronics

2021, 10,

x FOR

PEER REVIEW

12 of 17

12 of12

17 of 17

(c) Class‐BD amplifier shown in Figure 5 with extended PSC PWM modulator

Figure 8. Simulated THD + N frequency responses of three tested amplifiers in the band up to 30 kHz.

(c) Class‐BD amplifier shown in Figure 5 with extended PSC PWM modulator

Figure

9 shows

the voltage

oscillograms

measured

atband

the

outputs of the

Figure

8. Simulated

THD

+ N+frequency

responses

of

tested

amplifiers

up

tokHz.

30 kHz.

Figure

8. Simulated

THD

N frequency

responses

ofthree

three

tested amplifiers

inin

thethe

band

upfollowing

to 30

proposed Class‐BD amplifier with the PSC PWM modulator in Figure 5: right half bridge,

Figure

9 shows

thevoltage

voltage

oscillograms

measured

thethe

following

outputs

of the

leftFigure

half

bridge,

DMthe

output,

andoscillograms

CM output before

andatafter

filtration.

We

obtain

quite

9 shows

measured

at

following

outputs

of the

proposed

Class-BD

amplifier

with

the

PSC

PWM

modulator

in

Figure

5:

right

half

bridge,

similar

oscillograms

for

the

Class

BD‐amplifier

with

the

NBDD

modulator

in

Figure

4.

A

proposed Class‐BD amplifier with the PSC PWM modulator in Figure 5: right half bridge,

left half bridge,

DM

output,

and CM

output

before

and after

filtration.

We

obtain

quite

comparison

of

the

output

voltages

on

the

right

half

bridge,

left

half

bridge

and

CM

output,

left similar

half bridge,

DM output,

and CM

output before

andNBDD

after filtration.

We

obtain4.quite

oscillograms

for

the9,Class

BD-amplifier

with the

modulator

in Figure

presented

in

Figures

5

and

shows

that

the

real‐time

waveforms

are

distorted

by over‐

similar

oscillograms

foroutput

the Class

BD‐amplifier

with

the

NBDD

modulator

inand

Figure

A

comparison

of

the

voltages

on

the

right

half

bridge,

left

half

bridge

CM 4. A

lapping spikes on the rising and falling edges of the PWM pulse in each switching period.

comparison

of

the

output

voltages

on

the

right

half

bridge,

left

half

bridge

and

CM

output, presented in Figures 5 and 9, shows that the real-time waveforms are distorted output,

by

The main source of these spikes are timing errors added in each switching period Tc by

presented

in Figures

shows

theedges

real‐time

distorted

by over‐

overlapping

spikes 5onand

the 9,

rising

andthat

falling

of thewaveforms

PWM pulseare

in each

switching

the gate drivers, such as dead time. The inevitability of timing errors is due to the fact that

period.

The main

source

of and

thesefalling

spikesedges

are timing

errors

added

in in

each

switching

period

lapping

spikes

on the

rising

of the

PWM

pulse

each

switching

period.

the turn‐on delay times of the NMOS and PMOS transistors have to be implemented by

Tc

by

the

gate

drivers,

such

as

dead

time.

The

inevitability

of

timing

errors

is

due

to

the

fact

The

main sourceadjusting

of these spikes

aretimes

timing

errors

added

in each

switching

perioddriv‐

Tc by

independently

the of

delay

ofand

the

rising

and falling

edges

of implemented

the PWM

that

the

turn-on

delay

times

the NMOS

PMOS

transistors

have

toisbe

theing

gate

drivers,

such

as

dead

time.

The

inevitability

of

timing

errors

due

to

the

fact

that

Even with

equalthe

turn‐on

times

of the and

NMOS

andedges

PMOS,

during

by signals.

independently

adjusting

delay delay

times of

the rising

falling

of the

PWMthe

thedead

turn‐on

delay

times ofcurrent

the NMOS

PMOS

have

to diode.

be implemented

by

time,

the inductor

in theand

output

LPFtransistors

turns

the

body

During

driving

signals.

Even with

equal turn-on

delay times

of the on

NMOS

and PMOS,

during

thethe

independently

adjusting

the

delay

times

of

the

rising

and

falling

edges

of

the

PWM

driv‐

next

phase

the other

side of

the output

MOSFET

at diode.

the endDuring

of the the

dead

dead

time,when

the inductor

current

in the

LPFstarts

turnstoonturn

the on

body

ingtime,

signals.

Even

with

equal

turn‐on

delay

times

of

the

NMOS

and

PMOS,

during

the

body

diode

stays

in

a

conducting

state

unless

the

stored

minority

carrier

is

fullythe

next phase when the other side of the MOSFET starts to turn on at the end of the dead

dead

time,

the

inductor

current

in

the

output

LPF

turns

on

the

body

diode.

During

discharged.

Thisdiode

reverse

recovery

current tends

to have

a sharp,

spiky shape

andisleads

time, the body

stays

in a conducting

state unless

the

stored minority

carrier

fully tothe

next

phase when

other

side ofcurrent

thespikes

MOSFET

starts

turnfalling

on atshape

the end

of the

unwanted

distortion

by overlapping

onto

the

rising

and

edges

of leads

the

PWM

discharged.

Thisthe

reverse

recovery

tends

have

a to

sharp,

spiky

and

todead

unwanted

distortion

byperiod.

overlapping

spikes

onfiltration

the

rising

and

fallingminority

edges

of carrier

the

pulse

each

switching

However,

the

of

the

appearing

spikes

atPWM

theisCM

time,

theinbody

diode

stays

in a conducting

state

unless

the

stored

fully

pulse

in

each

switching

period.

However,

the

filtration

of

the

appearing

spikes

at

the

CM

output is very

even

when the

filter tends

inductance

L isa very

small,

is shown

the to

discharged.

This easy,

reverse

recovery

current

to have

sharp,

spikyasshape

and in

leads

output isdistortion

very

easy,by

even

when the filter

inductance

L is very

as is

shown

thePWM

oscillogram

in Figure

9. overlapping

unwanted

spikes

on the rising

andsmall,

falling

edges

of in

the

oscillogram in Figure 9.

pulse in each switching period. However, the filtration of the appearing spikes at the CM

output is very easy, even when the filter inductance L is very small, as is shown in the

oscillogram in Figure 9.

(a) Left-half and right-half H-bridge outputs before (left) and after (right) filtration

Figure 9. Cont.

(a) Left-half and right-half H-bridge outputs before (left) and after (right) filtration

Electronics 2021, 10, 1381

13 of 17

Electronics 2021, 10, x FOR PEER REVIEW

13 of 17

(b) Differential Mode output

(c) Common-Mode output

DM

VOUT

DM

VOUT

before (left) and after (right) filtration

before (left) and after (right) filtration

Figure

9. 9.

Ocillograms

outputsofofthe

theClass-BD

Class‐BD

amplifier

in Figure

5: Left-half

(a) Left‐half

and right‐half

Figure

Ocillogramsmeasured

measuredat

at the

the following

following outputs

amplifier

in Figure

5: (a)

and right-half

HH‐bridge

outputs,

(b)

DM

output,

(c)

CM

output

(in

the

left

column

before,

in

the

right

column

after

filtration);

bridge outputs, (b) DM output, (c) CM output (in the left column before, in the right column after filtration); Fc2 = 164

kHz,

; vertically:

1 div/5 V;1 horizontally:

div/5

Fc f2m=

164

f m 10 kHz

10 kHz

kHz;, vertically:

1 div/5

V; horizontally:

div/5 µs; V 1=

24 V.μs ; VDD 24 V .

DD

Figure10

10shows

shows the

the PCBs

PCBs of

of the

balanced

CM

Figure

the tested

testedClass-BD

Class‐BDaudio

audioamplifiers

amplifierswith

with

balanced

CM

® Power MOSFET IRF9389PbF:

output,

implemented

on

complementary

pairs

HEXFET

®

output, implemented on complementary pairs HEXFET Power MOSFET IRF9389PbF: (a)

(a) shown

in Figure

4, using

the extended

NBDD

modulator;

andshown

(b) shown

in

shown

in Figure

4, using

the extended

NBDD

PWMPWM

modulator;

and (b)

in Figure

Figure

5,

using

the

extended

PSC

PWM

modulator.

To

test

a

typical

Class-BD

amplifier

5, using the extended PSC PWM modulator. To test a typical Class‐BD amplifier in a H‐

in a H-bridge configuration with a classic NBDD PWM modulator (as shown in Figure 1

bridge configuration with a classic NBDD PWM modulator (as shown in Figure 1 but with

but with complementary MOSFETs), the main H-bridge of the amplifier in Figure 10a was

complementary MOSFETs), the main H‐bridge of the amplifier in Figure 10a was used.

used. To implement such a configuration, pins: drain-source of M5, M7 transistors should

To implement such a configuration, pins: drain‐source of M5, M7 transistors should be

be galvanically connected, while M6 and M8 should be permanently open. Electronic

galvanically

while

M6 and

M8 should

be permanently

open.

Electronic

components connected,

on PCBs have

the same

symbols

as in Figures

4 and 5. Load

resistances

of 4com‐

Ω,

ponents

on

PCBs

have

the

same

symbols

as

in

Figures

4

and

5.

Load

resistances

of

4 Ω, 65

65 W or 8 Ω, 35 W are attached to PCBs with short cables from the outside.

W or 8The

Ω, following

35 W are attached

to PCBswas

withused

short

the outside.

set of equipment

tocables

test thefrom

amplifiers:

The following set of equipment was used to test the amplifiers:

− Rigol DG1032Z function generator;

− − Rigol

RigolDG1032Z

DSA832E function

spectrumgenerator;

analyzer, 9 kHz ~ 3.2 GHz;

− − Rigol

DSA832E

kHz~~2.9

3.2GHz;

GHz;

Hp 8593

agilentspectrum

spectrum analyzer,

analyzer, 19kHz

− − Hp

8593 agilent

spectrum

analyzer,

1 kHz

~ 2.9

DSO4254B

advanced

digital

oscilloscope

4×

250 GHz;

MHz.

−

DSO4254B advanced digital oscilloscope 4 × 250 MHz.

2021, 10, 1381

OR PEERElectronics

REVIEW

14 of 17 14 of 17

Figure

TheThe

PCBsPCBs

of the of

tested

amplifiers

with

balanced CM

output,

implemented

on complementary

Figure10.10.

theClass-BD

tested audio

Class‐BD

audio

amplifiers

with

balanced

CM output,

imple‐

® Power MOSFET IRF9389PbF: (a) shown in Figure 4, using the extended NBDD PWM modulator; (b) shown

pairs

HEXFET

®

mented on complementary pairs HEXFET Power MOSFET IRF9389PbF: (a) shown in Figure 4, us‐

in Figure 5, using the extended PSC PWM modulator.

ing the extended NBDD PWM modulator; (b) shown in Figure 5, using the extended PSC PWM

modulator.

4. Final Conclusions

Two original open-loop Class-BD audio amplifiers with balanced Common-Mode

4. Final Conclusionsoutputs were described and tested. The output stage of each proposed amplifier includes

the typical Class‐BD

H-bridge with

fouramplifiers

MOSFETs and

four

additionalCommon‐Mode

MOSFET switches that

Two original open‐loop

audio

with

balanced

balance and keep the CM output constant. Each of the amplifiers employs the extended

outputs were described

and

tested.

The

output

stage of

eachand

proposed

amplifier

NBDD

PWM

or PSC

PWM

modulation

scheme

was implemented

onincludes

complementary

®

the typical H‐bridgepower

with four

MOSFETs

and four

additional MOSFET switches that bal‐

MOSFET

pairs: HEXFET

IRF9389PbF.

simulation studies

in SPICE

and experimental

studies

have

shown that the

ance and keep the CM Extensive

output constant.

Each of

the amplifiers

employs

the

extended

proposed

Class-BD

amplifiers

have

almost

the

same

audio

performance

on

the

DM outputs

NBDD PWM or PSC PWM modulation scheme and was implemented on complementary

as the prototype Class BD amplifier with the optimal NBDD modulation and, at the same

power MOSFET pairs: HEXFET® IRF9389PbF.

time, have balanced constant voltage CM outputs, thus enabling the implementation of

Extensive simulation

studies

SPICE and

experimental

studies

have shown

the

the true,

filterlessinClass-BD

amplifiers.

The filtration

of unwanted

spectralthat

components

at

proposed Class‐BD amplifiers have almost the same audio performance on the DM out‐

puts as the prototype Class BD amplifier with the optimal NBDD modulation and, at the

same time, have balanced constant voltage CM outputs, thus enabling the implementation

of the true, filterless Class‐BD amplifiers. The filtration of unwanted spectral components

Electronics 2021, 10, 1381

15 of 17

the DM output of the tested amplifiers is very easy because the frequency spectrum has

no harmonics of the switching frequency, and no IM components around odd multiples

of the switching frequency. Since these amplifiers simultaneously have balanced CM

outputs, with a constant VDD /2 voltage at this output, the output filter can be dramatically reduced, or rather eliminated, while significantly lowering radiative electromagnetic

interference (EMI).

The implementation of the amplifier output stage on complementary MOSFET pairs

is much easier than only on NMOSFET transistors because the gate drivers of all MOSFETs

share a common ground GND1 and are directly driven from the NBDD or PSC PWM

modulator outputs, the gate drivers are powered from the same voltage as the output

stage, and the complementary MOSFET pairs do not need pairs of complementary control

signals. To supply the proposed amplifiers with a voltage of 24 V, i.e., greater than |VGSmax |

(according to the datasheet it is 20 V), it was designed and applied a gate drive circuit

with a level voltage shifter with Zener diode for the control signals that is suitable for

applications with complementary power MOSFETs with the following supply voltage:

VDD < |VGS max + VZ | and VDD < |VDSmax |. This gate drive circuit has also the ability to

control turn-on and turn-off speeds independently for NMOSFET and PMOSFET.

Extensive experimental and simulation studies in SPICE have shown that the proposed

class BD amplifiers have almost the same audio performance on the DM outputs as the

prototype Class-BD amplifier with the optimal NBDD modulation.

The output power and the efficiency versus modulation index M, as well as THD as a

function of the signal frequency, have been tested for two proposed Class-BD amplifiers

and the prototype Class-BD amplifier with the optimal NBDD modulation (Figure 7) for the

two switching frequencies, Fc1 = 328 kHz and Fc2 = 164 kHz, using, with each switching

frequency, two different load resistances: RL = 4 Ω and RL = 8 Ω.

The audio performance on the DM outputs of the three tested amplifiers, for the following:

= 328 kHz, RL = 4 Ω, f m = 1 kHz, M = 0.95;

= 328 kHz, RL = 8 Ω, f m = 1 kHz, M = 0.95;

= 164 kHz, RL = 4 Ω, f m = 1 kHz, M = 0.95;

= 164 kHz, RL = 8 Ω, f m = 1 kHz, M = 0.95;

are as follows:

1.

Prototype Class-BD amplifier with conventional NBDD modulator:

(a)

PL = 61.16 W, η = 97.01%, THD = 0.683%;

(b)

PL = 32.88 W, η = 97.80%, THD = 0.635%;

(c)

PL = 59.48 W, η = 97.37%, THD = 0.102%;

(d)

PL = 32.19 W, η = 98.29%, THD = 0.078%.

2.

Class-BD amplifier shown in Figure 4 with extended NBDD PWM modulator:

(a)

PL = 56.71 W, η = 94.62%, THD = 0.784%;

(b)

PL = 31.01 W, η = 95.02%, THD = 0.742%;

(c)

PL = 56.93 W, η = 97.37%, THD = 0.085%;

(d)

PL = 31.35 W, η = 96.72%, THD = 0.065%.

3.

Class-BD amplifier shown in Figure 5 with extended PSC PWM modulator:

(a)

PL = 57.80 W, η = 95.27%, THD = 0.752%;

(b)

PL = 31.01 W, η = 96.38%, THD = 0.707%;

(c)

PL = 57.16 W, η = 95.76%, THD = 0.071%;

(d)

PL = 30.53 W, η = 97.10%, THD = 0.099%.

Comparing the above listed audio performance on the DM outputs of the three

tested amplifiers, we can see that the proposed Class-BD amplifiers have lower efficiency

of about 1 to 2% than the prototype Class-BD amplifier with the conventional NBDD

modulation, due to higher conduction losses in a greater number of transistor switches in

the output stages. They have also a slightly higher THD of about 0.1% than the prototype

amplifier with the conventional NBDD modulation because they are controlled by extended

(a)

(b)

(c)

(d)

Fc1

Fc1

Fc2

Fc2

Electronics 2021, 10, 1381

16 of 17

modulators, giving more timing errors added by the gate driver in each switching period

Tc . THD of all tested amplifiers is higher by about 0.6% for the higher switching frequency

Fc1 = 328 kHz than for Fc2 = 164 kHz because relative timing errors are greater for shorter

switching period Tc .

Class-BDD amplifiers with CM balanced output can successfully use a not very high

switching frequency (in our design Fc2 = 164 kHz), resulting in higher efficiency and lower

THD, even with a reduced LC output filter.

The proposed open-loop Class-BD audio amplifiers with balanced CM outputs are

true, filterless Class-D amplifiers with significantly reduced electromagnetic radiation

interference (EMI). In practice, due to imperfect waveforms of the voltages controlling the

MOSFET transistors, spike pulses are generated at the CM output of the amplifier, which

are easy to filter by the reduced LC output filter, even at a very low inductance L.

Author Contributions: Conceptualization, W.K., and S.K.; methodology, W.K.; software, W.K. and

J.J.; validation, S.K., and W.K.; formal analysis, W.K.; investigation, W.K. and J.J.; resources, W.K.;

data curation, W.K.; writing—original draft preparation, W.K. and S.K.; writing—review and editing, W.K. and S.K.; visualization, S.K. and W.K.; supervision, S.K.; project administration, W.K.;

funding acquisition, S.K. and W.K. All authors have read and agreed to the published version of

the manuscript.

Funding: This research received no external funding and The APC was funded by the Rector of the

University of Applied Sciences in Tarnów, Poland.

Conflicts of Interest: The authors declare no conflict of interest.

References

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12.

13.

14.

Nielsen, K. A Review and Comparison of Pulse Width Modulation (PWM) Methods for Analog and Digital Input Switching

Power Amplifiers. In Proceedings of the 102nd AES Convention, Munich, Germany, 22–25 March 1997.

Nielsen, K. Parallel Phase Shifted Carrier Pulse Width Modulation (PSCPWM)—A Novel Approach to Switching Power Amplifier

Design. In Proceedings of the 102nd AES Convention, Munich, Germany, 22–25 March 1997.

Jasielski, J.; Kolodziejski, W.; Kuta, S. Cancellation of common-mode output signal in Class-BD audio amplifiers. In Proceedings

of the 2016 International Conference on Signals and Electronic Systems (ICSES), Kraków, Poland, 5–7 September 2016; pp. 167–172.

[CrossRef]

Igarashi, T.; Komine, N.; Taihua, L.; Fukai, Y.; Arai, T.; Sano, Y. New method class D amplifier which enables reduction of RF

noise and signal distortion. In Proceedings of the 10th IEEE International NEWCAS Conference, Montreal, QC, Canada, 17–20

June 2012; pp. 265–268.

Cox, S.M.; Yu, J.; Goh, W.L.; Tan, M.T. Intrinsic Distortion of a Fully Differential BD-Modulated Class-D Amplifier with Analog

Feedback. IEEE Trans. Circuits Syst. I: Regul. Pap. 2012, 60, 63–73. [CrossRef]

Chien, S.-H.; Wu, L.-T.; Chen, S.-Y.; Jan, R.D.; Shih, M.Y.; Lin, C.T.; Kuo, T.H. An Open-Loop Class-D Audio Amplifier with

Increased Low-Distortion Output Power and PVT-Insensitive EMI Reduction. In Proceedings of the IEEE Custom Integrated

Circuits Conference, San Jose, CA, USA, 15–17 September 2014.

Siniscalchi, P.; Hester, R.K. A 20 W/Channel Class-D Amplifier with Near-Zero Common-Mode Radiated Emissions. IEEE J.

Solid-State Circuits 2009, 44, 3264–3271. [CrossRef]

Quek, Y.B. Class-D LC Filter Design, Texas Instruments, Application Report, SLOA119A–April 2006–Revised January 2008.

pp. 1–19. Available online: https://www.ti.com.cn/cn/lit/pdf/sloa119 (accessed on 8 June 2021).

Guanziroli, F.; Bassoli, R.; Crippa, C.; Devecchi, D.; Nicollini, G. A 1 W 104 dB SNR Filter-Less Fully-Digital Open-Loop Class D

Audio Amplifier with EMI Reduction. IEEE J. Solid-State Circuits 2012, 47, 686–698. [CrossRef]

Ikriannikov, A.; Wilson, N. New concept for Class D audio amplifiers for lower cost and better performance. IEEE Trans. Consum.

Electron. 2011, 57, 1218–1226. [CrossRef]

Midya, P.; Roeckner, W.J. Filterless Class D Amplifiers: Power-Efficiency and Power Dissipation. IET Circuits Devices Syst. 2010, 4,

48–56.

Teplechuk, M.A.; Gribben, A.; Amadi, C. True Filterless Class-D Audio Amplifier. IEEE J. Solid-State Circuits 2011, 46, 2784–2793.

[CrossRef]

Berkhout, M.; Dooper, L. Class-D Audio Amplifiers in Mobile Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2010, 57,

992–1002. [CrossRef]

Hwang, Y.S.; Shen, J.H.; Chen, J.J.; Fan, M.R. Performance comparison of integrated fully-differential filterless Class-D am-plifiers

with different feedback techniques. Analog Integr. Circuits Signal Process. 2013, 76, 167–177. [CrossRef]

Electronics 2021, 10, 1381

15.

16.

17 of 17

Jasielski, J.; Kuta, S. Applied methods of power supply and galvanic isolation of gate drivers of power transistors in bridging end

stages of Class D amplifiers and inverters. Sci. Technol. Innov. 2018, 2, 31–41. [CrossRef]

Park, S.; Jahns, T. A Self-Boost Charge Pump Topology for a Gate Drive High-Side Power Supply. IEEE Trans. Power Electron.

2005, 20. [CrossRef]