8086/8088 Architecture: Intel Microprocessor History & Organization

advertisement

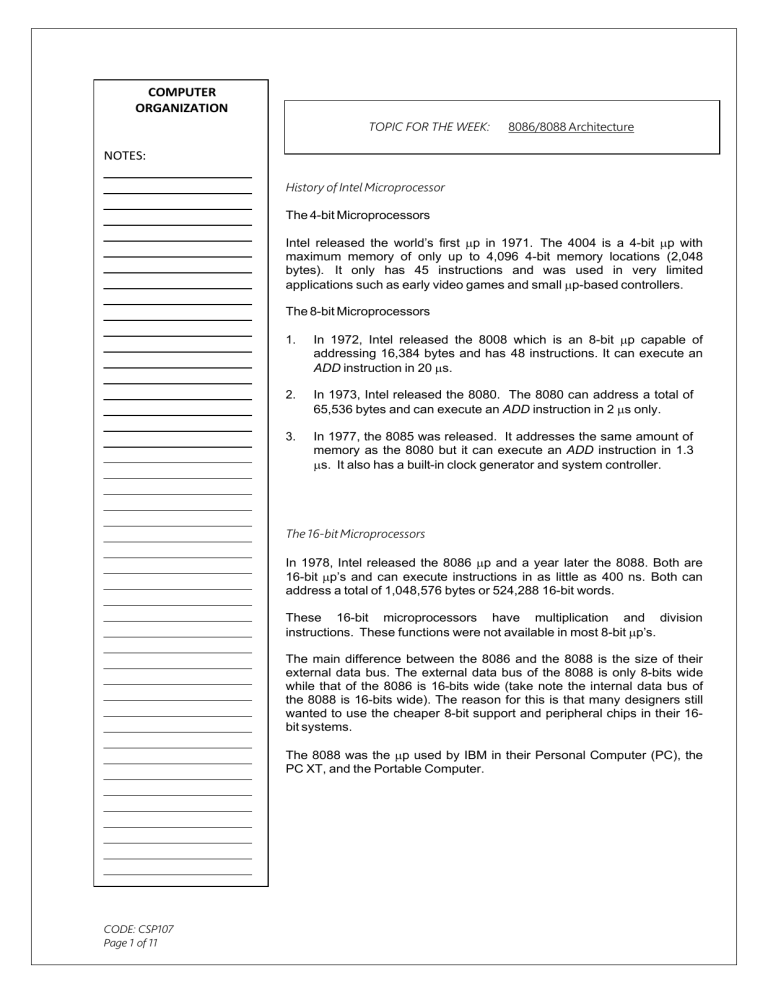

COMPUTER ORGANIZATION TOPIC FOR THE WEEK: 8086/8088 Architecture NOTES: History of Intel Microprocessor The 4-bit Microprocessors Intel released the world’s first p in 1971. The 4004 is a 4-bit p with maximum memory of only up to 4,096 4-bit memory locations (2,048 bytes). It only has 45 instructions and was used in very limited applications such as early video games and small p-based controllers. The 8-bit Microprocessors 1. In 1972, Intel released the 8008 which is an 8-bit p capable of addressing 16,384 bytes and has 48 instructions. It can execute an ADD instruction in 20 s. 2. In 1973, Intel released the 8080. The 8080 can address a total of 65,536 bytes and can execute an ADD instruction in 2 s only. 3. In 1977, the 8085 was released. It addresses the same amount of memory as the 8080 but it can execute an ADD instruction in 1.3 s. It also has a built-in clock generator and system controller. The 16-bit Microprocessors In 1978, Intel released the 8086 p and a year later the 8088. Both are 16-bit p’s and can execute instructions in as little as 400 ns. Both can address a total of 1,048,576 bytes or 524,288 16-bit words. These 16-bit microprocessors have multiplication and division instructions. These functions were not available in most 8-bit p’s. The main difference between the 8086 and the 8088 is the size of their external data bus. The external data bus of the 8088 is only 8-bits wide while that of the 8086 is 16-bits wide (take note the internal data bus of the 8088 is 16-bits wide). The reason for this is that many designers still wanted to use the cheaper 8-bit support and peripheral chips in their 16bit systems. The 8088 was the p used by IBM in their Personal Computer (PC), the PC XT, and the Portable Computer. CODE: CSP107 Page 1 of 11 COMPUTER ORGANIZATION Basic 8086/8088 Architecture EU BIU NOTES: Figure 1. A Sample Diagram of 8086/8088 Architecture Bus Interface Unit (BIU). This is responsible for fetching an instruction, the operand of an instruction or data from the MM. The bus interface unit is the part of the CPU that interfaces with the rest of the PC. Its name comes from the fact that it deals with moving information over the processor data bus, the primary conduit for the transfer of information to and from the CPU. It has bus controller that is responsible for responding to all signals that go to the processor, and generating all signals that go from the processor to other parts of the system. Specifically, it has the following functions: ▪ instruction fetch ▪ instruction queuing ▪ operand fetch and storage ▪ address relocation ▪ bus control The BIU is also responsible for generating bus control signals such as those for memory read or write and I/O read or write. These signals are needed for control of the circuits in the memory and I/O subsystems. Instruction Pointer (IP). This is the program counter. Prefetch Queue. The 8086/8088 prefetches the succeeding instructions while executing the current one. The prefetch queue simply acts as a buffer between the instruction register and the bus controller. This unit helps improve system performance by eliminating some conflicts for the bus (bus contention). Execution Unit (EU). This is responsible for executing the instructions. The execution unit is responsible for decoding and executing all instructions. It consists of an ALU, status and control flags, eight generalpurpose registers, temporary registers, and queue control logic. CODE: CSP107 Page 2 of 11 The EU extracts instructions from the top of the queue in the BIU, decodes them, generates operand addresses if necessary, passes them to the BIU and requests it to perform the read or write bus cycles to memory or I/O, and performs the operation specified by the instruction on the operands. COMPUTER ORGANIZATION NOTES: During execution of the instruction, EU tests the status and control flags and updates them based on the results of executing the instruction. If the queue is empty, the EU waits for the next instruction byte to be fetched and shifted to the top of the queue. When the EU executes a branch or jump instruction, it transfers control to a location corresponding to another set of sequential instructions. Whenever this happens, the BIU automatically resets the queue and then begins to fetch instructions from this new location to refill the queue. 8086/8088 Bus Structure Address Bus A0 to A19 Data Bus D0 to D15 8086 System Control Bus To Memory and I/O RD, WR, M/IO A0 to A19 Address Bus To Memory and I/O D0 to D7 8088 System Data Bus RD, WR, IO/M Control Bus Figure 2. The Bus Structure of 8086/8088 Architecture The M/IO’ (or IO/M’) signal is for selecting the memory or I/O of the system. If it is logic 0, then memory is selected; if it is logic 1, I/O is selected. Logical Memory Logical memory is the memory viewed by the programmer. FFFFFH FFFFEH FFFFDH 1M Bytes 00002H 00001H 00000H CODE: CSP107 Page 3 of 11 Figure 3. Logical Memory Map COMPUTER ORGANIZATION NOTES: It starts at memory location 00000H and extends to location FFFFFH. The logical memory is 8 bits wide. A 16-bit word of memory begins at any byte address and extends for two consecutive bytes. For example, the word at location 00122H is stored at byte 00122H and 00123H with the least significant byte stored in location 00122H. Physical Memory The physical memory is the actual organization of the memory that the hardware designers see. The physical memory map of the 8088 is identical to its logical memory map. Odd Bank Even Bank FFFFFH FFFFEH FFFFCH FFFFAH FFFFDH FFFFBH 512 K Bytes 512 K Bytes 00005H 00004H 00002H 00003H 00001H 00000H 16 bits Figure 4. The Physical Memory Map The physical memory of the 8086 contains two banks of memory. The advantage of this organization is that the 8086 can read or write a 16-bit word in one operation (provided the addresses of the data are even). The 8088 requires two reads or writes to transfer 16 bits of data. Dedicated and General Use of Memory Addresses 00000H to 00013H (20 memory locations) are dedicated while addresses 00014H to 0007FH (108 memory locations) are reserved. • These 128 bytes or memory locations are used for storage or pointers to interrupt service routines. Addresses FFFF0H to FFFFBH (12 memory locations) are dedicated for functions such as storage of the hardware reset jump instruction. Addresses FFFFCH to FFFFFH (4 memory locations) are reserved for use with future products. CODE: CSP107 Page 4 of 11 COMPUTER ORGANIZATION Register Structure of the 8086/8088 All forms of programming depend upon a clear understanding of the internal register structure of the p. NOTES: 8 Bits 8 Bits AH BH AL BL AX BX Accumulator Base CH DH CL DL CX DX Count Data SP Stack Pointer BP Base Pointer SI Source Index DI IP Destination Index Instruction Pointer General Purpose Register CS Code Segment DS Data Segment SS Stack Segment Extra Segment ES Pointer and Index Registers Segment Registers Flags 16 Bits Figure 5. Hierarchy of the Registers in 8086/8008 General Purpose Registers General Purpose Registers. These are used in any manner that the programmer wishes. Each is addressable as a 16-bit register (AX, BX, CX, DX) or as two 8-bit registers (AH, AL, BH, BL, CH, CL, DH, and DL). CODE: CSP107 Page 5 of 11 1. AX (Accumulator). This is often used to hold temporary result after an arithmetic and logic operation. 2. BX (Base). This is often used to hold the base address of data located in the memory. 3. CX (Count). This holds the count for certain instructions such as shift count (CL) for shifts and rotates, the number of bytes (CX) operated upon by the repeated string instructions, and a counter (CX) with the LOOP instruction. 4. DX (Data). This holds the most significant part of the product after a 16-bit multiplication and the most significant part of the dividend before a division. COMPUTER ORGANIZATION NOTES: Pointer and Index Registers Pointer and Index Registers. Although the pointer and index registers are also general purpose in nature, they are more often used to index or point to the memory location holding the operand data for many instructions. 1. SP (Stack Pointer). This is used to address data in a LIFO (last-in first-out) stack memory. This occurs most often when the PUSH and POP instructions are executed. 2. BP (Base Pointer). This is often used to address an array of data in memory. 3. SI (Source Index). This is used to address source data indirectly for use with string instructions. 4. DI (Destination Index). This is normally used to address destination data indirectly for use with the string instructions. Status Register or Processor Status Word Status Register or Processor Status Word. This contains 16 bits, but 7 of them are not used. Each bit in the PSW is a flag. These flags are divided into the conditional flags (they reflect the result of the previous operation involving the ALU) and the control flags (they control the execution of special functions). The conditional flags are: CODE: CSP107 Page 6 of 11 1. Sign Flag (SF) - b7 This is equal to the MSB of the result of the previous operation. 0 if positive, 1 if negative. 2. Zero Flag (ZF) - b6 This is set to 1 if the result of the previous operation is zero and 0 if the result is nonzero. 3. Parity Flag (PF) - b2 This is set to 1 if the low-order 8 bits of the result of the previous operation contain an even number of 1s. Otherwise, it is reset to 0. COMPUTER ORGANIZATION Conditional Flags (cont…) 4. NOTES: Carry Flag (CF) - b0 An addition causes this flag to be set to 1 if there is a carry out of the MSB, and a subtraction causes it to be set to 1 if a borrow is needed. 5. Overflow Flag (OF) - b11 This is set to 1 if an overflow occurs, i.e., a result is out of range. More specifically, for addition this flag is set to 1 when there is a carry into the MSB and no carry out of the MSB or vice-versa. For subtraction, it is set to 1, when the MSB needs to borrow and there is no borrow from the MSB, or vice-versa. 6. Auxiliary Carry Flag (AF) - b4 This flag is used exclusively for BCD arithmetic. It is set to 1 if there is a carry out of bit 3 (b3) during an addition or borrow by bit 3 during a subtraction. Example 1 1. + 0010 0011 0100 0101 0011 0010 0001 1001 0101 0101 0101 1110 SF = 0 ZF = 0 PF = 0 CF = 0 AF = 0 OF = 0 In this example, the sign flag (SF) is 0 since the MSB is 0, the zero flag (ZF) is 0 since the result is nonzero, the parity flag (PF) is 0 since the low-order 8 bits or the first 8 bits from the least significant bit (LSB) has odd number of ones, the carry flag (CF) is 0 since there is no carry out of the most significant bit (MSB), the auxiliary flag (AF) is 0 since there is no carry out of bit 3 and overflow flag (OF) is 0 since there is no carry into the MSB and no carry out of the MSB. 2. + 0101 0100 0011 1001 0100 0101 0110 1010 1001 1001 1010 0011 SF = 1 ZF = 0 PF = 1 CF = 0 AF = 1 OF = 1 In this example, the sign flag (SF) is 1 since the MSB is 1, the zero flag (ZF) is 0 since the result is nonzero, the parity flag (PF) is 1 since the low-order 8 bits or the first 8 bits from the least significant bit (LSB) has even number of ones, the carry flag (CF) is 0 since there is no carry out of the most significant bit (MSB), the auxiliary flag (AF) is 1 since there is a carry out of bit 3 (b3) and overflow flag (OF) is 1 since there is a carry into the MSB and no carry out of the MSB. CODE: CSP107 Page 7 of 11 COMPUTER ORGANIZATION Example 2 1. 0101 0100 0011 1001 + NOTES: SF = 1 0100 0101 0110 1010 1001 1001 1010 0011 ZF = 0 PF = 1 CF = 0 AF = 1 OF = 1 In this example, the sign flag (SF) is 1 since the MSB is 1, the zero flag (ZF) is 0 since the result is nonzero, the parity flag (PF) is 1 since the low-order 8 bits or the first 8 bits from the least significant bit (LSB) has even number of ones, the carry flag (CF) is 0 since there is no borrow by the most significant bit (MSB), the auxiliary flag (AF) is 1 since there is a borrow by bit 3 (b3) and overflow flag (OF) is 1 since there is a borrow by the MSB and no borrow from the MSB. 2. + SF = 0 0001 0010 0011 0100 0100 1010 1110 0000 0101 0101 0001 0100 ZF = 0 PF = 0 CF = 0 AF = 0 OF = 0 In this example, the sign flag (SF) is 1 since the MSB is 1, the zero flag (ZF) is 0 since the result is nonzero, the parity flag (PF) is 0 since the low-order 8 bits or the first 8 bits from the least significant bit (LSB) has odd number of ones, the carry flag (CF) is 1 since there is a borrow by the most significant bit (MSB), the auxiliary flag (AF) is 0 since there is no borrow by bit 3 (b3) and overflow flag (OF) is 0 since there is a borrow by the MSB and a borrow from the MSB. Example 3 Perform the following arithmetic operation and determine the state of the conditional flags. 1. 2. 70A3H + E757H FE58H + 01A8H The first thing to do is to convert the given hexadecimal numbers to their equivalent binary values (disregard the letter H; it only refers to the number system used which is hexadecimal). Then, perform the indicated arithmetic operation. After that, determine the values of the conditional flags. CODE: CSP107 Page 8 of 11 COMPUTER ORGANIZATION Exercises Perform the following arithmetic operation and determine the state of the conditional flags. NOTES: 1. 2. 3. AA45H + 4678H 234FH + 34CDH + SF = 0 0110 0010 1010 0000 1001 1101 0110 0000 0000 0000 0000 0000 ZF = 1 PF = 1 CF = 1 AF = 0 OF = 0 The first thing to do is to convert the given hexadecimal numbers to their equivalent binary values (disregard the letter H; it only refers to the number system used which is hexadecimal). Then, perform the indicated arithmetic operation. After that, determine the values of the conditional flags. Control Flags The control flags are: 1. Direction Flag (DF) - b10 This flag is used by string manipulation instructions. If clear, the string is processed from its beginning with the first element having the lowest address. Otherwise, the string is processed from the high address towards the low address. 2. Interrupt Enable Flag (IF) - b9 If set, a certain type of interrupt (a maskable interrupt) can be recognized by the CPU; otherwise, these interrupts are ignored. 3. Trap Flag (TF) - b8 If set, the 8086/8088 will enter into a single-step mode. In this mode, the CPU executes one instruction at a time. CODE: CSP107 Page 9 of 11 COMPUTER ORGANIZATION Segment Registers and Memory Segmentation Even though the 8086/8088 has a 1MB memory address space, not all this memory can be active at any one time. NOTES: 64 KB Segment Base Address The MM can be partitioned into 64K (65,536) byte segments where each segment represents an independently addressable unit of memory consisting of 64K consecutive byte-wide storage locations. Each segment is assigned a base address that identifies its starting point, that is, its lowest-addressed byte storage location. Generating a Memory Address A logical address in the 8086/8088 is identified by a segment (its base address) and an offset. The offset identifies the distance in bytes that the storage location of interest resides from this starting address. . . . Data Offset 64 KB Segment . . . Base Address Both segment base address and offset are 16 bits long. Therefore, the lowest-addressed byte in a segment has an offset of 0000H and the highest-addressed byte has an offset of FFFFH. However, the physical addresses that are used to access memory are 20 bits long. The generation of the physical address involves combining a 16-bit offset value and a 16-bit segment base address value that is shifted-left by 4 bits with its LSB’s being filled with 0s. CODE: CSP107 Page 10 of 11 COMPUTER ORGANIZATION Example 1 Determine the physical address of the following: NOTES: 1. Segment Base Address = 1234H Offset Address = 0022H Computing for the physical address is just getting the sum of the physical segment base address and the offset address. The physical segment base address is the segment base address shifted 4 bits to the left or simply appends 0 before the least significant bit (LSB). If the segment base address is 1234H then the physical segment base address is 12340H. + Physical Segment Base Address Offset Address Physical Address 12340H + 0022H = 12362H Note: Remind the students that hexadecimal addition is different from the usual addition process. The students may convert the given hexadecimal values to binary numbers first and then perform the addition process and then convert it back to the hexadecimal notation. Take note that the offset address is sometimes called the effective address. Logical addresses are often written following the segment base address:offset format. Example: 1234H:0022H Example 2 2. Segment Base Address = 123AH Offset Address = 341BH Computing for the physical address: + Physical Segment Base Address Offset Address Physical Address = 123A0H = 341BH = 157BBH Exercise Determine the physical address of the following addresses: 1. Segment Base Address = 4321H Offset Address = 1266H 2. Segment Base Address = ABCDH Offset Address = 3623H 3. Segment Base Address = AE6DH Offset Address = 43A1H CODE: CSP107 Page 11 of 11