OptimalSlopeCompensationforsteploadinpeakcurrentcontrolleddc-dcBuckConverter conf

advertisement

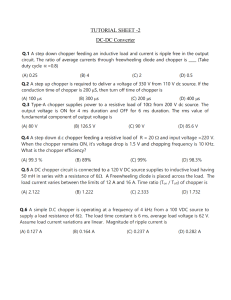

See discussions, stats, and author profiles for this publication at: https://www.researchgate.net/publication/224331347 Optimal Slope Compensation for step load in peak current controlled dc-dc Buck Converter Conference Paper · October 2008 DOI: 10.1109/EPEPEMC.2008.4635313 · Source: IEEE Xplore CITATIONS READS 10 2,742 4 authors: Susovon Samanta Pradipta Patra National Institute of Technology Rourkela Samsung 31 PUBLICATIONS 684 CITATIONS 6 PUBLICATIONS 271 CITATIONS SEE PROFILE SEE PROFILE Siddhartha Mukhopadhyay Amit Patra Indian Institute of Technology Kharagpur Indian Institute of Technology Kharagpur 69 PUBLICATIONS 362 CITATIONS 209 PUBLICATIONS 2,995 CITATIONS SEE PROFILE Some of the authors of this publication are also working on these related projects: Power Electronics Design for PV based system View project M.Tech Thesis View project All content following this page was uploaded by Susovon Samanta on 14 July 2016. The user has requested enhancement of the downloaded file. SEE PROFILE Optimal Slope Compensation for step load in peak current controlled dc-dc Buck Converter Susovon Samanta*, Pradipta Patra†, Siddhartha Mukhopadhyay* and Amit Patra* * IIT Kharagpur/Electrical Engg., Kharagpur, India, e-mail: (susovon, smukh, amit)@ee.iitkgp.ernet.in † IIT Kharagpur/ATDC, Kharagpur, India, e-mail: pradipta@vlsi.iitkgp.ernet.in Abstract— The paper comes up with the variation of slope compensation with step load and duty cycle for one cycle control in a peak current controlled dc-dc buck converter. For an optimal performance under varying load conditions and input voltage the amount of slope compensation desired, vary dynamically. A conventionally used linear slope is definitely not a solution. To meet the dynamic requirement of slope in a current controlled dc-dc buck converter a nonlinear ramp generator circuit has been proposed. The primary aim of the circuit is to provide a slope which is very small for low duty cycles and increases steeply as duty cycle increases. Consequently, it proves much more efficient in low duty cycle (less than 0.5) of operation. On the higher side this achieves a similar performance as that by a linear ramp with much less p-p value of the ramp. Keywords— Power management, Voltage Regulator Modules, Automotive application, Switched-mode power supply, Converter control. I. INTRODUCTION With the growing need for consumer applications, the urge for dc-dc converters is also on the rise. Considering high performance, increased efficiency and stability dc-dc switching converters are incorporated. There are primarily two control methods for PWM DCDC switching converter, voltage mode and current mode. The voltage mode control has the disadvantage of a small frequency bandwidth. The inductor and the capacitor at the output , which forms a low pass filter, introduce 180˚ phase shift at the self-resonant frequency; fLC =1/2ɩ¥LC. This requires a gain of the control loop less than unity at fLC to guarantee stability. The result is a slow response in the output voltage [5-6]. However the current control can realize a large frequency bandwidth. Two loops are required in this configuration: the conventional voltage control loop and the current control loop. Though circuits become complicated and current sensing becomes a challenge it is possible to extend the bandwidth up to half the switching frequency [1]. In order to ensure stability in a current controlled dc-dc switcher with duty cycles more than 0.5, slope compensation (Mc) has to be introduced [5-6]. The amount of slope compensation is important because it affects both on stability and the frequency bandwidth [1]. This value of Mc significantly affects the frequency bandwidth of the system. With a higher value of slope the bandwidth decreases which dampens the dynamic response of the system. For systems which are limited by duty cycles, very common in commercial chips, there is a definite need for high value of ramp [ref]. The value of such a slope also varies depending on the duty cycle of the operating condition, the load step and the gain of the error amplifier [2] [4]. Thus, a dynamically changing value of Mc is needed which is only possible using a dynamically changing ramp [3]. This paper comes up with results which show the effects on the optimal Mc value for different load steps and different duty cycles. The contribution of the error amplifier gain factor on Mc is also analyzed into and design of a PI based compensator accounted for. Finally, the advantages of using non linear slope compensation over linear slope compensation for varying duty cycle and load currents, has been put forth. The implementation of the non-linear slope compensation has also been discussed. II. CURRENT MODE CONTROL FOR DC-DC CONVERTERS In the current-mode control, the duty ratio of the converter is determined by the time taken by the inductor current to reach a threshold value defined by the reference control signal. Fig1 shows a fixed frequency current-mode PWM buck converter. It contains two feedback loops, an outer one which senses the output voltage and develops a control signal to an inner loop which senses the current flowing through the sense resistance series with the inductor, and keeps the output voltage constant on a pulseby-pulse basis. The major drawback of the current-mode PWM scheme is its instability for duty ratio exceeding 0.5. Fig. 1.Current controlled DC-DC Buck Converter 485 c 2008 IEEE 978-1-4244-1742-1/08/$25.00 III. OPTIMAL SLOPE COMPENSATION FOR ONE CYCLE CONTROL OF A PEAK CURRENT CONTROLLED DC-DC amplifier gain. The figure Fig2 illustrates the operation of the outer loop. CONVERTER A. Why optimal slope compensation for one cycle control - a discussion To apply slope compensation for a current controlled buck converter many of the system parameter needs to be concentrated on so as to get the best dynamic performance of the system. The prime consideration in determining the value of Mc is the duty ratio of the operating condition which finally depends on the input and output voltage variation of the system. The following sections would go into the details of such variation of the slope compensation value required for different duty cycles. With different step loads in steady state condition the requirement of the value of the Mc changes quite unlikely to the theoretical Mc=M2 (for one cycle control, where M2 is the slope of the falling inductor current)or Mc = M2/2 (for stability consideration) [5-6]. Usually, for one cycle control, at high duty ratio, the system requires much more slope compensation than the theoretical values and it depends on the load step as detailed out in Table2. Finally, the gain of the compensator is a serious concern at high frequency as a step change is a high frequency effect. The gain directly affects the control signal (vc) which effects Mc consequently. So, when it comes to an optimal selection of Mc for one cycle control all the above issues comes into concern. An optimal transient performance with a step load can be characterized by the following effects. • One cycle control which ensures that the inductor current reaches its initial value in one cycle • Duty ratio in the transient state should never go beyond 1 • Applying a very high value of Mc the system will more oscillate. Thus a fixed linear ramp cannot be a solution to all these issues. From Fig2 the instantaneous change in vc due to the step load changes can be calculated as; Change in output voltage Dvout = RESR · I load Change in feedback voltage ª R2 º D v fb = K v out « K = » R1 + R 2 ¼ ¬ DvC = g m · (Rout Rc )·Dv fb = g m · (Rout Rc )· K Dvout Dvc = g m · (Rout Rc )· K · RESR · I load The gain of the error amplifier in high frequency should be nominal, preferably negative. However such a gain depends on the gain of the error amplifier and the parameters of the PI controller and the values which cannot be arbitrarily chosen. Effects of some parameter changes to the system response to achieve a lower value of Mc can be summarized as follows. 1. The value of the Rc of the PI can be made equal to zero so as to achieve a low high frequency gain of the error amplifier which in turns makes the system oscillatory due to double pole. 2. Maintaining the zero within the converter resonant frequency if the Rc and Cc have to be adjusted. Decreasing the Rc value would decrease the gain of the system. This in turn makes the system less sensitive to the change in control signal so the settling time increases. Accordingly the value of Rc has to be chosen such that it incorporates a system gain. This in turn accounts for a greater Mc B. Effect of control signal on slope compensation If a step is applied to the load in steady state condition, the control signal (vc) value too gets a step. This is due to the effect of the ESR of the output capacitance, of the converter, and the amplitude of the load step which is then divided by the voltage divider and amplified by the error Fig. 2. ESR effects on control signal during load step 486 TABLE I. PARAMETER VALUES OF THE CONVERTER Vg(V) V0(V) Rload(ȍ) L(H) C(F) Resr(ȍ) 4 - 10 Gm(mho) 1300μ 3.3 Rout(ȍ) 100k 10 Rc(ȍ) 20k 22μ Cc(μ) 4.7n 60μ Rsense(ȍ) 0.08 30m Fs(Hz) 600k 2008 13th International Power Electronics and Motion Control Conference (EPE-PEMC 2008) Fig3 shows the ac plots, for a converter with parameters as is tabulated in Table1, of the error amplifier with the zero of PI constant though the high frequency gain is varied simultaneously. But decreasing the gain of the amplifier makes the system response sluggish as shown in Fig4. When it comes to the design of an on-chip current controlled converter for duty cycles higher than 0.5, selecting the value of the compensating slope becomes a real challenge. Quite contrary to theory Mc=M2 is unable to stabilize the system in one cycle. As has already been discussed apart from the duty cycle the amount of the load step also poses a significant effect on the amount of the compensating slope required for the optimal performance of the converter in the steady state condition. Thus, literally speaking for optimal operation of the converter different values of Mc is needed based on operating condition. This however is not quite achievable with a fixed linear slope which can only be designed to meet the worst case condition for a converter. It not only hinders the optimal performance of the converter but also degrades the system performance at different operating conditions, may be the typical condition also. Based on the above stated analysis on the values of Mc a non-linear ramp can be much worthwhile as compared to its linear counterpart for optimal system performance. Some significant advantages can be • Fig. 3. AC response for different PI’s • • A low value of Mc for very low duty cycles which does not unnecessarily makes the system sluggish as with a fixed linear slope which offers the same mc for all duty cycles. A non-linear ramp can be designed based on the optimal values of the Mc for different operating conditions and the curve obtained is more likely to give an optimal value for its corresponding operating condition. There is no such option for a fixed linear ramp. Last but not the least, the p-p value of such a non-linear will definitely be much less than a fixed linear slope. V. DESIGN OF NON LINEAR SLOPE Fig5 shows the proposed slope compensation generation circuit for a standard current controlled dc-dc buck converter. The voltage Vsense gives the non-linear ramp which is added to the current sense in the similar manner as a linear slope ramp is added before it is compared to the compensated error signal from the outer voltage loop. Fig4: Output response at step load for different gain in error amplifier Consequently to achieve a good dynamic system response we have to compromise with some amount of gain in the compensator which instead makes for higher and varying values of Mc under different operating conditions and different steps as in Table2. IV. ADVANTAGES OF NON LINEAR SLOPE COMPENSATION OVER LINEAR SLOPE COMPENSATION Fig5: Slope Compensation Circuit The slope compensation circuit described in Fig5 consists of M1, M2, a constant bias current Is, two capacitances C1 and C2, and three switches Sw1, Sw2 and 2008 13th International Power Electronics and Motion Control Conference (EPE-PEMC 2008) 487 Sw3. Is is a fixed current source and the slope produced by Is and the combination of C1 and C2 at different time instant is relatively precise. The switching operations of the capacitors must be synchronized with the system clock. With the turning ON of the high side switch S3 turns ON. Consequently the node voltage of Ns is defined by the charging of the capacitors C1 and C2 in parallel. Thus, S1 turns ON to discharge C1. The final part is defined by the switching ON of C1 only. The voltage at the node is due to the charging of C1. Thus maintaining a small value of C1 and a high value of C2 the rate of change of voltage at the node is small when both the capacitors are in parallel than when only C1 is charged. The voltage drop at that node will be linear with respect to supply with two different slopes for the two different charging patterns. The intention of such a slope is to maintain a low slope for low duty cycles and an exponential may be, as the duty cycle increase. This linear voltage change is applied to the gate of M2. As M1 and M2 are mirrored then they would try to maintain the same Vgs. As the node voltage decreases the Vg tends to decrease to maintain the same Vgs. Thus the Vgs across M2 increases. As a result a current with square relationship with time flows in M2 and is converted to square voltage of the resistor Rs. Finally the voltage Vsense serves as the ramp for the converter. Fig 6. Response at constant d and varying load VI. SIMULATION RESULTS Based on the parameters of the current controlled converter tabulated in Table1 the dynamic p-p values of Mc were obtained as in Table2 which give the optimal performance. The corresponding operation of the converter at a constant duty cycle with different load steps has been figured out in Fig6. TABLE II. DYNAMIC VALUE OF P-P MC Duty Cycle 0.4 0.5 0.6 0.7 0.8 15 N.A. 50mV 55mV 60mV 75mV Load Step (%) 30 50 N.A. 80mV 60mV 100mV 70mV 130mV 120mV 170mV 160mV 310mV 70 150mV 175mV 190mV 250mV 620mV 90 280mV 325mV 365mV 420mV 1.7V Consequently the transient optimal response of the converter, as from the values of Mc in Table2, with a load step of 50% over a range of duty cycles in plotted in Fig7. Finally, to account for the advantage of using a non-linear ramp over a linear ramp has been brought forward by Fig8. However for high duty cycles non-linear slope achieves a similar performance even with much smaller pp value. The transient response at 0.8 duty cycle and 50% load step with a non-linear ramp of about half the peak of linear ramp is shown in Fig9. However for high duty cycles non-linear slope achieves a similar performance even with much smaller p-p value. The transient response at 0.8 duty cycle and 50% load step with a non-linear ramp of about half the peak of linear ramp is shown in Fig9. 488 Fig7: Response at constant load and varying d Fig8: Output Comparison with linear and non linear compensation at d=0.4 2008 13th International Power Electronics and Motion Control Conference (EPE-PEMC 2008) Fig9: Output Comparison with linear and non linear compensation at d=0.8 VII. CONCLUSION The variation of Mc has been analyzed into with the amount of load disturbance and the changing duty cycle with the change in input and/or output of the system. It can thus be inferred that dynamic slope compensation is of utmost importance to tackle dynamic conditions for a current controlled converter and for one cycle control. Designing a conventional linear ramp is an overdoing it. Based on the values of Mc for optimal performance of the system a non linear ramp generation circuit has been developed and its performance compared with that of the linear one. Such a ramp would deeply improve the performance of peak current controlled converters. ACKNOWLEDGMENT The authors would like to express their gratitude to the members of Advanced VLSI Design Lab, IIT Kharagpur who have been always on their toes in times of need REFERENCES [1] [2] [3] [4] [5] [6] 1. Tan F.Dong, “Current-Loop Gain with a Nonlinear Compensating Ramp.” Power Electronics Specialists Conference, IEEE, Vol. 1., June 1996. 2. Choi B., “Step Load Response of a Current-Mode-Controlled DC-to-DC Converter.” IEEE Transactions on Aerospace and Electronic Systems, Vol.33, No.4, October 1997. 3. Sakurai H. and Sugimoto Y, “Analysis and Design of a CurrentMode PWM Buck Converter Adopting the Output-Voltage Independent Second-Order Slope Compensation Scheme” IEICE Transaction Fundamentals, Vol.E88-A, No.2 February 2005. 4. Redl. R, Erisman B and Zansky Z, “Optimizing the Load Transient Response of the Buck Converter.” Applied Power Electronics Conference and Exposition, IEEE, 1998. 5. Erickson Robert W. and Maksimovic Dragan., “Fundamentals of Power Electronics.” Kluwer Academic Publishers Group Distribution Centre. 6. Abraham I. Pressman, “Switching Power Supply Design”, McGraw-Hill. 2008 13th International Power Electronics and Motion Control Conference (EPE-PEMC 2008) View publication stats 489