The Atmel AVR Microcontroller MEGA and XMEGA in Assembly and C (Han-Way Huang) (z-lib.org)

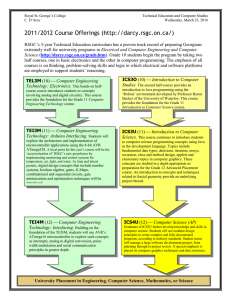

advertisement

The Atmel AVR

Microcontroller:

Mega and XMega in Assembly and C

Han-Way Huang

Minnesota State University • Mankato

Australia • Brazil • Japan • Korea • Mexico • Singapore • Spain • United Kingdom • United States

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

This is an electronic version of the print textbook. Due to electronic rights restrictions,

some third party content may be suppressed. Editorial review has deemed that any suppressed

content does not materially affect the overall learning experience. The publisher reserves the right

to remove content from this title at any time if subsequent rights restrictions require it. For

valuable information on pricing, previous editions, changes to current editions, and alternate

formats, please visit www.cengage.com/highered to search by ISBN#, author, title, or keyword for

materials in your areas of interest.

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

The Atmel AVR Microcontroller: Mega

and XMega in Assembly and C

Han-Way Huang

Vice President, Editorial: Dave Garza

Director of Learning Solutions: Sandy Clark

Acquisitions Editor: Stacy Masucci

Managing Editor: Larry Main

© 2014 Delmar, Cengage Learning

ALL RIGHTS RESERVED. No part of this work covered by the copyright herein

may be reproduced, transmitted, stored, or used in any form or by any means

graphic, electronic, or mechanical, including but not limited to photocopying,

recording, scanning, digitizing, taping, Web distribution, information networks,

or information storage and retrieval systems, except as permitted under

Section 107 or 108 of the 1976 United States Copyright Act, without the prior

written permission of the publisher.

Senior Product Manager: John Fisher

Editorial Assistant: Kaitlin Murphy

Director, Brand Management: Jason Sakos

Brand Manager: Kristin McNary

Director, Market Development: Debbie Yarnell

For product information and technology assistance, contact us at

Cengage Learning Customer & Sales Support, 1-800-354-9706

For permission to use material from this text or product,

submit all requests online at www.cengage.com/permissions.

Further permissions questions can be e-mailed to

permissionrequest@cengage.com

Market Development Manager: Erin Brennan

Senior Production Director: Wendy Troeger

Production Manager: Mark Bernard

Content Project Manager: Barbara LeFleur

Production Technology Assistant: Emily Gross

Library of Congress Control Number: 2012934976

ISBN-13: 978-1-133-60729-8

ISBN-10: 1-133-60729-2

Senior Art Director: David Arsenault

Technology Project Manager: Joe Pliss

Delmar

5 Maxwell Drive

Clifton Park, NY 12065-2919

USA

Cengage Learning is a leading provider of customized learning solutions with

office locations around the globe, including Singapore, the United Kingdom,

Australia, Mexico, Brazil, and Japan. Locate your local office at:

international.cengage.com/region

Cengage Learning products are represented in Canada by Nelson Education, Ltd.

To learn more about Delmar, visit www.cengage.com/delmar

Purchase any of our products at your local college store or at our preferred

online store www.cengagebrain.com

Notice to the Reader

Publisher does not warrant or guarantee any of the products described herein or perform any independent

analysis in connection with any of the product information contained herein. Publisher does not assume,

and expressly disclaims, any obligation to obtain and include information other than that provided to it by

the manufacturer. The reader is expressly warned to consider and adopt all safety precautions that might be

indicated by the activities described herein and to avoid all potential hazards. By following the instructions

contained herein, the reader willingly assumes all risks in connection with such instructions. The publisher

makes no representations or warranties of any kind, including but not limited to, the warranties of fitness for

particular purpose or merchantability, nor are any such representations implied with respect to the material set

forth herein, and the publisher takes no responsibility with respect to such material. The publisher shall not be

liable for any special, consequential, or exemplary damages resulting, in whole or part, from the readers’ use of,

or reliance upon, this material.

Printed in the United States of America

1 2 3 4 5 6 7 16 15 14 13 12

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

Contents

Preface

Chapter 1 Introduction to Microcontroller

1.1

1.2

1.3

1.4

1.5

1.6

1.7

1.8

1.9

1.10

1.11

1.12

1

Objectives 1

A Brief History of the Computer 2

1.2.1

Mainframe Computers 3

1.2.2

Minicomputers 4

1.2.3

Microcomputers 4

1.2.4

Supercomputers 5

Computer Hardware Organization 6

The Processor 6

1.4.1

The Arithmetic Logic Unit (ALU) 6

1.4.2

Registers 7

1.4.3

The Control Unit 8

1.4.4

The Language Issue 8

The Microprocessor 9

The Microcontroller 10

Embedded Systems 10

1.7.1

Characteristics of Embedded Systems 11

1.7.2

User Interfaces 11

Memory 11

1.8.1

Magnetic Memory 11

1.8.2

Optical Memory 12

1.8.3

Semiconductor Memory 12

1.8.4

Nonvolatile and Volatile Memory 12

1.8.5

Random Access Memory (RAM) 12

1.8.6

Read-Only Memory (ROM) 13

Memory-System Operation 14

1.9.1

Read Operation 15

1.9.2

Write Operation 15

Program Execution 16

1.10.1

The Program Counter Circuit 16

1.10.2

Starting Program Execution 17

1.10.3

Instruction Execution Process 18

Summary 18

Exercises 20

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

iv

Contents

Chapter 2 Introduction to the AVR Microcontroller

2.1

2.2

2.3

2.4

2.5

2.6

2.7

2.8

2.9

Objectives 21

An Overview of the AVR Microcontroller Family 22

The AVR Memory Space 22

The AVR CPU Register 24

2.4.1

The RAMPX, RAMPY, and RAMPZ Registers 25

2.4.2

The Extended Indirect Register (EIND) 25

2.4.3

The RAMPD Register 25

2.4.4

The Status Register (SREG) 26

The AVR Instruction Set 27

AVR Addressing Modes 27

2.6.1

Register Direct Mode 28

2.6.2

I/O Direct Mode 28

2.6.3

Direct Data Mode 28

2.6.4

Data Indirect with Displacement Mode 28

2.6.5

Data Indirect Mode 29

2.6.6

Data Indirect with Pre-Decrement 29

2.6.7

Data Indirect with Post-Increment 29

2.6.8

Program Memory Constant Addressing Using the LPM, ELPM,

and SPM Instructions 30

2.6.9

Program Memory with Post-Increment Using the LPM Z+

and ELPM Z+ Instructions 30

2.6.10

Direct Addressing, JMP and CALL 30

2.6.11

Indirect Program Addressing, IJMP and ICALL 31

2.6.12

Relative Program Addressing, RJMP and RCALL 31

A Sample of AVR Instructions 31

2.7.1

The Data Transfer Instructions 31

2.7.2

Addition Instruction 35

2.7.3

Subtract Instructions 37

Summary 38

Exercises 39

Chapter 3 AVR Assembly Language Programming

3.1

3.2

3.3

21

Objectives 41

AVR Assembly Language Program Structure

3.2.1

Label Field 42

3.2.2

Operation Field 42

3.2.3

Operand Field 43

3.2.4

Comment Field 43

Expressions 43

3.3.1

Operands 43

3.3.2

Functions 44

3.3.3

Operators 44

3.3.4

Formats of Constants 45

41

42

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

v

Contents

3.4

3.5

3.6

3.7

3.8

3.9

3.10

3.11

3.12

3.13

3.14

3.15

3.16

Memory Class 46

Assembler Directives 47

3.5.1

The BYTE Directive 47

3.5.2

The CSEG Directive 48

3.5.3

The DB Directive 48

3.5.4

The DEF Directive 48

3.5.5

The DEVICE Directive 49

3.5.6

The DSEG Directive 49

3.5.7

The DW Directive 49

3.5.8

The MACRO and ENDMACRO Directives

3.5.9

The EQU Directive 50

3.5.10

The ESEG Directive 51

3.5.11

The EXIT Directive 51

3.5.12

The INCLUDE Directive 51

3.5.13

The LIST and NOLIST Directives 51

3.5.14

The LISTMAC Directive 51

3.5.15

The ORG Directive 51

3.5.16

The Set Directive 52

AVR Assembly Program Template 52

Software Development Issue 53

Writing Programs to Perform Arithmetic 55

3.8.1

The Carry/Borrow Flag 57

3.8.2

Multiprecision Addition 57

3.8.3

The C Flag and Subtraction 58

3.8.4

Multiprecision Subtraction 59

3.8.5

Multiplication and Division 59

Accessing Data in Data and Program Memory 61

Writing Program Loops 62

3.10.1

The Infinite Loop 62

3.10.2

The For-Loop 63

3.10.3

The While-Loop 65

3.10.4

The Repeat-Until Loop 67

Shift and Rotate Instructions 70

Boolean Instructions 74

Bit Manipulating Instructions 75

Create Time Delay Using Program Loops 76

Summary 77

Exercises 78

49

Chapter 4 Hardware and Software Development Tools for the AVR 81

4.1

4.2

4.3

Objectives 81

Development Tools for the Atmel AVR 82

Hardware Development Tools 82

4.3.1

Choosing a Demo Board for Learning the AVR

4.3.2

The EasyAVR M1280 Demo Boards 83

82

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

vi

Contents

4.4

4.5

4.6

4.7

4.8

4.9

4.3.3

Stingray XMega Demo Board 84

4.3.4

Arduino Demo Kits 85

4.3.5

Debug Adapters from Atmel 86

Software Development Tools 88

Using the AVR Studio IDE 88

4.5.1

Create a Project 89

4.5.2

Enter the Program 90

4.5.3

Assemble (or Build) the Project 90

4.5.5

Program Execution and Debugging 93

Tips for Assembly Program Debugging 98

4.6.1

Syntax and Semantic Errors 98

4.6.2

Logical Errors 101

4.6.3

General Debug Strategy 101

4.6.4

Common Program Logical Errors 101

Project File Structure 102

Summary 102

Lab Assignments 103

Chapter 5 Advanced Assembly Programming and Subroutine Calls 105

5.1

5.2

5.3

5.4

5.5

5.6

5.7

5.8

5.9

5.10

Objectives 105

Introduction 106

The Stack Data Structure 106

5.3.1

Initializing the Stack Pointer 107

5.3.2

Instructions for Stack Operation 107

An Example of Subroutine 108

Issues Related to Subroutine Calls 109

5.5.1

Parameter Passing 109

5.5.2

Local Variable Allocation and Deallocation 109

5.5.3

Result Returning 110

5.5.4

Accessing Local Variables in the Stack 111

5.5.5

Register Usage Issue 111

5.5.6

Instructions for Subroutine Call 111

Writing Subroutines to Perform Multiprecision Arithmetic 114

5.6.1

Writing Subroutines to Perform 16-Bit Unsigned

Multiplication 114

5.6.2

Writing a Subroutine to Perform 16-bit Signed Multiplication 116

5.6.3

Writing Subroutines to Perform Unsigned Multiprecision

Division 118

5.6.4

Converting an Internal Binary Number into a BCD String 120

5.6.5

Signed Division Operation 122

5.6.6

Finding the Square Root 123

5.6.7

Prime Test Subroutine 126

Subroutines with Local Variables in Stack 128

5.7.1

Subroutine to Convert a BCD String to a Binary Number 128

5.7.2

Bubble Sort 133

Summary 138

Exercises 139

Lab Assignments 140

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

vii

Contents

Chapter 6 C Language Programming

6.1

6.2

6.3

6.4

6.5

6.6

6.7

6.8

6.9

6.10

143

Objectives 143

Introduction to C 144

Types, Operators, and Expressions 145

6.3.1

Data Types 145

6.3.2

Variable Declarations 145

6.3.3

Constants 146

6.3.4

Arithmetic Operators 146

6.3.5

Bitwise Operators 148

6.3.6

Relational and Logical Operators 149

6.3.7

Precedence of Operators 149

Control Flow 150

6.4.1

If Statement 150

6.4.2

If-Else Statement 151

6.4.3

Multiway Conditional Statement 151

6.4.4

Switch Statement 152

6.4.5

For-Loop Statement 152

6.4.6

While Statement 153

6.4.7

Do-While Statement 153

6.4.8

Goto Statement 153

Input and Output 154

Functions and Program Structure 155

6.6.1

Function Prototype 157

6.6.2

Writing a C Program with Multiple Functions 157

Pointers, Arrays, Structures, Unions, and Type Definition 158

6.7.1

Pointers and Addresses 158

6.7.2

Arrays 159

6.7.3

Pointers and Arrays 160

6.7.4

Passing Arrays to a Function 160

6.7.5

Initializing Arrays 161

6.7.6

Structures 161

6.7.7

Unions 163

6.7.8

The typedef Statement 163

6.7.9

Enumerated Data Types 164

Miscellaneous Items 165

6.8.1

Automatic/External/Static/Volatile 165

6.8.2

Scope Rules 165

6.8.3

Type Casting 166

6.8.4

Pointer to Functions 167

The C Preprocessor 168

6.9.1

The #define Statement 168

6.9.2

The ## Operator 169

6.9.3

The #include Statement 170

6.9.4

Conditional Compilation 171

Using the AVR Studio C Compiler 172

6.10.1

AVR Peripheral Register Naming Convention 173

6.10.2

AVR Peripheral Register Bit Naming Convention 173

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

viii

Contents

6.11

6.12

6.13

6.14

6.15

6.10.3

Accessing AVR Mega Device Peripheral Registers in C 174

6.10.4

Accessing AVR XMega Device Peripheral Registers in C 174

Using the AVR Studio IDE to Develop C Programs 177

6.11.1

Create a New Project 177

6.11.2

Entering C Programs in AVR Studio IDE 180

6.11.3

Add C Files into the Project 181

6.11.4

Compile (or Build) the Project 182

6.11.5

Execute and Debug the Project 183

Multiple-File Project 190

Summary 193

Exercises 194

Lab Assignments 195

Chapter 7 System Clock Configuration

7.1

7.2

7.3

7.4

7.5

7.6

Objectives 197

Overview of System Clock Generation 198

The Clock System of the AVR Mega Devices 198

7.3.1

Clock Sources 198

7.3.2

Default Clock Source 199

7.3.3

External Clock 200

7.3.4

Watchdog Oscillator 200

7.3.5

Low-Frequency Oscillator 200

7.3.6

Timer/Counter Oscillator 200

7.3.7

System Clock Prescaler 200

Clock System of the XMega Devices 204

7.4.1

Internal Oscillators 205

7.4.2

External Clock Sources 205

7.4.3

System Clock Selection and Prescalers 206

7.4.4

PLL Circuit 209

7.4.5

DFLL 2 MHz and DFLL 32 MHz 210

7.4.6

External Oscillator Failure Detector 213

Summary 215

Exercises 216

Chapter 8 Parallel I/O

8.1

8.2

8.3

197

217

Objectives 217

I/O Introduction to I/O PORTs 218

8.2.1

I/O Addressing Issue 218

8.2.2

I/O Synchronization 219

8.2.3

Synchronization Issue for Parallel PORTs 219

8.2.4

Synchronization Issue for Serial Interface 219

I/O Pin Driving Circuit Structure 220

8.3.1

Totem Pole 220

8.3.2

Bus Keeper 221

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

ix

Contents

8.4

8.5

8.6

8.7

8.8

8.9

8.10

8.11

8.3.3

Wired-OR 222

8.3.4

Wired-AND 222

Electrical Characteristic Consideration for I/O Interfacing 222

8.4.1

Voltage-Level Compatibility 223

8.4.2

Current Drive Capability 225

8.4.3

Timing Compatibility 226

Overview of the AVR Mega Parallel PORTs 227

8.5.1

Configuring the Mega I/O Pins 228

8.5.2

Toggling the Mega I/O Pin 228

8.5.3

Reading the Pin Value 228

8.5.4

Unconnected Pins 229

8.5.5

Alternate PORT Functions 229

Overview of AVR XMega Parallel PORTs 233

8.6.1

Setting the Direction of PORT Pins 234

8.6.2

Controlling the Output Value of PORT Pins 235

8.6.3

Reading the Logic State of PORT Pins 235

8.6.4

Pin Configuration 235

8.6.5

Multipin Configuration 237

8.6.6

Virtual PORTs 237

8.6.7

Alternate PORT Functions of XMega 239

Simple I/O Devices 239

8.7.1

Interfacing with LEDs 239

8.7.2

Interfacing with Seven-Segment Displays 242

8.7.3

Generating a Digital Waveform Using an I/O Pin 247

8.7.4

Making a Sound using an I/O Pin 248

8.7.5

Interfacing with DIP Switches 250

Interfacing with a D/A Converter 251

8.8.1

The AD7302 DAC 251

8.8.2

Interfacing the AD7302 with the AVR Mega or XMega Devices

Summary 254

Exercises 254

Lab Assignments 256

Chapter 9 Interrupt Handling, Resets, and Power Management

9.1

9.2

9.3

9.4

252

259

Objectives 259

Basic Concepts on Interrupt 260

9.2.1

Why Interrupt Is Useful 260

9.2.2

Enabling and Disabling Interrupts 260

9.2.3

Prioritizing Multiple Interrupts 261

9.2.4

Servicing the Interrupt 261

9.2.5

The Interrupt Vector 261

9.2.6

Writing an Interrupt-Driven Program 262

Resets 262

The AVR Mega Interrupts 263

9.4.1

AVR Mega Device Interrupt Vectors 263

9.4.2

The Mega AVR Microcontroller Configuration Register (MCUCR) 266

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

x

Contents

9.5

9.6

9.7

9.8

9.9

9.10

9.11

9.12

9.4.3

AVR Mega External Interrupt Pins 267

9.4.4

Pin Change Interrupt 268

9.4.5

Writing Interrupt Service Routine in C for AVR Mega Devices

The XMega Device Interrupts 272

9.5.1

PMIC Operation 273

9.5.2

XMega Maskable Interrupts 273

9.5.3

XMega Nonmaskable Interrupt 273

9.5.4

XMega Interrupt Level 273

9.5.5

XMega Interrupt Priority 274

9.5.6

PMIC Registers 274

9.5.7

XMega Interrupt Sources 276

9.5.8

XMega PORT Interrupt 277

AVR Mega Reset 283

AVR Mega Watchdog Timer 284

XMega Reset 286

9.8.1

XMega Brown-Out Reset 287

9.8.2

Spike Detector Reset 288

9.8.3

XMega Watchdog Timer 288

9.8.4

XMega WDT Programming 291

Power Management and Sleep Modes 293

9.9.1

Mega Sleep Modes 293

9.9.2

XMega Sleep Modes 297

Summary 300

Exercises 302

Lab Assignments 302

Chapter 10 Advanced Parallel I/O

10.1

10.2

10.3

10.4

10.5

10.6

270

305

Objectives 305

Interfacing a Parallel PORT to a Keypad 306

10.2.1

Keypad Scanning 306

10.2.2

Keyboard Debouncing 307

10.2.3

ASCII Code Lookup 309

Driving the Stepper Motor 311

10.3.1

Principles of Rotation 311

10.3.2

Discrete Stepper Motor Drivers 315

10.3.3

Integrated Stepper Motor Driver 318

Direct Memory Access (DMA) Transfer 319

10.4.1

Overview of the XMega DMA Controller 319

10.4.2

DMA Registers 319

10.4.3

DMA Channel Operation 321

Liquid Crystal Displays (LCDs) 329

The HD44780 LCD Controller 330

10.6.1

Display Data RAM 334

10.6.2

Character Generator ROM (CGROM) 334

10.6.3

Character Generator RAM (CGRAM) 334

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

xi

Contents

10.7

10.8

10.9

10.6.4

LCD Controller Registers 334

10.6.5

Instruction Description 335

10.6.6

Interfacing the HD44780 to the AVR Microcontroller

10.6.7

LCD Startup Sequence 338

10.6.8

Writing LCD Programs 339

Summary 346

Exercises 347

Lab Assignments 348

Chapter 11 Timer Functions of the Mega AVR

11.1

11.2

11.3

11.4

11.5

11.6

11.7

11.8

11.9

11.10

336

351

Objectives 351

Introduction to the Microcontroller Timer System 352

11.2.1

Using a Timer to Create Time Delays 352

11.2.2

Input Capture 352

11.2.3

Output Compare 353

11.2.4

Pulse-Width Modulation (PWM) 353

Overview of the Mega AVR Timer System 355

11.3.1

Timers Pin Assignment 355

11.3.2

8-Bit Timer Building Blocks 355

11.3.3

16-Bit Timer Building Blocks 357

Timer Clock Source Selection 357

Timer/Counter Operation Modes 360

11.5.1

8-Bit Timer/Counter Operation Modes 360

11.5.2

16-Bit Timer/Counter Operation Modes 362

Applications of Each Timer/Counter Operation Mode 366

Using the Timer Normal Mode 366

11.7.1

Using the Normal Mode in Creating Time Delays 366

11.7.2

Using the Timer Normal Mode in Waveform Generation 368

11.7.3

Using the Normal Mode to Make Sound 373

11.7.4

Using the Normal Mode to Play a Song 375

11.7.5

Using the Normal Mode to Measure Signal Frequency 381

11.7.6

Measuring Signal Period Using the Normal Mode 384

Using the CTC Mode 386

11.8.1

Using the CTC Mode to Create Time Delay 386

11.8.2

Using the CTC Mode to Generate Waveform 387

Using the Fast PWM Mode 391

11.9.1

Compare Match Pin Action in Fast PWM Mode 391

11.9.2

Using OCRnA to Hold the TOP Value 391

11.9.3

Using ICRn to Hold the TOP Value 391

11.9.4

Extreme Cases for the Fast PWM 392

Using the Phase-Correct PWM Mode 393

11.10.1 The Choice of the TOP Value 394

11.10.2 Pin Action on Compare Match in the Phase-Correct PWM

Mode 394

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

xii

Contents

11.11

11.12

11.13

11.14

11.15

Using the Phase and Frequency Correct PWM Mode 396

Driving the DC Motor 397

11.12.1 DC Motor Driver ICs 398

11.12.2 Driving a DC Motor Using the SN754410 398

Summary 399

Exercises 401

Lab Assignments 402

Chapter 12 Event System and Timer Functions of XMega

12.1

12.2

12.3

12.4

12.5

12.6

12.7

12.8

12.9

12.10

12.11

Objectives 405

The XMega Event System 406

12.2.1

Signaling Events 406

12.2.2

Data Events 406

12.2.3

Manually Generating Events 407

12.2.4

Event Routing Network 407

12.2.5

Event Timing 409

12.2.6

Applications of Events 410

An Overview of the XMega Timer System 410

XMega Timer Operation and Configuration 413

12.4.1

Timer Clock Source 413

12.4.2

Timer Operation Modes 413

12.4.3

Double Buffering 414

The Normal Mode 415

12.5.1

Input Capture 416

12.5.2

General Input Capture 417

12.5.3

Frequency Capture 420

12.5.4

Pulse-Width Capture 423

12.5.5

32-Bit Input Capture 423

12.5.6

Capture Overflow 426

12.5.7

Creating Time Delays 426

The Frequency (FRQ) Waveform Generation Mode

The Single-Slope PWM Generate Mode 439

The Dual-Slope PWM Mode 440

Summary 442

Exercises 443

Lab Assignments 443

405

433

Chapter 13 Universal Synchronous Asynchronous Receiver

Transmitter (USART) 449

13.1

13.2

13.3

Objectives 449

Fundamental Concepts of Serial Communication 450

The TIA-232 Standard 450

13.3.1

TIA-232 Electrical Specification 450

13.3.2

TIA-232 Functional Specification 451

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

xiii

Contents

13.4

13.5

13.6

13.7

13.8

13.9

13.10

13.11

13.3.3

TIA-232 Mechanical Specification 454

13.3.4

TIA-232 Procedural Specification 455

13.3.5

Data Format 457

13.3.6

Data Transmission Errors 458

13.3.7

Null Modem Connection 459

The AVR USART 459

13.4.1

USART Signal Pin Assignment 459

13.4.2

Features of the USART Module 460

USART Baud Rate Generation 462

13.5.1

The Mega USART Baud Rate Generator 462

13.5.2

The XMega USART Baud Rate Generator 463

The USART Operation 465

13.6.1

USART Initialization 467

13.6.2

USART Data Transmission 470

13.6.3

USART Data Reception 475

Data Exchange with USART via the TIA-232 Interface 483

Terminal and Terminal Emulation 484

Summary 485

Exercises 486

Lab Assignments 488

Chapter 14 The SPI Function

14.1

14.2

14.3

14.4

14.5

14.6

14.7

14.8

14.9

491

Objectives 491

Introduction to the SPI Function 492

SPI Signal Pins 492

SPI-Related Registers 493

14.4.1

SPI Registers of Mega Devices 493

14.4.2

Registers Related to the XMega SPI Operation 494

The SPI Operation 496

14.5.1

Data Modes 496

14.5.2

SPI Circuit Connection 497

14.5.3

Configuring the SPI for Data Transfer 498

14.5.4

Writing Common SPI Data Transfer Functions 500

SPI-Compatible Chips 504

The 74HC595 Shift Register 504

The TC72 Digital Temperature Sensor 507

14.8.1

Operation of the TC72 507

14.8.2

The Temperature Data Format 508

14.8.3

The Serial Bus Interface 509

14.8.4

Internal Register Structure 509

The 12-Bit D/A Converter MCP4922 513

14.9.1

Signal Pins 514

14.9.2

Data Format 515

14.9.3

MCP4922 Output Voltage 515

14.9.4

Format Data to be Sent to the MCP4922 515

14.9.5

Interfacing the MCP4922 with the AVR 516

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

xiv

Contents

14.10

14.11

14.12

14.13

14.14

Using the USART in the SPI Mode 519

14.10.1 Clock Generation in the MSPI mode 520

14.10.2 USART Registers of Mega Devices in MSPI Mode 520

14.10.3 USART Registers of XMega Devices in the MSPI Mode 521

14.10.4 USART Module Operation in MSPI Mode 523

Interfacing the MC14489 to the USART in the MSPI Mode 527

14.11.1 The Signal Pins of MC14489 528

14.11.2 Operation of the MC14489 529

14.11.3 Cascading the MC14489s 534

Summary 538

Exercises 539

Lab Assignments 541

Chapter 15 Two-Wire Interface (TWI)

15.1

15.2

15.3

15.4

15.5

15.6

15.7

15.8

543

Objectives 543

Introduction to the Two-Wire Interface (TWI) 544

15.2.1

TWI Addressing 544

15.2.2

The TWI Signal Components 545

15.2.3

Bus Arbitration in TWI 547

15.2.4

Clock and Clock Stretching 547

15.2.5

Clock Synchronization 548

15.2.6

Handshaking 548

15.2.7

Data Transfer Format 549

The TWI of the Mega MCU 550

15.3.1

The SCL and SDA Pins 551

15.3.2

The Bit-Rate Generator Unit 551

15.3.3

The Bus Interface Unit 551

15.3.4

The Address Match Unit 552

15.3.5

The Control Unit 552

Using the Mega TWI Module 554

Mega TWI Programming using the Polling Approach 555

15.5.1

Generating the START Condition 555

15.5.2

Generating the STOP Condition 555

15.5.3

Writing Data to the TWI Bus 556

15.5.4

Read Data Byte from the TWI Bus 556

Interfacing with Serial EEPROM AT24C08B 557

15.6.1

Pin Assignment and Block Diagram of AT24C08B

15.6.2

Device Addressing of AT24C08B 557

15.6.3

The AT24C08B Write Operation 558

15.6.4

The AT24C08B Acknowledge Polling 558

15.6.5

The AT24C08B Read Operation 559

Interrupt-Driven Mega TWI Programming 565

Using the Digital Thermostat DS1631A 571

15.8.1

The DS1631A Pin Assignment 571

15.8.2

The DS1631A Functional Description 571

557

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

xv

Contents

15.9

15.10

15.11

15.12

15.13

15.14

15.8.3

DS1631A Registers 572

15.8.4

The DS1631A Operation 573

15.8.5

DS1631A Command Set 574

15.8.6

Interfacing the DS1631A with the AVR Mega MCU 574

The XMega TWI Module 589

15.9.1

The XMega TWI Bus States 589

15.9.2

XMega TWI Master Registers 590

15.9.3

The XMega TWI Master Mode Operation 593

15.9.4

The TWI Slave Mode Registers 596

15.9.5

The XMega TWI Slave Mode Operation 598

Using the XMega TWI Module 600

Using the Real-Time Clock DS1337 606

15.11.1 DS1337 Signal Functions 607

15.11.2 The DS1337 Address Map 607

15.11.3 The DS1337 Clock and Calendar 607

15.11.4 The DS1337 Special Registers 607

15.11.5 The DS1337 Alarms 609

15.11.6 Interfacing the DS1337 with the XMega128A1 610

Summary 616

Exercises 617

Lab Assignments 619

Chapter 16 Analog-to-Digital Converter

16.1

16.2

16.3

16.4

621

Objectives 621

Basics of A/D Conversion 622

16.2.1

A Data Acquisition System 622

16.2.2

Analog Voltage and Digital Code Characteristic 622

16.2.3

A/D Conversion Algorithms 623

16.2.4

Optimal Voltage Range for A/D Conversion 625

16.2.5

Scaling Circuit 626

16.2.6

Voltage Translation Circuit 627

16.2.7

Conversion Ranges 628

The Mega ADC Module 629

16.3.1

Signal Pins of Mega ADC 629

16.3.2

Prescaling and Conversion Timing of Mega ADC 632

16.3.3

Differential Channels of Mega ADC 633

16.3.4

Changing Channel or Reference Selection for Mega ADC 633

16.3.5

Mega ADC Noise Canceller 635

16.3.6

Mega ADC Conversion Result 637

The XMega ADC Module 639

16.4.1

Pipelined Architecture and Virtual Channels of XMega ADC 640

16.4.2

Input Gain Stage of XMega ADC 641

16.4.3

Input Sources of XMega ADC 643

16.4.4

Reference Voltage of XMega ADC 645

16.4.5

Conversion Result of XMega ADC 646

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

xvi

Contents

16.5

16.6

16.7

16.8

16.9

16.10

16.11

16.4.6

Result Presentation of XMega ADC 647

16.4.7

Compare Function of XMega ADC 647

16.4.8

XMega ADC Interrupts 647

16.4.9

Starting an XMega ADC Conversion 649

16.4.10 XMega ADC Clock and Conversion Timing 650

16.4.11 XMega ADC Free-Running Mode 651

16.4.12 XMega ADC Calibration 652

Interfacing with Analog Temperature Sensor TC1047A 658

Measuring Barometric Pressure 661

Measuring Relative Humidity 666

XMega Digital to Analog Converter (DAC) 669

16.8.1

Enabling XMega DAC 670

16.8.2

XMega DAC Conversion Triggering 670

16.8.3

XMega DAC Single and Dual Channel Operation 672

16.8.4

Left- and Right-Adjusted Values 673

16.8.5

XMega DAC Calibration 674

16.8.6

The XMega DAC Status 674

Summary 681

Exercises 682

Lab Assignments 685

Chapter 17 Controller Area Network (CAN)

17.1

17.2

17.3

17.4

17.5

687

Objectives 687

Overview of Controller Area Network 688

17.2.1

Layered Approach in CAN 688

17.2.2

General Characteristics of CAN 689

CAN Messages 689

17.3.1

Data Frame 690

17.3.2

Remote Frame 693

17.3.3

Error Frame 693

17.3.4

Overload Frame 694

17.3.5

Interframe Space 695

17.3.6

Message Filtering 695

17.3.7

Message Validation 696

17.3.8

Bit Stream Encoding 696

Error Handling 696

17.4.1

Bit Error 696

17.4.2

Stuff Error 696

17.4.3

CRC Error 696

17.4.4

Form Error 696

17.4.5

Acknowledgment Error 696

17.4.6

Error Signaling 696

Fault Confinement 697

17.5.1

CAN Node Status 697

17.5.2

Error Counts 697

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

xvii

Contents

17.6

17.7

17.8

17.9

17.10

17.11

17.12

17.13

17.14

17.15

17.16

17.17

CAN Message Bit Timing 697

17.6.1

Nominal Bit Time 697

17.6.2

Length of Time Segments 698

Synchronization Issue 698

17.7.1

Resynchronization Jump Width 698

17.7.2

Phase Error of an Edge 699

CAN System Configuration 699

Overview of the MCP2515 700

17.9.1

CAN Module 700

17.9.2

Control Logic 700

17.9.3

SPI Protocol 701

MCP2515 Transmit/Receive Buffers/Masks/Filters

17.10.1 Transmit Buffers 702

17.10.2 Transmit Priority 704

17.10.3 Initiating Transmission 704

17.10.4 One-Shot Mode 704

17.10.5 TXnRTS Pins 705

17.10.6 Aborting Transmission 706

Message Reception 706

17.11.1 Receive Buffers 707

17.11.2 Receive Priority 710

17.11.3 Start-of-Frame (SOF) Signal 710

17.11.4 RX0BF and RX1BF Pins 710

Message Acceptance Filters and Masks 711

17.12.1 Filter Matching 713

17.12.2 Filter Hits 713

17.12.3 Data Byte Filtering 714

Bit Timing 714

17.13.1 Oscillator Tolerance 715

17.13.2 Bit Timing Configuration 715

Modes of Operation 720

17.14.1 Configuration Mode 720

17.14.2 Sleep Mode 721

17.14.3 Listen-Only Mode 721

17.14.4 Loopback Mode 722

17.14.5 Normal Mode 722

Error Detection 722

Interrupts 723

17.16.1 Interrupt Code Bits 723

17.16.2 Transmit Interrupt 724

17.16.3 Receive Interrupt 724

17.16.4 Message Error Interrupt 724

17.16.5 Bus Activity Wake-up Interrupt 724

17.16.6 Error Interrupt 724

Oscillator 724

17.17.1 CLKOUT Pin 725

17.17.2 RESET Pin 725

702

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

xviii

Contents

17.18

17.19

17.20

17.21

17.22

17.23

Appendices

759

A

B

C

D

E

F

G

References

Glossary

The SPI Interface 725

17.18.1 Reset Instruction 726

17.18.2 Read Instruction 726

17.18.3 Read RX Buffer Instruction 727

17.18.4 Write Instruction 727

17.18.5 Load TX Buffer Instruction 727

17.18.6 Request-to-Send (RTS) Instruction 728

17.18.7 Read Status Instruction 728

17.18.8 RX Status Instruction 728

17.18.9 Bit Modify Instruction 729

Physical CAN Bus Connection 729

17.19.1 The MCP2551 CAN Transceiver 730

17.19.2 Building a CAN Node Using AVR, MCP2515, and MCP2551 731

Programming the MCP2515 for Data Communications 732

17.20.1 MCP2515 Initialization 733

17.20.2 Transmit Message Frames to the MCP2515 737

17.20.3 Receive Message Frames 741

17.20.4 A Complete Program 745

Summary 753

Exercises 754

Lab Assignments 756

Summary of Atmel AVR Instruction Set 759

XMega Devices Interrupt Vector Symbolic Names 763

XMega Devices Interrupt Vector Number Symbolic Names 767

XMega Module Definitions 771

Alternate PORT Functions of XMega64A1/128A1/192A1/

256A1/384A1 773

Music Note Frequencies 781

Example of the LCD Circuit for Mega AVR and LCD Functions 783

787

789

Index 797

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

Preface

A Brief History of AVR

The 8-bit Atmel AVR architecture was initially conceived and developed by two Norwegian

college students, Alf-Egil Bogen and Vegard Wollan, at the Norwegian Institute of Technology.

The AVR is a modified Harvard architecture machine where programs and data are stored in

separate physical memory systems that appear in different address spaces, but it has the capability to read data items from program memory, using special instructions.

The AVR is a reduced instruction set (RISC) microcontroller (MCU). The AVR CPU is pipelined, and hence the majority of AVR instructions are executed in one clock cycle. The AVR

CPU incorporates 32 general-purpose registers (GPR). Most of these registers can be used as

operands of arithmetic and logical instructions. An arithmetic or logical instruction can only

operate on a GPR or an immediate value. Only load and store instructions can access memory

locations.

The AVR family of microcontrollers is divided into four subgroups:

• Tiny AVR

• Mega AVR

• Application specific AVR

• XMega AVR

The first three groups of AVRs share the same peripheral design but differ in the number of

supported peripheral modules. These three groups can operate at a frequency up to 20 MHz.

The XMega was introduced later and has peripheral modules designed differently from the

other three subgroups. In addition to the peripheral modules implemented in the Mega AVR,

the XMega AVR supports direct-memory-access (DMA) transfer, implements event systems for

interperipheral communication, provides an on-chip digital-to-analog converter (DAC), and performs data encryption and decryption in hardware. The XMega can operate at a frequency up to

32 MHz. All four of these groups share the same instruction set. Not all instructions are implemented in all AVR devices.

Since its debut in 1996, the AVR MCU has attracted many adopters because of the following reasons:

• Atmel provides a free integrated development environment (IDE) AVR Studio.

By installing the free WINAVR C compiler, the user has a full-blown IDE with C

language support. Starting with version 5, the AVR Studio already includes the C

compiler.

• Inexpensive development boards are available from Atmel and third-party vendors.

• The AVR MCU is easy to use.

• The device is inexpensive.

Today, the Atmel AVR has become one of the most popular 8-bit microcontrollers (MCUs).

Many universities all over the world are teaching the AVR MCU. This text is written for learning the AVR MCU.

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

xx

Preface

Intended Audience

This book is written for two groups of readers:

1. Students in electrical and computer engineering and technology who are taking an

introductory course of microprocessor interfacing. For this group of readers, this text

serves as a systematic, step-by-step tutorial.

2. Senior electrical and computer engineering students and working engineers who want

to incorporate the AVR in their design projects. Because this book also provides many

more complicated examples, the reader can explore the possible applications of the

AVR peripheral modules in their design projects.

Prerequisites

The author of this book has assumed that the reader has taken a course on digital logic design

and has been exposed to at least one high-level language (preferably C) programming. Knowledge of digital logic design will greatly facilitate learning the AVR. Knowledge of assembly

language programming is not required because one of the goals of this book is to teach AVR

assembly language programming.

Organization of the Book

Chapter 1 gives a brief history of computing, outlines the computer hardware organization,

describes the overall organization of a processor, details the characteristics of a microcontroller and embedded system, classifies memory technologies according to volatility and read/

writability, and summarizes the 8-bit, 16-bit, and 32-bit microcontroller market.

Chapter 2 provides an overview of the AVR MCU family, discusses the AVR memory

space and CPU registers, and examines the AVR addressing modes and a subset of the AVR

instructions.

Chapter 3 introduces basic assembly language programming skills such as arithmetic

operations, program loops, data shifting, and time delay creation.

Chapter 4 introduces development tools, recommends demo boards for learning AVR, and

gives a tutorial on how to use the Atmel AVR Studio to enter, assemble, and execute the program, using a simulator or demo board.

Chapter 5 describes how to write subroutines and make subroutine calls, discusses the

issues related to subroutine calls, and makes recommendation on the use of registers.

Chapter 6 provides a brief tutorial on C language, describes the use of the AVR Studio C

to manipulate the AVR registers and bits, and provides a tutorial on using the AVR Studio to

develop C programs.

Chapter 7 deals with the issue of CPU clock signal generation.

Chapter 8 introduces the concepts of parallel I/O; discusses electrical compatibility

between integrated circuits made of different semiconductor technologies; explores the possible

I/O pin configurations; and demonstrates how to use parallel I/O PORTs to drive LEDs, sevensegment displays; and DAC, and how to generate waveforms.

Chapter 9 introduces the concepts of interrupts, delineates the interrupt mechanism of the

Mega and XMega devices, demonstrates interrupt programming, discusses the mechanism and

applications of reset and watchdog timers, and describes the AVR power management schemes.

Chapter 10 presents a few more applications of parallel I/O PORTs, including keypad input,

stepper motors driving, and liquid crystal display interfacing. This chapter also introduces the

direct memory access method to speed up data transfers.

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

Preface

xxi

Chapter 11 first discusses how to use timers to create a time delay, capture event arrival

time, perform output compare operation, and generate waveforms using pulse-width modulation (PWM). It then gives an overview on the Mega timers and their operation modes. Finally,

this chapter explores the applications of each operation mode.

Chapter 12 introduces the event system that is an interperipheral communication protocol

unique to XMega, provides an overview on the XMega timer system, and explores the applications of the XMega timer functions.

Chapter 13 introduces the TIA-232 protocol, delineates the operation modes of the USART

module of the Mega and XMega devices, and demonstrates the applications of the USART

module.

Chapter 14 introduces the serial peripheral interface (SPI) protocol, illustrates the SPI modules of the Mega and XMega devices, and demonstrates the applications of the SPI module.

Chapter 15 introduces the I2C and TWI protocols, describes the AVR TWI module, and

demonstrates how to use the TWI module to interface with the peripheral chips.

Chapter 16 describes the basic structure of a data acquisition system, delineates the AVR

ADC modules, and demonstrates how to use the ADC to measure physical quantities such as

voltage, temperature, humidity, and barometric pressure.

Chapter 17 introduces the controller area network (CAN) protocol, describes the configuration and operation modes of the CAN controller MCP2515, and demonstrates how to use the

MCP2515 and an AVR MCU to build a CAN node to perform data communication.

Pedagogical Features

Each chapter starts with a list of objectives. Every subject is presented in a step-by-step manner.

Background issues are presented before the specifics related to each AVR function are discussed.

Numerous examples are then presented to demonstrate the use of each AVR peripheral function. Procedural steps and flowcharts are used to help the reader understand the program logic

in most examples.

Both the assembly and C languages are used to illustrate the programming of the AVR functions. Using assembly language gives students an intimate feel about the functioning of the

MCU, whereas using C language yields higher productivity. The instructor can opt to use only

assembly language, only C language, or both in teaching the AVR MCU.

Development Tools

To learn the programming and interfacing of a microcontroller, the learner needs both the software and hardware development tools.

Software Development Tools

The software tools that the learner needs include the text editor, cross-assembler, crosscompiler, simulator, debugger, and the device driver for the hardware debug adapter. Software

vendors often put together these software programs and sell them as a package called an integrated development environment (IDE). Atmel provides a free IDE called AVR Studio to the

AVR user. Before version 5, the user had to install the WINAVR C compiler in order to use the

C language as his or her developing language. Starting with version 5, the C compiler became

part of the IDE. Currently, the AVR Studio supports all 8-bit and 32-bit AVR MCUs. Eventually,

the AVR Studio will also support the Atmel ARM microcontrollers.

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

xxii

Preface

Hardware Development Tools

The minimum hardware that a learner needs is a demo board and a programmer. The programmer connects to the host computer (usually a PC), and the demo board via a USB cable. The

programmer circuit can also be built into the demo board. This way the user only needs a demo

board and a USB cable. Both the demo board EasyAVR M1280 from AVRVI and the Stingray

XMega from XBIT Inc. have this capability built in. However, program debugging is a difficult

process. A debugger is highly desirable and consists of both the hardware and software.

First of all, the microcontroller must have a debug support circuit. The AVR provides a

proprietary programming debug interface called PDI that uses two dedicated pins (PDI_CLK

and PDI_DATA) for the host computer to access the MCU internal resources such as registers,

data memory, and program memory nonintrusively. Commands can be sent to reset the program counter, set breakpoint, step the program, run-to-cursor, read out register and memory

contents, and so on, through the PDI interface. The AVR also supports the industrial standard

JTAG interface that uses four pins (TMS, TCK, TDI, and TDO) to perform programming and

debugging. JTAG interface is the acronym for Joint Test Action Group interface, which is the

boundary-scan interface defined by the IEEE 1149.1 standard.

Second, software is needed to run on the host computer that sends commands to reset the

program counter, step the instruction, set the breakpoint, add program variables to the watch

list, execute the program until the cursor position, and so on. This software is called a debugger

and is part of the IDE.

Third, a debug adapter that connects the host computer and the demo board is required.

The debug adapter receives commands coming from the host computer, converts them into

appropriate PDI instructions, and sends them to the MCU in serial format.

Atmel provides four debug adapters (Dragon, JTAGICE3, JTAGICE mkII, and AVR ONE!)

to AVR users. Dragon is the least expensive, whereas the AVR ONE! is the most expensive

debug adapter. All of these debug adapters support all AVR 8-bit and 32-bit devices.

Demo Boards

Some of the demo boards include many I/O devices and peripheral chips, whereas other demo

boards are bare kits. Some of the peripheral chips are either very small or use a package that

is difficult to handle manually. If these chips are not pre-soldered on the demo board, then

it will be difficult to perform the experiment. Bare kits will be cheaper. However, when the

costs of all the I/O devices and peripheral chips required in learning the AVR MCU are added

up, the bare kits may be much more expensive. Because the instructor may opt to teach only

the Mega AVR or the XMega AVR, the learner will only need a Mega-based or an XMega-based

demo board.

Because the Mega MCUs were introduced a few years before the XMega MCUs, there

are a lot more Mega-based demo boards than XMega-based demo boards available in the

market. If the instructor wants to teach all the topics in the text, then the EasyAVR M1280

from AVRVI (enshop.avrvi.com) is the only Mega-based demo board, and the Stingray

XMega from XBIT Inc. (xbitinc.com) is the only XMega-based demo board that provides

all the required features. If the instructor does not plan to teach Chapter 17, which covers

CAN, then more demo boards can be used. The user can find additional AVR demo boards

from ebay.com by entering “Mega128” as the search key. For example, Waveshare Electronics (wvshare.com) produces quite a few Mega-based (for example, OpenM128 package B) and

XMega-based (for example, EVK XA1) demo boards that are suitable for learning the Mega

and XMega devices.

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

xxiii

Preface

Complementary Material

The following materials are useful in learning the AVR and are placed on the complementary CD:

• The source code of all example programs in the text

• The PDF files of datasheets of the Mega2560, XMegaA1, and all the peripheral

chips covered in the text

• Utility programs (in assembly and C languages) for time delay, system clock

generation, LCD, USART, and SPI

Supplements

An Instructor Resource CD is available for this text (ISBN 1133608884). The elements of the

instructor resource link directly to the text to provide a unified instructional system. With the

instructor resource you can spend your time teaching, not preparing to teach.

Features in the instructor resource include the following:

• A Solution Manual with solutions to the exercises is available to instructors as a

PDF file.

• An Image Gallery of all the figures and tables is also available.

• ExamView Test Bank: Questions of varying levels of difficulty are provided for each

chapter. This versatile tool enables the instructor to manipulate the test banks to

create original tests.

• Chapter Presentations in PowerPoint: These slides provide the basis for a

lecture outline to present concepts and material. Key points and concepts can be

graphically highlighted for student retention.

Professors can request a copy of the instructor resource from their sales representatives.

These files are also available through an instructor companion website.

Feedback and Update

The author has tried his best to eliminate errors from this text. However, it is impossible to get

rid of all of the errors. The solutions in the examples of this book may not be the best either.

Error reports and suggestions are welcomed. Please send them to han-way.huang@mnsu.edu.

Acknowledgments

This book would not have been possible without the help of a number of people. I would like to

thank the following reviewers who provided valuable opinions on how to improve the quality

of this book:

Rabah Aoufi DeVry, Irving, Texas

Christopher Cischke, Michigan Technological University

Fanourios Halkiadakis, CalState Polytechnic University, Pomona, California

Max Rabiee, University of Cincinnati, Cincinnati, Ohio

Roman Stembrok, San Diego, California

Ron Tinckham, Santa Fe College, Gainesville, Florida

Hanqi Zhuang, Florida Atlantic University, Boca Raton, Florida

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

xxiv

Preface

I would also like to thank Stacy Masucci, acquisitions editor, and John Fisher, senior product manager, of Cengage Learning for their enthusiastic support during the preparation of this

book, and the Cengage Learning staff for their outstanding production work. I would like to

express my heartfelt appreciation to my students and colleagues at the Department of ECET at

Minnesota State University, Mankato, who allowed me to test out the manuscript.

Finally, I would like to express my thanks to my wife, Su-Jane, and my sons, Craig and

Derek, for their encouragement and support during the entire preparation of this book.

Han-Way Huang

Mankato, Minnesota

March 1, 2012

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

1

Introduction to Microcontroller

1.1 Objectives

After completing this chapter, you will be able to

• Describe the characteristics of a mainframe

computer.

•

•

•

•

•

•

Describe the characteristics of a minicomputer.

Describe the characteristics of a microcomputer.

Describe the characteristics of a supercomputer.

Describe the characteristics of a microprocessor.

Describe the characteristics of a microcontroller.

Describe the characteristics of an embedded

system.

• Explain the structure of a computer hardware.

• Explain the memory technologies.

• Explain the structure of an ALU that performs

ADD, SUB, AND, and OR operations.

• Explain the instruction execution process.

• Understand the 8-bit, 16-bit, and 32-bit

microcontroller markets.

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

2

Chapter 1

■

Introduction to Microcontroller

1.2 A Brief History of the Computer

The word computer first appeared in 1613 [1]. It refers to a person who performs the task

of computation, or calculation. At the end of the nineteenth century, the meaning of the word

changed so that it no longer refers to a person but instead to a machine that carries out the task

of calculation.

A computer consists of hardware and software. The computer hardware implements

the binary digital logic that performs the desired computation. The binary digital logic was

invented by Claude Shannon in 1937. Boolean algebra provides the theoretical foundation for

the binary digital logic. The subjects of binary digital logic and Boolean algebra are covered in

many textbooks [2,3,4] on digital logic design. The smallest unit of information manipulated

by the computer is referred to as a bit, which represents on or off, open or closed, or 1 or 0.

A group of 8 bits is referred to as a byte; a group of bytes (either 2 or 4) is referred to as a word;

and a group of 64 bits is referred to as a double word. The relationship among a bit, a byte, a

word, and a double word is illustrated in Figure 1.1, where a bit is represented by a rectangle;

a byte is represented by eight rectangles; a word is represented by 32 rectangles; and a double

word is represented by 64 rectangles. The number above a rectangle refers to the bit number, or

the bit position, within a byte, a word, or a double word. Within a byte, the bits are numbered

from 7 down to 0. Within a double word, the bits are numbered from 63 down to 0. A bit with a

higher bit number is more significant than a bit with a lower bit number.

0

7

6

5

4

3

2

1

0

Byte

31 30 29 28 27 26 25 24

7

6

5

4

3

2

1

0

Word

63 62 61 60 59 58 57 56

31 30 29 28 27 26 25 24

7

6

5

4

3

2

1

0

Double word

Figure 1.1

■

Source: Atmel Corporation, The Atmel AVR

Microcontroller

Bit

Relative sizes of a bit, byte, word, and double word

The defining feature of modern computers that distinguishes them from other machines

is their programmability. The hardware of a modern computer consists of processor, input

devices, output devices, and memory. The processor carries out all the computations. It is

designed to execute a set of instructions. An instruction is simply a group of bits that tells

the computer what operation to perform. The operands are also specified in the instruction

(using addressing modes). An instruction may perform the operation of addition, subtraction,

multiplication, division, AND, OR, shift left, shift right, and so on. A program is a sequence of

selected instructions that performs certain tasks such as finding the square root of an integral

number or measuring the frequency of an unknown signal. By providing different programs to

the computer, the same computer can perform different operations. In early computers, programming was performed by changing wires and switches. This proved to be a difficult task.

Starting in 1940s, the stored program architecture was adopted to provide programmability

to the computer. The program is stored in memory, as are the data to be manipulated by the

program. Because this design was first proposed by John von Neumann in 1945, the stored

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

1.2

■

3

A Brief History of the Computer

Memory

Control

unit

Arithmetic logic

unit (ALU)

Input

Figure 1.2

■

Central processing

unit (CPU)

Output

Source: Atmel Corporation, The Atmel AVR

Microcontroller

program architecture is also called von Neumann Architecture. The outline of this architecture

is shown in Figure 1.2. The von Neumann Architecture has a processing unit and a single storage structure that holds both instructions and data. The combination of control unit and the

arithmetic logic unit is referred to as the central processing unit (CPU) or simply the processor.

A deviation from the von Neumann Architecture is the Harvard Architecture, in which program and data are stored in different memories. The Harvard Architecture allows the computer

to access program and data simultaneously.

von Neumann architecture

The maximum number of bits that can be operated on by the ALU in one operation is

referred to as the word length of the processor. A processor may be called 8-bit, 16-bit, 32-bit,

or 64-bit because it can operate on 8-bit, 16-bit, 32-bit, or 64-bit operands in one operation,

respectively.

1.2.1 Mainframe Computers

The earliest digital computers are made of vacuum tubes and were housed in enormous,

room-sized metal boxes or frames. Due to their huge size, they are called mainframe computers.

Mainframe computers are expensive, and only large companies and organizations can afford

them. Later on, the term was used to distinguish high-end commercial computers from less

powerful ones. A mainframe computer has a lot of storage serving simultaneously many users

through terminal stations. The CPU time of the mainframe is divided into slots, with each time

slot assigned to one user.

The mainframe computer market is dominated by the IBM System 360–compatible product line. The IBM System 360 product line was introduced in 1965. It allowed the users to start

with a small system and later on upgrade by adding more memory and faster CPU when their

needs grew. The IBM System 360 was considered one of the most successful computers in history. In 1970, the IBM System 370 family was introduced as the replacement of System 360.

System 370 was backward software compatible to the System 360; that is, all the programs

written for System 360 can also be executed by the System 370. The System 390 was introduced to take the place of System 370. The latest IBM mainframe family (as of December 2011)

is the system z, which is also software compatible with the earliest System 360.

In addition to a fast CPU, a mainframe has the following features:

1. High reliability and security is provided by the redundant design.

2. There are extensive input/output facilities.

3. It has strict backward compatibility with older software; a newer generation of

machines can run software written for older machines. This feature is extremely

important for a computer family to be successful in the market.

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

4

Chapter 1

■

Introduction to Microcontroller

4. The high utilization rate supports massive throughput.

5. Repairs and hardware upgrades take place during normal operation.

1.2.2 Minicomputers

Minicomputers, called mini because they are smaller than mainframe computers, appeared

in the 1960s. The small size of these computers is made possible by the use of transistors, core

memory, and the integrated circuit. Minicomputers usually took up one or a few cabinets the

size of a large refrigerator. The first successful minicomputer was Digital Equipment Corporation’s (DEC) 12-bit PDP-8 introduced in 1964. Other minicomputer vendors include Prime,

Data General, Wang Laboratory, Apollo Computer, and HP.

The off-the-shelf 7400 series digital logic integrated circuits started appearing in minicomputers in the later 1960s. These chips provide many functions useful in a computer and greatly

simplify the design and implementation of minicomputers. Starting in the 1980s, many minicomputers used very large-scale integration (VLSI) circuits. Many minicomputers in this period

were 32-bit and hence were called superminicomputers.

Minicomputers have decent processing power and capacity and hence satisfy the computation needs of many midsize organizations. Like mainframe computers, minicomputers

supported multi-users.

DEC was the leading minicomputer manufacturer. At one time, DEC was the second largest computer company after IBM. The PDP-11 and VAX-11 families of minicomputers from

DEC were very popular in the 1970s and 1980s but started to decline in the late 1980s. Today,

all of the minicomputer manufacturers have disappeared from the computer market due to

the competition of personal computers (PC) and servers. A server is a computer that provides

database access, file access, printing, email, web browsing services and so on to users of other

computers in the network.

1.2.3 Microcomputers

A microcomputer is a computer that uses a microprocessor as its central processing unit.

The microprocessor is explained in a later section. The first batch of microcomputers appeared

in the 1970s. Some of them were sold as kits to be assembled by the user and came with as

little as 256 bytes of memory and no input/output (I/O) devices other than indicator lights and

switches. As microprocessors and semiconductor memory became less expensive in the mid1970s, microcomputers in turn grew faster and cheaper. This resulted in an explosion in their

popularity during the later 1970s and 1980s. Companies such as Cromemco, Altos, and others

have been very successful in producing systems designed for a resourceful end user or consulting firms to deliver business applications such as accounting, database management, and word

processing to small businesses. Some of these microcomputers are single-user systems, whereas

others are multi-user systems.

The Apple II computer, introduced in 1977 by Apple, has become one of the most successful computers in the world. Due to its popularity, many clones have appeared. Unlike earlier

microcomputers, the Apple II was designed to target individual users. For this reason, the Apple

II was called a personal computer instead of a microcomputer. The introduction of Apple II

attracted the attention of many software developers. The Macintosh (often called MAC) introduced in 1984 was the successor of Apple II. The MAC has gone through several generations

and used several different microprocessors as its CPU. Today’s MAC has several versions that

cover desktop, laptop, and all-in-one categories.

Copyright 2012 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).