Marvell. Moving Forward Faster

Integrated 10/100/1000 Mbps Energy

Efficient Ethernet Transceiver

fo

zjr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

7t

x

1p

rs

wi

February 24, 2012

CONFIDENTIAL

Document Classification: Proprietary

Information

d.

Co

.

1prswi7txfozjrtot1xvhoklupjx4d-i1a1tipj * Beijing Sifang Automation Co. Ltd. * UNDER NDA# 12111695

Doc. No. MV-S107146-00, Rev. --

Lt

Alaska®

88E1510/88E1518/88E1512/

88E1514 Datasheet

Co

.

xf

oz

jr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

rs

wi

7t

1p

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

Lt

d.

Cover

Note: Provides related information or information of special importance.

Caution: Indicates potential damage to hardware or software, or loss of data.

Warning: Indicates a risk of personal injury.

Document Status

Co

.

Lt

d.

Technical Publication: 0.0x

rs

wi

7t

fo

zjr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

Doc Status: Advance

For more information, visit our website at: www.marvell.com

Doc. No. MV-S107146-00 Rev. -Page 2

1p

rs

wi

7t

x

Disclaimer

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose,

without the express written permission of Marvell. Marvell retains the right to make changes to this document at any time, without notice. Marvell makes no warranty of any

kind, expressed or implied, with regard to any information contained in this document, including, but not limited to, the implied warranties of merchantability or fitness for any

particular purpose. Further, Marvell does not warrant the accuracy or completeness of the information, text, graphics, or other items contained within this document.

Marvell products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use

Marvell products in these types of equipment or applications.

With respect to the products described herein, the user or recipient, in the absence of appropriate U.S. government authorization, agrees:

1) Not to re-export or release any such information consisting of technology, software or source code controlled for national security reasons by the U.S. Export Control

Regulations ("EAR"), to a national of EAR Country Groups D:1 or E:2;

2) Not to export the direct product of such technology or such software, to EAR Country Groups D:1 or E:2, if such technology or software and direct products thereof are

controlled for national security reasons by the EAR; and,

3) In the case of technology controlled for national security reasons under the EAR where the direct product of the technology is a complete plant or component of a plant,

not to export to EAR Country Groups D:1 or E:2 the direct product of the plant or major component thereof, if such direct product is controlled for national security reasons

by the EAR, or is subject to controls under the U.S. Munitions List ("USML").

At all times hereunder, the recipient of any such information agrees that they shall be deemed to have manually signed this document in connection with their receipt of any

such information.

Copyright © 1999–2012. Marvell International Ltd. All rights reserved. M Logo, Marvell, Moving Forward Faster, Alaska, Link Street, Prestera, Virtual Cable Tester, Yukon,

Datacom Systems On Silicon, AnyVoltage, DSP Switcher, Feroceon, ZX, ZXSTREAM, Armada, Qdeo & Design, QuietVideo, TopDog, TwinD, and Kinoma are registered

trademarks of Marvell or its affiliates. Avanta, Avastar, Carrierspan, DragonFly, HyperDuo, HyperScale, Kirkwood, LinkCrypt, Marvell Smart, The World As You See It,

Turbosan, and Vmeta are trademarks of Marvell or its affiliates.

CONFIDENTIAL

Document Classification: Proprietary Information

Copyright © 2012 Marvell

February 24, 2012, Advance

1prswi7txfozjrtot1xvhoklupjx4d-i1a1tipj * Beijing Sifang Automation Co. Ltd. * UNDER NDA# 12111695

Co

.

xf

oz

jr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

Document Conventions

1p

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

Lt

d.

Alaska® 88E1510/88E1518/88E1512/88E1514 Datasheet

Integrated 10/100/1000 Mbps Energy Efficient Ethernet Transceiver

Lt

The device uses advanced mixed-signal processing to

perform equalization, echo and crosstalk cancellation,

data recovery, and error correction at a gigabit per

second data rate. The device achieves robust

performance in noisy environments with very low power

dissipation.

fo

zjr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

The device supports the RGMII (Reduced pin count

GMII) and SGMII for direct connection to a MAC/Switch

port. The SGMII can also be used on media/line side to

connect to SFP modules that support 1000BASE-X,

100BASE-FX and SGMII. It also supports Copper/Fiber

Auto-media applications with RGMII as the MAC

interface. SGMII operates at 1.25 Gbps over a single

differential pair thus reducing power and number of I/Os

used on the MAC interface.

identification of potential cable malfunctions, thus

reducing equipment returns and service calls. Using

VCT, the Alaska device detects and reports potential

cabling issues such as pair swaps, pair polarity and

excessive pair skew. The device will also detect cable

opens, shorts or any impedance mismatch in the cable

and reporting accurately within one meter the distance to

the fault.

Co

.

The Alaska® 88E1510/88E1518/88E1512/88E1514

device is a physical layer device containing a single

10/100/1000 Gigabit Ethernet transceiver. The

transceiver implements the Ethernet physical layer

portion of the 1000BASE-T, 100BASE-TX, and

10BASE-T standards. It is manufactured using standard

digital CMOS process and contains all the active circuitry

required to implement the physical layer functions to

transmit and receive data on standard CAT 5 unshielded

twisted pair.

d.

OVERVIEW

rs

wi

7t

The device integrates MDI interface termination resistors

into the PHY. This resistor integration simplifies board

layout and reduces board cost by reducing the number

of external components. The new Marvell® calibrated

resistor scheme will achieve and exceed the accuracy

requirements of the IEEE 802.3 return loss

specifications.

The device has an integrated switching voltage regulator

to generate all required voltages. The device can run off

a single 3.3V supply. The device supports 1.8V, 2.5V,

and 3.3V LVCMOS I/O Standards.

The 88E1510/88E1518/88E1512/88E1514 device

supports Synchronous Ethernet (SyncE) and Precise

Timing Protocol (PTP) Time Stamping, which is based on

IEEE1588 version 2 and IEEE802.1AS.

The 88E1510/88E1518/88E1512/88E1514 device

supports IEEE 802.3az-2010 Energy Efficient Ethernet

(EEE) and is IEEE 802.3az-2010 compliant.

10/100/1000BASE-T IEEE 802.3 compliant

Multiple Operating Modes

• RGMII to Copper

• SGMII to Copper (88E1512/88E1514 device only)

• RGMII to Fiber/SGMII (88E1512 device only)

• RGMII to Copper/Fiber/SGMII with Auto-Media

Detect (88E1512 device only)

• Copper to Fiber (1000BASE-X)

(88E1512/88E1514)

Four RGMII timing modes including integrated

delays - This eliminates the need for adding trace

delays on the PCB

Supports 1000BASE-X and 100BASE-FX on the

Fiber interface along with SGMII

Supports LVCMOS I/O Standards on the RGMII

interface

Supports Energy Efficient Ethernet (EEE) - IEEE

802.3az-2010 compliant

• EEE Buffering

• Incorporates EEE buffering for seamless support of

legacy MACs

Ultra Low Power

Integrated MDI interface termination resistors that

eliminate passive components

Integrated Switching Voltage Regulators

Copyright © 2012 Marvell

February 24, 2012, Advance

1p

rs

wi

7t

x

The device incorporates the Marvell Advanced Virtual

Cable Tester® (VCT™) feature, which uses Time Domain

Reflectometry (TDR) technology for the remote

Features

CONFIDENTIAL

Document Classification: Proprietary Information

Doc. No. MV-S107146-00 Rev. -Page 3

1prswi7txfozjrtot1xvhoklupjx4d-i1a1tipj * Beijing Sifang Automation Co. Ltd. * UNDER NDA# 12111695

Co

.

xf

oz

jr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

Integrated 10/100/1000 Mbps Energy Efficient Ethernet

Transceiver

1p

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

Lt

d.

Alaska® 88E1510/88E1518/88E1512/88E1514

Datasheet

MDC/XMDIO Management Interface

CRC checker, packet counter

Packet generation

Wake on Lan (WOL) event detection

Advanced Virtual Cable Tester® (VCT™)

Auto-Calibration for MAC Interface outputs

Temperature Sensor

Supports single 3.3V supply when using internal

switching regulator

I/O pads can be supplied with 1.8V, 2.5V, or 3.3V

Commercial grade, Industrial grade (88E1510 and

88E1512 only)

48-Pin QFN 7 mm x 7 mm Green package with

EPAD (88E1510 and 88E1518) and 56-Pin QFN 8

mm x 8 mm Green package with EPAD

(88E1512/88E1514 device)

Table 1:

88E1510/88E1518/88E1512/88E1514 Device Features

F e a tu re s

88E1510

88E1518

d.

88E1512

88E1514

Lt

Co

.

Yes

Yes

Yes

No

SGMII to Copper

No

No

Yes

Yes

No

No

Yes

No

No

No

Yes

No

fo

zjr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

RGMII to Copper

RGMII to Fiber/SGMII

RGMII to Copper/Fiber/SGMII with Auto-Media Detect

Copper to Fiber

No

No

Yes

Yes

3.3V/2.5V

1.8V only

3.3V/2.5V/1.8V

3.3V/2.5V/1.8V

IEEE 802.3az-2010 Energy Efficient Ethernet (EEE)

Yes

Yes

Yes

Yes

EEE Buffering

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

No

No

Yes

No

Yes

Yes

Yes

Yes

I/O Voltage (VDDO)

rs

wi

7t

Synchronous Ethernet (SyncE)

Precise Timing Protocol (PTP)

Auto-Media Detect

Wake on LAN (WOL)

Package

48-pin QFN

Commercial

Industrial

Commercial

56-pin QFN

Commercial

Industrial

Commercial

Doc. No. MV-S107146-00 Rev. -Page 4

1p

rs

wi

7t

x

Industrial/Commercial Temperature

CONFIDENTIAL

Document Classification: Proprietary Information

Copyright © 2012 Marvell

February 24, 2012, Advance

1prswi7txfozjrtot1xvhoklupjx4d-i1a1tipj * Beijing Sifang Automation Co. Ltd. * UNDER NDA# 12111695

Co

.

Supports Green Ethernet

• Active Power Save Mode

• Energy Detect and Energy Detect+ low power

modes

IEEE1588 version 2 Time Stamping

Synchronous Ethernet (SyncE) Clock Recovery

Three loopback modes for diagnostics

“Downshift” mode for two-pair cable installations

Fully integrated digital adaptive equalizers, echo

cancellers, and crosstalk cancellers

Advanced digital baseline wander correction

Automatic MDI/MDIX crossover at all speeds of

operation

Automatic polarity correction

IEEE 802.3 compliant Auto-Negotiation

Software programmable LED modes including

LED testing

xf

oz

jr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

1p

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

Lt

d.

Alaska® 88E1510/88E1518/88E1512/88E1514 Datasheet

Integrated 10/100/1000 Mbps Energy Efficient Ethernet Transceiver

Integrated Passive

Termination

M

a

g

n

e

t

i

c

s

RJ-45

Media Types:

- 10BASE-T

- 100BASE-TX

- 1000BASE-T

MAC Interface

- RGMII

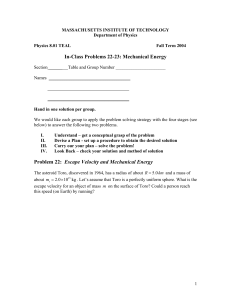

RGMII to Copper Device Application

d.

Media Types:

- 10BASE-T

- 100BASE-TX

- 1000BASE-T

Lt

RJ-45

Co

.

Integrated Passive

Termination

88E1512/

88E1514

Device

10/100/1000 Mbps

Ethernet MAC

M

a

g

n

e

t

i

c

s

fo

zjr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

MAC Interface

- SGMII/SERDES

rs

wi

7t

10/100/1000 Mbps

Ethernet MAC

88E1512

Device

MAC Interface

- RGMII

Integrated Passive

Termination

SGMII to Copper Application

SERDES/

SGMII

Fiber

Optics

Media Types:

- 1000BASE -X

- 100 BASE -FX

- SFP

Fiber

Optics

Media Types:

- 1000BASE -X

- 100BASE-FX

- SFP

RJ-45

Media Type:

- 1000BASE-T

- 100BASE-TX

- 10 BASE-T

10/ 100/1000 Mbps

Ethernet MAC

88E1512

Device

MAC Interface

- RGMII

Integrated Passive

Termination

RGMII to Fiber/SGMII Application

SERDES/

SGMII

OR

M

A

G

Copyright © 2012 Marvell

February 24, 2012, Advance

1p

rs

wi

7t

x

RGMII to Copper/Fiber/SGMII Auto-Media Application

CONFIDENTIAL

Document Classification: Proprietary Information

Doc. No. MV-S107146-00 Rev. -Page 5

1prswi7txfozjrtot1xvhoklupjx4d-i1a1tipj * Beijing Sifang Automation Co. Ltd. * UNDER NDA# 12111695

Features

Co

.

xf

oz

jr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

88E1510/

88E1518/

88E1512

Device

10/100/1000 Mbps

Ethernet MAC

1p

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

Lt

d.

Overview

1.1

Pin Description ................................................................................................................................................18

1.1.1

88E1510/88E1518 48-Pin QFN Package Pinout ..............................................................................19

1.1.2

88E1512 56-Pin QFN Package Pinout .............................................................................................25

1.1.3

88E1514 56-Pin QFN Package Pinout .............................................................................................32

1.2

Pin Assignment List.........................................................................................................................................38

1.2.1

88E1510 48-Pin QFN Pin Assignment List - Alphabetical by Signal Name......................................38

1.2.2

88E1518 48-Pin QFN Pin Assignment List - Alphabetical by Signal Name......................................39

1.2.3

88E1512 56-Pin QFN Pin Assignment List - Alphabetical by Signal Name......................................40

1.2.4

88E1514 56-Pin QFN Pin Assignment List - Alphabetical by Signal Name......................................41

2

PHY Functional Specifications...................................................................................................42

2.1

Modes of Operation and Major Interfaces .......................................................................................................43

2.2

Copper Media Interface...................................................................................................................................45

2.2.1

Transmit Side Network Interface ......................................................................................................45

2.2.2

Encoder ............................................................................................................................................45

2.2.3

Receive Side Network Interface .......................................................................................................46

2.2.4

Decoder ............................................................................................................................................47

2.3

1.25 GHz SERDES Interface ..........................................................................................................................48

2.3.1

Electrical Interface ............................................................................................................................48

2.4

MAC Interfaces ...............................................................................................................................................49

2.4.1

SGMII Interface.................................................................................................................................49

2.4.2

RGMII Interface ................................................................................................................................50

2.4.3

10/100 Mbps Functionality ................................................................................................................51

2.4.4

TX_ER and RX_ER Coding ..............................................................................................................51

fo

zjr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

Co

.

Lt

d.

Signal Description .......................................................................................................................18

rs

wi

7t

1

2.5

Loopback.........................................................................................................................................................52

2.5.1

System Interface Loopback ..............................................................................................................52

2.5.2

Synchronous SERDES Loopback ....................................................................................................53

2.5.3

Line Loopback ..................................................................................................................................54

2.5.4

External Loopback ............................................................................................................................56

2.6

Fiber/Copper Auto-Selection ...........................................................................................................................57

2.6.1

Preferred Media ................................................................................................................................57

2.6.2

Definition of link in SGMII Media Interface in the context of auto media selection ...........................57

2.6.3

Notes on Determining which Media Linked Up .................................................................................58

2.7

Synchronizing FIFO ........................................................................................................................................59

2.8

Resets .............................................................................................................................................................60

2.9

Power Management ........................................................................................................................................61

2.9.1

Low Power Modes ............................................................................................................................61

2.9.2

RGMII/SGMII MAC Interface Power Down .......................................................................................63

2.10

Auto-Negotiation .............................................................................................................................................63

2.10.1 10/100/1000BASE-T Auto-Negotiation .............................................................................................63

2.10.2 1000BASE-X Auto-Negotiation .........................................................................................................64

2.10.3 SGMII Auto-Negotiation ....................................................................................................................65

2.11

Downshift Feature ...........................................................................................................................................67

7t

x

Page 6

1p

rs

wi

Doc. No. MV-S107146-00 Rev. --

CONFIDENTIAL

Document Classification: Proprietary Information

Copyright © 2012 Marvell

February 24, 2012, Advance

1prswi7txfozjrtot1xvhoklupjx4d-i1a1tipj * Beijing Sifang Automation Co. Ltd. * UNDER NDA# 12111695

Co

.

xf

oz

jr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

Table of Contents

1p

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

Lt

d.

Alaska® 88E1510/88E1518/88E1512/88E1514 Datasheet

Integrated 10/100/1000 Mbps Energy Efficient Ethernet Transceiver

2.14

Data Terminal Equipment (DTE) Detect..........................................................................................................74

2.15

Energy Efficient Ethernet (EEE) ......................................................................................................................75

2.15.1 Energy Efficient Ethernet Low Power Modes ...................................................................................75

2.15.2 Energy Efficient Ethernet (EEE) Buffering for Master mode .............................................................76

2.15.3 Energy Efficient Ethernet Auto-Negotiation ......................................................................................76

2.16

CRC Error Counter and Frame Counter..........................................................................................................77

2.16.1 Enabling The CRC Error Counter and Packet Counter ....................................................................77

2.17

Packet Generator ............................................................................................................................................77

2.18

RX_ER Byte Capture ......................................................................................................................................78

2.19

1.25G PRBS Generator and Checker .............................................................................................................79

2.20

MDI/MDIX Crossover ......................................................................................................................................80

2.21

Unidirectional Transmit ...................................................................................................................................80

2.22

Polarity Correction...........................................................................................................................................81

2.23

FLP Exchange Complete with No Link............................................................................................................81

2.24

Duplex Mismatch Indicator ..............................................................................................................................81

2.25

Link Disconnect Counter .................................................................................................................................82

2.26

LED .................................................................................................................................................................83

2.26.1 LED Polarity ......................................................................................................................................83

2.26.2 Pulse Stretching and Blinking ...........................................................................................................84

2.26.3 Bi-Color LED Mixing .........................................................................................................................85

2.26.4 Modes of Operation ..........................................................................................................................86

fo

zjr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

Co

.

Lt

d.

Advanced Virtual Cable Tester®.....................................................................................................................68

2.13.1 Maximum Peak .................................................................................................................................69

2.13.2 First Peak..........................................................................................................................................70

2.13.3 Offset ................................................................................................................................................70

2.13.4 Sample Point ....................................................................................................................................71

2.13.5 Pulse Amplitude and Pulse Width.....................................................................................................71

2.13.6 Drop Link ..........................................................................................................................................71

2.13.7 VCT™ with Link Up ..........................................................................................................................71

2.13.8 Alternate VCT Control.......................................................................................................................72

CLK125 ...........................................................................................................................................................89

2.27.1 Synchronous Ethernet Recovered Clock ..........................................................................................89

2.28

Precise Timing Protocol (PTP) Time Stamping Support .................................................................................90

2.28.1 PTP Control ......................................................................................................................................90

2.28.2 Packet Time Stamping......................................................................................................................91

2.28.3 Time Application Interface (TAI) .......................................................................................................92

2.28.4 ReadPlus Command.........................................................................................................................96

2.29

Interrupt ...........................................................................................................................................................97

2.30

Automatic and Manual Impedance Calibration................................................................................................98

2.30.1 MAC Interface Calibration Circuit .....................................................................................................98

2.30.2 MAC Interface Calibration Register Definitions.................................................................................98

2.30.3 Changing Auto Calibration Targets...................................................................................................99

2.30.4 Manual Settings to The Calibration Registers ..................................................................................99

2.31

Configuring the 88E1510/88E1518/88E1512/88E1514 Device ....................................................................101

2.31.1

Hardware Configuration .................................................................................................................101

2.31.2 Software Configuration - Management Interface ............................................................................102

2.32

Jumbo Packet Support ..................................................................................................................................103

Copyright © 2012 Marvell

February 24, 2012, Advance

1p

rs

wi

7t

x

2.27

CONFIDENTIAL

Document Classification: Proprietary Information

Doc. No. MV-S107146-00 Rev. -Page 7

1prswi7txfozjrtot1xvhoklupjx4d-i1a1tipj * Beijing Sifang Automation Co. Ltd. * UNDER NDA# 12111695

Lt

d.

Co

.

Fast 1000BASE-T Link Down Indication .........................................................................................................68

2.13

xf

oz

jr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

2.12

rs

wi

7t

1p

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

Table of Contents

2.35

Wake on Lan (WOL) Event Detection ...........................................................................................................106

2.35.1 Wake Up Frame Event ...................................................................................................................106

2.35.2 Magic Packet Event ........................................................................................................................107

2.35.3 Link Change Event .........................................................................................................................107

3

88E1510/88E1518/88E1512/88E1514 Register Description ....................................................108

3.1

PHY MDIO Register Description ...................................................................................................................108

3.2

PHY XMDIO Register Description.................................................................................................................226

4

Electrical Specifications ...........................................................................................................230

4.1

Absolute Maximum Ratings ..........................................................................................................................230

4.2

Recommended Operating Conditions ...........................................................................................................231

4.3

Package Thermal Information .......................................................................................................................232

4.3.1

Thermal Conditions for 88E1510/88E1518 48-pin, QFN Package .................................................232

4.3.2

Thermal Conditions for 88E1512/88E1514 56-pin, QFN Package .................................................233

4.4

88E1510/88E1518 Current Consumption .....................................................................................................234

4.4.1

Current Consumption AVDD18 + AVDDC18 ..................................................................................234

4.4.2

Current Consumption AVDD33.......................................................................................................234

4.4.3

Current Consumption DVDD ..........................................................................................................235

4.4.4

Current Consumption VDDO ..........................................................................................................236

Lt

Co

.

fo

zjr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

rs

wi

7t

d.

Regulators and Power Supplies ....................................................................................................................104

2.34.1 AVDD18..........................................................................................................................................105

2.34.2 AVDDC18 .......................................................................................................................................105

2.34.3 AVDD33..........................................................................................................................................105

2.34.4 DVDD..............................................................................................................................................105

2.34.5 REG_IN ..........................................................................................................................................105

2.34.6 AVDD18_OUT ................................................................................................................................105

2.34.7 DVDD_OUT ....................................................................................................................................105

2.34.8 VDDO .............................................................................................................................................105

2.34.9 Power Supply Sequencing..............................................................................................................105

4.5

88E1512 Current Consumption.....................................................................................................................237

4.5.1

Current Consumption AVDD18 + AVDDC18 ..................................................................................237

4.5.2

Current Consumption AVDD33.......................................................................................................238

4.5.3

Current Consumption DVDD ..........................................................................................................239

4.5.4

Current Consumption VDDO ..........................................................................................................240

4.6

DC Operating Conditions ..............................................................................................................................241

4.6.1

Digital Pins ......................................................................................................................................241

4.6.2

IEEE DC Transceiver Parameters ..................................................................................................242

4.7

AC Electrical Specifications ..........................................................................................................................243

4.7.1

Reset Timing...................................................................................................................................243

4.7.2

XTAL_IN/XTAL_OUT Timing ..........................................................................................................244

4.7.3

SyncE Recovered Clock Output Timing ........................................................................................245

4.7.4

LED to CONFIG Timing ..................................................................................................................246

4.8

SGMII Interface Timing .................................................................................................................................247

4.8.1

SGMII Output AC Characteristics ...................................................................................................247

4.8.2

SGMII Input AC Characteristics ......................................................................................................247

7t

x

Page 8

1p

rs

wi

Doc. No. MV-S107146-00 Rev. --

CONFIDENTIAL

Document Classification: Proprietary Information

Copyright © 2012 Marvell

February 24, 2012, Advance

1prswi7txfozjrtot1xvhoklupjx4d-i1a1tipj * Beijing Sifang Automation Co. Ltd. * UNDER NDA# 12111695

Co

.

Temperature Sensor .....................................................................................................................................103

2.34

xf

oz

jr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

2.33

1p

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

Lt

d.

Alaska® 88E1510/88E1518/88E1512/88E1514 Datasheet

Integrated 10/100/1000 Mbps Energy Efficient Ethernet Transceiver

4.10

RGMII Interface Timing .................................................................................................................................251

4.10.1 RGMII AC Characteristics...............................................................................................................251

4.10.2 RGMII Delay Timing for different RGMII Modes .............................................................................252

MDC/MDIO Timing ........................................................................................................................................254

4.12

IEEE AC Transceiver Parameters.................................................................................................................255

4.13

CLK125 .........................................................................................................................................................256

4.14

Latency Timing ..............................................................................................................................................257

4.14.1 RGMII to 1000BASE-T Transmit Latency Timing ...........................................................................257

4.14.2 RGMII to 100BASE-TX Transmit Latency Timing...........................................................................257

4.14.3 RGMII to 10BASE-T Transmit Latency Timing ...............................................................................257

4.14.4 1000BASE-T to RGMII Receive Latency Timing ............................................................................258

4.14.5 100BASE-TX to RGMII Receive Latency Timing............................................................................258

4.14.6 10BASE-T to RGMII Receive Latency Timing ................................................................................259

4.14.7 10/100/1000BASE-T to SGMII Latency Timing ..............................................................................260

4.14.8 SGMII to 10/100/1000BASE-T Latency Timing ..............................................................................261

5

Package Mechanical Dimensions ............................................................................................262

5.1

48-Pin QFN Package ....................................................................................................................................262

5.2

56-Pin QFN Package ....................................................................................................................................264

6

Order Information ......................................................................................................................266

6.1

Ordering Part Numbers and Package Markings............................................................................................266

6.1.1

Package Marking Examples ...........................................................................................................266

6.1.2

Package Marking Samples .............................................................................................................267

rs

wi

7t

fo

zjr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

Co

.

Lt

d.

4.11

7t

x

February 24, 2012, Advance

1p

rs

wi

Copyright © 2012 Marvell

CONFIDENTIAL

Document Classification: Proprietary Information

Doc. No. MV-S107146-00 Rev. -Page 9

1prswi7txfozjrtot1xvhoklupjx4d-i1a1tipj * Beijing Sifang Automation Co. Ltd. * UNDER NDA# 12111695

Lt

d.

Co

.

PTP Interface Timing ....................................................................................................................................248

4.9.1

PTP Clock Input Timing ..................................................................................................................248

4.9.2

PTP Event Request Input AC Timing (LED[1]) ...............................................................................249

4.9.3

PTP Trigger Generate Output AC Timing (LED[1]).........................................................................250

xf

oz

jr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

4.9

1p

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

Table of Contents

88E1510/88E1518/88E1512/88E1514 Device Features ....................................................................4

Table 2:

Pin Type Definitions ..........................................................................................................................18

Table 3:

Media Dependent Interface ..............................................................................................................20

Table 4:

RGMII Interface ................................................................................................................................21

Table 5:

Management Interface and Interrupt ................................................................................................21

Table 6:

LED Interface ....................................................................................................................................22

Table 7:

Clock/Configuration/Reset/I/O ..........................................................................................................22

Table 8:

Control and Reference......................................................................................................................22

Table 9:

Test...................................................................................................................................................23

Table 10:

Power, Ground & Internal Regulators ..............................................................................................23

Media Dependent Interface ..............................................................................................................26

Table 12:

RGMII Interface ................................................................................................................................27

Lt

Table 11:

d.

Table 1:

Management Interface and Interrupt ................................................................................................28

Table 14:

LED Interface ....................................................................................................................................28

fo

zjr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

Co

.

Table 13:

Table 15:

Clock/Configuration/Reset/I/O ..........................................................................................................29

Table 16:

SGMII I/Os ........................................................................................................................................29

Table 17:

Control and Reference......................................................................................................................30

Table 18:

Test...................................................................................................................................................30

Table 19:

Power, Ground, and Internal Regulators ..........................................................................................30

Table 20:

Media Dependent Interface ..............................................................................................................33

Table 21:

Management Interface and Interrupt ................................................................................................34

Table 22:

LED Interface ....................................................................................................................................35

Table 23:

Clock/Configuration/Reset/I/O ..........................................................................................................35

Table 24:

SGMII I/Os ........................................................................................................................................35

Table 25:

Control and Reference......................................................................................................................36

Table 26:

Test...................................................................................................................................................36

Table 27:

Power, Ground, and Internal Regulators ..........................................................................................36

Table 28:

No Connect .......................................................................................................................................37

Table 29:

MODE[2:0] Select .............................................................................................................................44

Table 30:

SGMII (System Interface) Operational Speed ..................................................................................49

Table 31:

Fiber Noise Filtering..........................................................................................................................50

Table 32:

RGMII Signal Mapping......................................................................................................................50

Table 33:

Fiber/Copper Auto-media Modes of Operation .................................................................................57

Table 34:

Device FIFO Status Bits ...................................................................................................................59

Reset Control Bits .............................................................................................................................60

Table 36:

Power Down Control Bits ..................................................................................................................61

Table 37:

Power Down Modes..........................................................................................................................62

Table 38:

Enhanced SGMII PHY Status ...........................................................................................................65

Table 39:

MAC Specific Control Register 1 ......................................................................................................66

Doc. No. MV-S107146-00 Rev. -Page 10

1p

rs

wi

7t

x

Table 35:

CONFIDENTIAL

Document Classification: Proprietary Information

Copyright © 2012 Marvell

February 24, 2012, Advance

1prswi7txfozjrtot1xvhoklupjx4d-i1a1tipj * Beijing Sifang Automation Co. Ltd. * UNDER NDA# 12111695

Co

.

xf

oz

jr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

rs

wi

7t

List of Tables

1p

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

Lt

d.

Alaska® 88E1510/88E1518/88E1512/88E1514 Datasheet

Integrated 10/100/1000 Mbps Energy Efficient Ethernet Transceiver

Alternate VCT™ Control ...................................................................................................................72

Table 42:

Registers for DTE Power ..................................................................................................................74

Table 43:

Error Byte Capture............................................................................................................................78

Table 44:

1.25 GHz SERDES PRBS Registers ................................................................................................79

Table 45:

Media Dependent Interface Pin Mapping .........................................................................................80

Table 46:

Late Collision Registers ....................................................................................................................82

Table 47:

LED Polarity .....................................................................................................................................84

Table 48:

Pulse Stretching and Blinking ...........................................................................................................84

Table 49:

Bi-Color LED Mixing .........................................................................................................................85

Table 50:

Modes of Operation ..........................................................................................................................86

Table 51:

Compound LED Status .....................................................................................................................87

Speed Blinking Sequence.................................................................................................................87

Table 53:

Speed Blink.......................................................................................................................................87

Table 54:

MODE 3 Behavior .............................................................................................................................88

Table 55:

MODE 4 Behavior .............................................................................................................................88

Lt

Table 52:

d.

Table 41:

PTP Control Register ........................................................................................................................91

Table 57:

Copper ..............................................................................................................................................97

Table 58:

Fiber..................................................................................................................................................97

fo

zjr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

Co

.

Table 56:

Table 59:

RGMII Output Impedance Calibration Override ............................................................................... 98

Table 60:

RGMII Output Impedance Target .................................................................................................... 99

Table 61:

Two-Bit Mapping .............................................................................................................................101

Table 62:

Configuration Mapping....................................................................................................................101

Table 63:

Configuration Definition ..................................................................................................................102

Table 64:

Serial Management Interface Protocol ...........................................................................................103

Table 65:

Temperature Sensor .......................................................................................................................103

Table 66:

Power Supply Options - Integrated Switching Regulator (REG_IN) ...............................................104

Table 67:

Power Supply Options - External Supplies .....................................................................................104

Table 68:

SRAM Data Structure .....................................................................................................................106

Table 69:

Register Types............................................................................................................................... 108

Table 70:

Register Map ..................................................................................................................................109

Table 71:

Copper Control Register ................................................................................................................ 113

Table 72:

Copper Status Register ................................................................................................................. 115

Table 73:

PHY Identifier 1.............................................................................................................................. 117

Table 74:

PHY Identifier 2.............................................................................................................................. 117

Table 75:

Copper Auto-Negotiation Advertisement Register ......................................................................... 118

Table 76:

Copper Link Partner Ability Register - Base Page ......................................................................... 120

Copper Auto-Negotiation Expansion Register ............................................................................... 122

Table 78:

Copper Next Page Transmit Register ............................................................................................ 122

Table 79:

Copper Link Partner Next Page Register ...................................................................................... 123

Table 80:

1000BASE-T Control Register ....................................................................................................... 123

Table 81:

1000BASE-T Status Register ........................................................................................................ 125

Table 82:

XMDIO MMD control Register ....................................................................................................... 126

Table 83:

XMDIO MMD address data Register ............................................................................................. 126

February 24, 2012, Advance

1p

rs

wi

Copyright © 2012 Marvell

7t

x

Table 77:

CONFIDENTIAL

Document Classification: Proprietary Information

Doc. No. MV-S107146-00 Rev. -Page 11

1prswi7txfozjrtot1xvhoklupjx4d-i1a1tipj * Beijing Sifang Automation Co. Ltd. * UNDER NDA# 12111695

Lt

d.

Co

.

SGMII Auto-Negotiation modes ........................................................................................................67

xf

oz

jr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

rs

wi

7t

1p

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

Table 40:

List of Tables

Table 85:

Copper Specific Control Register 1 ............................................................................................... 127

Table 86:

Copper Specific Status Register 1 ................................................................................................. 128

Table 87:

Copper Specific Interrupt Enable Register .................................................................................... 130

Table 88:

Copper Interrupt Status Register ................................................................................................... 131

Table 89:

Copper Specific Control Register 2 ............................................................................................... 133

Copper Specific Receive Error Counter Register .......................................................................... 133

Table 91:

Page Address ................................................................................................................................ 134

Table 92:

Global Interrupt Status ................................................................................................................... 134

Table 93:

Copper Specific Control Register 3 ............................................................................................... 134

Table 94:

Fiber Control Register.................................................................................................................... 135

Table 95:

Fiber Status Register ..................................................................................................................... 137

Table 96:

PHY Identifier................................................................................................................................. 139

Table 97:

PHY Identifier................................................................................................................................. 139

Table 98:

Fiber Auto-Negotiation Advertisement Register - 1000BASE-X Mode (Register 16_1.1:0 = 01) .. 139

Table 99:

Fiber Auto-Negotiation Advertisement Register - SGMII (System mode) (Register 16_1.1:0 = 10).....

141

Co

.

Lt

d.

Table 90:

Table 100: Fiber Auto-Negotiation Advertisement Register - SGMII (Media mode) (Register 16_1.1:0 = 11) 142

fo

zjr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

Table 101: Fiber Link Partner Ability Register - 1000BASE-X Mode (Register 16_1.1:0 = 01) ....................... 142

Table 102: Fiber Link Partner Ability Register - SGMII (System mode) (Register 16_1.1:0 = 10)................... 143

Table 103: Fiber Link Partner Ability Register - SGMII (Media mode) (Register 16_1.1:0 = 11)..................... 143

Table 104: Fiber Auto-Negotiation Expansion Register................................................................................... 144

Table 105: Fiber Next Page Transmit Register ............................................................................................... 145

Table 106: Fiber Link Partner Next Page Register .......................................................................................... 146

Table 107: Extended Status Register .............................................................................................................. 146

rs

wi

7t

Table 108: Fiber Specific Control Register 1 ................................................................................................... 147

Table 109: Fiber Specific Status Register ....................................................................................................... 148

Table 110: Fiber Interrupt Enable Register...................................................................................................... 149

Table 111: Fiber Interrupt Status Register....................................................................................................... 150

Table 112: Fiber Receive Error Counter Register ........................................................................................... 151

Table 113: PRBS Control ................................................................................................................................ 151

Table 114: PRBS Error Counter LSB .............................................................................................................. 152

Table 115: PRBS Error Counter MSB ............................................................................................................. 152

Table 116: Fiber Specific Control Register 2 ................................................................................................... 152

Table 117: MAC Specific Control Register 1 ................................................................................................... 153

Table 118: MAC Specific Interrupt Enable Register ........................................................................................ 155

Table 119: MAC Specific Status Register........................................................................................................ 155

Table 120: Copper RX_ER Byte Capture ........................................................................................................ 156

Table 121: MAC Specific Control Register 2 ................................................................................................... 156

Table 122: RGMII Output Impedance Calibration Override ............................................................................. 157

Table 123: RGMII Output Impedance Target .................................................................................................. 158

Table 124: LED[2:0] Function Control Register ............................................................................................... 159

Table 125: LED[2:0] Polarity Control Register ................................................................................................. 160

Doc. No. MV-S107146-00 Rev. -Page 12

1p

rs

wi

7t

x

Table 126: LED Timer Control Register........................................................................................................... 161

CONFIDENTIAL

Document Classification: Proprietary Information

Copyright © 2012 Marvell

February 24, 2012, Advance

1prswi7txfozjrtot1xvhoklupjx4d-i1a1tipj * Beijing Sifang Automation Co. Ltd. * UNDER NDA# 12111695

Co

.

Extended Status Register .............................................................................................................. 126

xf

oz

jr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

Table 84:

1p

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

Lt

d.

Alaska® 88E1510/88E1518/88E1512/88E1514 Datasheet

Integrated 10/100/1000 Mbps Energy Efficient Ethernet Transceiver

Table 128: RGMII RX_ER Byte Capture ......................................................................................................... 162

Table 129: Advanced VCT TX to MDI[0] Rx Coupling ..................................................................................... 163

Table 130: Advanced VCT TX to MDI[1] Rx Coupling ..................................................................................... 163

Table 131: Advanced VCT TX to MDI[2] Rx Coupling ..................................................................................... 165

Table 132: Advanced VCT TX to MDI[3] Rx Coupling ..................................................................................... 166

Table 133: 1000BASE-T Pair Skew Register .................................................................................................. 166

Table 134: 1000BASE-T Pair Swap and Polarity ............................................................................................ 167

Table 135: Advance VCT Control .................................................................................................................... 167

Table 136: Advanced VCT Sample Point Distance ......................................................................................... 168

Table 137: Advanced VCT Cross Pair Positive Threshold .............................................................................. 169

Table 138: Advanced VCT Same Pair Impedance Positive Threshold 0 and 1............................................... 169

Table 139: Advanced VCT Same Pair Impedance Positive Threshold 2 and 3............................................... 169

Table 140: Advanced VCT Same Pair Impedance Positive Threshold 4 and Transmit Pulse Control ............ 170

d.

Table 141: Copper Port Packet Generation..................................................................................................... 171

Lt

Table 142: Copper Port CRC Counters ........................................................................................................... 172

Co

.

Table 143: Checker Control ............................................................................................................................. 172

Table 144: Copper Port Packet Generation..................................................................................................... 172

fo

zjr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

Table 145: General Control Register ............................................................................................................... 172

Table 146: Late Collision Counters 1 & 2 ........................................................................................................ 173

Table 147: Late Collision Counters 3 & 4 ........................................................................................................ 173

Table 148: Late Collision Window Adjust/Link Disconnect .............................................................................. 174

Table 149: Misc Test ....................................................................................................................................... 174

Table 150: Misc Test: Temperature Sensor Alternative Reading .................................................................... 175

Table 151: PHY Cable Diagnostics Pair 0 Length ........................................................................................... 175

rs

wi

7t

Table 152: PHY Cable Diagnostics Pair 1 Length ........................................................................................... 176

Table 153: PHY Cable Diagnostics Pair 2 Length ........................................................................................... 176

Table 154: PHY Cable Diagnostics Pair 3 Length ........................................................................................... 176

Table 155: PHY Cable Diagnostics Results .................................................................................................... 176

Table 156: PHY Cable Diagnostics Control ..................................................................................................... 177

Table 157: Advanced VCT Cross Pair Negative Threshold............................................................................. 178

Table 158: Advanced VCT Same Pair Impedance Negative Threshold 0 and 1 ............................................. 178

Table 159: Advanced VCT Same Pair Impedance Negative Threshold 2 and 3 ............................................. 178

Table 160: Advanced VCT Same Pair Impedance Negative Threshold 4 ....................................................... 179

Table 161: PTP Port Configuration Register 0 ................................................................................................ 179

Table 162: PTP Port Configuration Register 1 ................................................................................................ 180

Table 163: PTP Port Configuration Register 2 ................................................................................................ 181

Table 164: PTP Port Configuration Register 3 ................................................................................................ 183

Table 165: PTP Arrival 0 Time Port Status Register ....................................................................................... 184

Table 166: PTP Arrival 0 Time Register Bytes 1 & 0 ....................................................................................... 185

Table 167: PTP Arrival 0 Time Register Bytes 3 & 2 ....................................................................................... 186

Table 168: PTP Arrival 0 Sequence Identifier Register ................................................................................... 187

Table 169: PTP Arrival 1 Time Port Status Register ....................................................................................... 187

Copyright © 2012 Marvell

February 24, 2012, Advance

1p

rs

wi

7t

x

Table 170: PTP Arrival 1 Time Register Bytes 1 & 0 ....................................................................................... 188

CONFIDENTIAL

Document Classification: Proprietary Information

Doc. No. MV-S107146-00 Rev. -Page 13

1prswi7txfozjrtot1xvhoklupjx4d-i1a1tipj * Beijing Sifang Automation Co. Ltd. * UNDER NDA# 12111695

Lt

d.

Co

.

xf

oz

jr

M tot1

AR x

VE vh

LL okl

COupj

NF x4d

ID -i1

EN a1

TI tip

AL j *

, U Be

ND ijin

ER g

NDSifa

A# ng

12 Au

11 tom

16 a

95 tio

n

Table 127: PTP LED Function Control ............................................................................................................ 162

1p

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

List of Tables

Table 172: PTP Arrival 1 Sequence Identifier Register ................................................................................... 190

Table 173: PTP Departure Time Port Status Register..................................................................................... 190

Table 174: PTP Departure Time Register Bytes 1 & 0 .................................................................................... 191

Table 175: PTP Departure Time Register Bytes 3 & 2 .................................................................................... 192

Table 176: PTP Departure Sequence Identifier Status Register ..................................................................... 193

Table 177: PTP Port Discard Counter Register ............................................................................................... 193

Table 178: TAI Global Configuration Register 0 .............................................................................................. 195

Table 179: TAI Global Configuration Register 1 .............................................................................................. 198

Table 180: TAI Global Configuration Register 2 .............................................................................................. 198