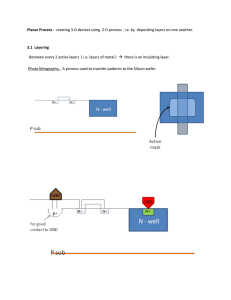

InP-based mixed device (HEMT/HBT) technology on planar substrate for high performance mixed-signal and optoelectronic circuits an optical micrograph of such a HEMT. The process then continues with the fabrication of HBTs and the passive elements (TaN thin film resistors, MIM capacitors) while making sure that the HEMTs are masked. Fabrication is finished by forming the interconnects. K. Kızılo glu, M.W. Yung, H.C. Sun, S. Thomas III, M.B. Kardos, R.H. Walden, J.J. Brown and W.E. Stanchina Indexing terms: Indium phosphide, Integrated optoelectronics The authors report the first successful demonstration of an integrated circuit process on planar InP substrates that incorporates a stacked single layer MBE growth of HEMTs and HBTs. In this process, the HBT layers are patterned and selectively wet etched to expose the HEMT layers after the MBE growth is completed. The authors report functional HEMTs and HBTs on the same wafer, with pertinent DC and microwave measurements. We report the first successful demonstration of an integrated circuit process on planar InP substrates that incorporates a single, stacked layer molecular beam epitaxy (MBE) growth of high electron mobility transistors (HEMTs) and heterojunction bipolar transistors (HBTs). We believe that this approach to mixed device integration on planar substrates with stacked epitaxial layers is robust and versatile, and will enable the implementation of ICs for such diverse system applications as optoelectronics, communications and radar. The availability of a mixed device technology will not only exploit the advantages of each device type, e.g. low noise HEMTs together with high transconductance HBTs, but will also encourage innovative circuit design. Fig. 2 Comparison between patterned and planar growth processes a Patterned growth b Planar growth Process steps are: a (i) pattern substrate, (ii) grow device layers by MBE, (iii) etch back and expose HEMT layers; b (i) grow device layers by MBE on planar substrate, (ii) etch back and expose HEMT layers Fig. 3 Photographs of 0.12 × 50µm2 HEMT a After completion of ohmic metal b After interconnection with HBTs and other passive elements Fig. 1 HEMT/HBT stacked layer structure Previous approaches using selective MBE [1, 2], and pre-patterning the substrate before MBE growth [3] have been reported for HEMT/HBT integration. In the process reported here, however, HBT layers are patterned and selectively etched to expose the HEMT layers after the MBE growth is completed. The MBE grown layer structure is shown in Fig. 1. Fig. 2 contrasts the current approach with that of pre-patterning the substrate. Advantages of the current approach include growth on a planar, epi-ready substrate (low defect density) and simplified process steps. The subsequent steps are a combination of our state-of-the-art HEMT and HBT processes [4 – 6]. First, discrete HEMTs are fabricated. Even though the HEMTs are placed near to 2 µm below the surface of the wafer, E-beam written gates with LG = 0.12 µm are achieved. Fig. 3 shows ELECTRONICS LETTERS 20th November 1997 The HEMT characteristics were measured after they were completed, and again at the end of the whole process. The characteristics were found to remain stable which indicates the compatibility of the HEMT and subsequent HBT and passive element fabrication sequences. 0.12 × 50 µm HEMTs demonstrate gM, MAX . 800mS/mm and ID, FULL . 500mA/mm. Fig. 4 shows ID and gM against VDS for such a device. S-parameter measurements performed on etch-FETs with DC gM, MAX . 650mS/mm yielded fT . 90GHz and fMAX . 110GHz. Fig. 5 shows the IC against VCE for a 2 × 20 µm HBT in the common emitter configuration. β . 50 is observed. Biased at JC . 25kA/cm2 and VCE = 1.2V, this device has FT . 75GHz and fMAX . 100GHz. These DC and microwave results are comparable to those of our baseline stand-alone devices. As a feasibility study for this technology, high-sensitivity pin photodetector/HEMT/HBT integrated optoelectronic receivers have been fabricated, where the pin photodiodes comprise the reverse- Vol. 33 No. 24 biased base-collector junction of the HBTs. The performance of these circuits is currently being evaluated and will be reported later. In conclusion, we have reported the first successful demonstration of an integrated circuit process on planar InP substrates that incorporates a single stacked layer MBE growth of HEMTs and HBTs. We achieved integration by patterning and selectively wet etching the HBT layers to expose the HEMT layers after the MBE growth is completed. Both the HEMTs and the HBTs showed DC and microwave performances similar to those of our baseline technologies, thereby indicating no loss of performance of devices due to the combined processing and confirming the feasibility of the reported approach. Acknowledgments: We would like to thank A. Arthur, Y. Brown, J. Duvall, W. Hoefer, C. Hooper, H. Karatnicki , R. Martinez and M. Montes for their help in processing, R. Wilson for ion implantation, M. Le and P. Hashimoto for E-beam lithography, D. Harvey for his help with measurements and A.E. Schmitz and M. Hafizi for useful discussions. © IEE 1997 Electronics Letters Online No: 19971384 2 October 1997 K. Kızılo g lu, M.W. Yung, H.C. Sun, S. Thomas III, M.B. Kardos, R.H. Walden, J.J. Brown and W.E. Stanchina (Hughes Research Laboratories, 3011 Malibu Canyon Road, Malibu, CA 90265, USA) E-mail: kursad@hrl.com H.C. Sun: currently at Rockwell Science Center, 1049 Camino Dos Rios, Thousand Oaks, CA 91358, USA References Fig. 4 Characteristics of 0.12 × 50µm2 HEMT 1 a gM and ID against VGS (VDS = 0.8V) b ID against VDS, VGS from –0.4 to 0.6V in steps of 0.2V 2 3 4 5 6 Fig. 5 IC against VCE for 2 × 20µm2 HBT IB: from 0 to 250µA in steps of 50µA ELECTRONICS LETTERS 20th November 1997 Vol. 33 STREIT, D.C., UMEMOTO, D.K., KOBAYASHI, K.W., and OKI, A.K.: ‘Monolithic HEMT-HBT integration by selective MBE’, IEEE Trans. Electron Devices, 1995, 42, (4), pp. 618–623 WANG, H., LIN, E., LO, D.C.W., TAI, R., TRAN, L., COWLES, J., CHEN, Y.C., BLOCK, T., LIU, P.H., YEN, H.C., and STAMPER, K.: ‘A monolithic 24GHz frequency source using InP-based HEMT-HBT integration technology’. IEEE Radio Frequency Integrated Circuits Symp. Dig., 1997, pp. 79–81 STANCHINA, W.E., BROWN, J.J., HAFIZI, M., WALDEN, R.H., SUN, H.C., and RODWELL, M.: ‘InP-based mixed signal/mixed device technology’. Int. Conf. GaAs Manufacturing Technol. Dig., 1996, pp. 160–163 STANCHINA, W.E., JENSEN, J.F., WALDEN, R.H., HAFIZI, M., SUN, H.C., LIU, T., RAGHAVAN, G., ELLIOTT, K.E., KARDOS, M., SCHMITZ, A.E., BROWN, Y.K., MONTES, M.E., and YUNG, M.: ‘An InP-based HBT fabrication for high-speed digital, analog, mixed-signal, and optoelectronic ICs’. IEEE GaAs Integrated Circuit Symp. Tech. Dig., 1995, pp. 31–34 BROWN, J.J., SCHMITZ, A.E., LE, M., and HU, M.: ‘High speed InP-based IC fabrication technology for both commercial and military system insertion’. MRS Spring Meeting Abstracts, 1997, pp. 65 MISHRA, U.K., BROWN, A.S., JELLOIAN, L.M., THOMPSON, M., NGUYEN, L.D., and ROSENBAUM, S.E.: ‘Novel high performance selfaligned 0.15 micron long T-gate AlInAs-GaInAs HEMTs’. Int. Electron Dev. Meeting Tech. Dig., 1989, pp. 101–104 No. 24