Fall 2013

Page 1 of 150

ECE 401 Notes

Power Electronics

Part A

Chapters 1 - 17

John Salmon and Ali Khajehoddin

Fall 2015

Copyright © August 2015 by the University of Alberta

All rights reserved. No part of this publication may be reproduced, stored in a retrieval

system, or transmitted, in any form or by any means, electronic, mechanical, photocopying,

recording or otherwise, without the prior permission of the University of Alberta.

ECE Dept. University of Alberta

Page 1 of 150

Fall 2013

Page 2 of 150

Contents

Exam Formulas ........................................................................................................................................................5

1

Power Semiconductors ........................................................................................................................................16

1.1 Technical specifications of the main power semiconductor types ........................................................16

1.2 V-I-F ratings of the main power semiconductors.....................................................................................17

1.3 SiC and GaN Devices ......................................................................................................................................18

2

Diodes.......................................................................................................................................................................19

2.1 Diode Model......................................................................................................................................................19

2.2 Series Connection of Diodes .......................................................................................................................20

2.3 Parallel Connection of Diodes ......................................................................................................................21

2.4 Examples ..........................................................................................................................................................22

3

Thyristor ................................................................................................................................................................24

3.1 Power Semiconductor Structure ................................................................................................................24

3.2 Power Semiconductor Switching Characteristics..................................................................................25

3.3 Power Semiconductor V-I Characteristics .............................................................................................25

3.4 Gate-Drives .....................................................................................................................................................27

3.5 Examples ..........................................................................................................................................................29

4

BJT and MOSFET ...............................................................................................................................................30

4.1 BJT Transistor ................................................................................................................................................31

4.2 MOSFET Power Semiconductor .................................................................................................................34

4.3 Summary ..........................................................................................................................................................37

5

MOSFET & BJT Input Drivers & Snubbers ...............................................................................................39

5.1 BJT ....................................................................................................................................................................39

5.2 MOSFET ..........................................................................................................................................................42

6

IGBT ........................................................................................................................................................................48

6.1 Semiconductor Device...................................................................................................................................49

6.2 Gate Drive ........................................................................................................................................................51

6.3 Miller-Effect ..................................................................................................................................................52

6.4 Short-circuit Behaviour ...............................................................................................................................53

6.5 Problems associated with the high switching speeds of IGBTs ........................................................55

7

SiC and GaN ..........................................................................................................................................................57

7.1 General characteristics of the new devices ....................................................................................................57

7.2 Timelines for the introduction of the new technologies ................................................................................59

7.3 Market for the new devices .............................................................................................................................................................61

7.4 Application Examples ..........................................................................................................................................................................63

ECE Dept. University of Alberta

Page 2 of 150

Fall 2013

Page 3 of 150

7.5 Predictions of the future for the new devices ......................................................................................65

8

AC/DC/RMS of Waveforms .............................................................................................................................66

8.1 RMS of a repetitive voltage waveform v(t) .............................................................................................66

8.2 RMS of a repetitive current waveform i(t) ............................................................................................67

8.3 RMS components of a repetitive voltage waveform v(t) .....................................................................68

8.4 AC/DC and RMS components of a repetitive current waveform i(t)................................................69

8.5 RMS/DC/AC of a general periodic pulse current waveform ..............................................................70

8.6 Examples ..........................................................................................................................................................72

9

Steady-State Properties of Power, L & C .................................................................................................76

9.1 Power Dissipation and Power Flow ..............................................................................................................76

9.2 Power Absorbed in a DC Voltage Source .................................................................................................76

9.3 Power drawn from a Sinusoidal Voltage Source .....................................................................................77

9.4 Inductor ...........................................................................................................................................................79

9.5 Capacitor ..........................................................................................................................................................79

10 1-phase Diode Rectifiers with R-loads ........................................................................................................81

10.1 Half-Wave With an R-Load ........................................................................................................................81

10.2 1-phase Full-Wave Diode Rectifier: R-load ...........................................................................................82

10.3 R-load Vs is small (e.g. 5-30 V, VDon taken into account, θc < 180°) ..................................................84

10.4 R-load Vs is large (Vs >> VDon, say Vs > 30V, and assume θc = 180°, α = 0°) .......................................85

10.5 R-E load (conduction angle = θc , zero current angle α) .....................................................................87

10.6 Examples ........................................................................................................................................................89

11 1-phase Full-Wave Diode Rectifiers ............................................................................................................94

11.1 Full-Wave with an R-L load .........................................................................................................................94

11.2 Full-Wave with an LC output filter ..........................................................................................................94

11.3 Full-Wave with an R-L output filter and a dc voltage .........................................................................94

11.4 Examples .........................................................................................................................................................95

12 1-phase Diode Rectifier with a C-Filter ...................................................................................................101

12.1 Circuit Operation.........................................................................................................................................101

12.2 Analysis Assumptions ................................................................................................................................102

12.3 Capacitor peak-peak ripple voltage and rms of the ripple voltage ...............................................103

12.4 Rectifier Average Output Voltage ........................................................................................................104

12.5 Diode Conduction Angle ............................................................................................................................105

12.6 Peak Charging Current .............................................................................................................................106

12.7 Peak Capacitor Charging Current and the average rectifier output current..............................106

12.8 Supply rms current and capacitor rms current ..................................................................................107

12.9 Example of the Process for Circuit Design .........................................................................................107

12.10 Commonly used Rectifier Configurations ...........................................................................................108

ECE Dept. University of Alberta

Page 3 of 150

Fall 2013

Page 4 of 150

13 Design Examples: 1-ph Diode Rectifier with a C Filter ......................................................................109

Examples ...............................................................................................................................................................109

14 Power Quality Definitions for Utility Rectifiers .....................................................................................115

14.1 Concept of steady-state power quality .................................................................................................115

14.2 Power Factor ................................................................................................................................................116

14.3 Harmonic Distortion...................................................................................................................................117

14.4 1-phase Rectifier Example .......................................................................................................................118

14.5 Examples ......................................................................................................................................................120

15 3-phase diode rectifiers .................................................................................................................................124

15.1 Definitions of waveforms used in the 3-phase voltage supply ........................................................124

15.2 Operation of the basic 3-phase dido rectifier ..................................................................................125

15.3 Analysis of the Output voltage Waveform ..........................................................................................127

15.4 Ideal performance of the 3-phase diode rectifier with an LC output filter & L→∞ ...............128

16 3-phase diode rectifier with an LC DC filter ..........................................................................................131

Examples ................................................................................................................................................................131

17 3-phase diode rectifiers using ac reactors .............................................................................................136

17.1 Operation with no ac reactors (Ls = 0, Ldc = 0) ....................................................................................136

17.2 Operation when using ac reactors (Ldc = 0) .........................................................................................137

17.3 Performance when using ac reactors and assuming Ldc = 0..............................................................138

17.4 Performance when using ac reactors and assuming Ldc = ∞ .............................................................140

17.5 Examples ......................................................................................................................................................142

Sample Mid-Term ....................................................................................................................................................145

ECE Dept. University of Alberta

Page 4 of 150

Fall 2013

Page 5 of 150

Exam Formulas

Waveforms Calculations and Power Quality

(a) 1-phase ac supply harmonics and power quality

Power Factor: PF =

P I1

= cosφ1 = CDF × DPF

S Is

⎛ E + VDon ⎞

α = a sin ⎜

, θc = π − 2α, θoc = (180 − 2α ) °

⎝ 2Vs ⎟⎠

Vs2

2 2

α⎞

2 ⎛1

sin 2α −

Vs ( E + VDon ) cosα + ⎡Vs2 + ( E + VDon ) ⎤ ⎜ − ⎟

⎣

⎦⎝ 2 π ⎠

2π

π

Io,rms =

1

R + rD

Apparent Power: S = Vs Is

Io,dc =

Is = I12 + I22 + I23 + I24 + I25 + .... , Is = I12 + I2H , IH = I22 + I23 + I24 + ....

I

Current Distortion Factor: CDF = 1

Is

I

Displacement Power Factor: DPF = FPF = cosφ1 = 1r

I1

IH

IH

% , THD F = 100

%

ac supply current: THD R = 100

IS

I1

1 ⎡ 2

⎛ 1 α⎞ ⎤

Vs cosα − [ E + VDon ] ⎜ − ⎟ ⎥

⎢

⎝ 2 π⎠⎦

R + rD ⎣ π

(ii) Full-wave R/E load (R-load has E = 0) (4 diodes)

Real Power Flow: P = Vs Is1r = Vs I1 cosφ1

THD F

THD R =

CDF =

1+ THD 2F

1

1+ THD 2F

, THD F =

THD R

1− THD 2R

, CDF = 1− THD

2

R

(b) Basic Waveform Calculation

Harmonics of a square-wave of voltage magnitude Vo:

Vn,pk = Vo

4

2 2

, n = 1, 3,5, 7,9,11,13 etc... , Vn,rms = Vo

nπ

nπ

Power drawn from a dc source Vdc: P = Vdc × Idc

Power drawn from an ac source V1: P = V1 × I1 × cosφ1

Power dissipated in a resistor V1: PR = I2rms × R

RMS of a voltage with 2 components V1(t), V2(t):

2

2

Vrms = V1,rms

+ V2,rms

= V12 + V22

2

+ I22,rms + I23,rms + ...

In general: Irms = I2dc + I1,rms

⎛ E + 2VDon ⎞

α = a sin ⎜

, θc = π − 2α, θoc = (180 − 2α ) °

2Vs ⎟⎠

⎝

Vs2

4 2

2α ⎞

2 ⎛

sin 2α −

Vs ( E + 2VDon ) cosα + ⎡Vs2 + ( E + 2VDon ) ⎤ ⎜ 1−

⎟

⎣

⎦⎝

π

π

π ⎠

Io,rms =

1

R + 2rD

Io,dc =

1 ⎡2 2

⎛ 2α ⎞ ⎤

Vs cosα − [ E + 2VDon ] ⎜ 1−

⎢

⎟⎥

⎝

R + 2rD ⎣ π

π ⎠⎦

(iii) Half-Wave Approx Approach R-Load

Vo,dc ≈ 0.45Vs − δ cVDon , Vo,rms ≈ Vs

2 − δ c VDon

(iv) Full-Wave Approx Approach R-Load

Vo,dc ≈ 0.9Vs − 4δ cVDon , Vo,rms ≈ Vs − 2δ c × 2VDon

(b) R-Load neglecting θc and α

Io,rms =

Vo.rms

V

, Io,dc = o.dc

R

R

(i) Half-Wave R-Load: Vo,dc ≈

2

V − VDon

Vs − 0.5VDon , Vo,rms ≈ s

π

2

(ii) Full-Wave R-Load: Vo,dc ≈

2 2

Vs − 2VDon = 0.9Vs − 2VDon ,

π

Vo,rms ≈ Vs − 2VDon

1-Phase diode rectifier continuous conduction

Irms = I2dc + I12 + I22 + I23 + ... = I2dc + I12 + I2H

For simplicity, the equations given neglect VDon

IH = I22 + I23 + I24 + ... , Iac = I12 + I22 + I23 + ... = I2rms − I2dc

Z = R 2 + ( ωL ) , tanφ =

A current ramping between Ip and Im has an rms/dc/ac:

(a) Full-Wave R/L Load continuous conduction

Irms =

I +I

1 2

Ip + Ip Im + I2m , Idc = p m , Iac = I2rms − I2dc

3

2

(

)

A current lasting for δ of a cycle has an rms/dc/ac of:

Irms =

⎛I +I ⎞

δ 2

Ip + Ip Im + I2m , Idc = δ ⎜ p m ⎟ , Iac = I2rms − I2dc

⎝ 2 ⎠

3

(

)

2

2 2

VS = 0.9VS , VO,rms = VS ,

π

4

VOn

VOn = 2

VS n = 2, 4,6,8.... IOn =

n = 2, 4,6,.... ,

2

2

n −1 π

R + ( nωL )

VO,dc =

(

IO,ac ≈

1-phase diode rectifier: R and R-E load

(a) Including the effect of θc and α

(i) Full-wave R/E load (R-load has E = 0) (2 diodes)

ECE Dept. University of Alberta

ωL

R

)

VO2

R 2 + ( 2ωL )

2

(b) Full-Wave LC filter, R load, continuous conduction

! VO,dc =

2 2

VS = 0.9VS ,! VO,rms = VS

π

Page 5 of 150

Fall 2013

! VOn =

(

Page 6 of 150

(e) Commutation Overlap

4

V

VS n = 2, 4,6,8.... , ! IOn = On n = 2, 4,6,8....

nωL

n −1 π

2

)

4

V

VS ≈ 0.424VS , ! IO,ac ≈ IO2 = O2

3π

2ωL

(c) Full-Wave R./L Load, cont. cond., ripple free

FPF = cos Φ1 = cos α

⎛

2IDC Xs ⎞

! µ = a cos ⎜ 1−

, VO,dc = 1.35VLL − 0.955IDC XS

VLL: ⎟⎠

⎝

! VO2 =

! Pin =

! DPF =

1+ cosµ

, PF ≈ 0.955 × DPF

2

SCR Snubber

2 2

VSIDC , IS = IDC , S = VSIDC

π

! ωo =

Pin 2 2

2 2

=

, CDF =

, DPF = 1

S

π

π

2 2

8

! IS1 =

IDC , IH = IDC 1− 2

π

π

THDF = 0.48, THDR = 0.44

! PF =

!ω =

1

R

, α=

,τ = RC

2L

LC

1

R2

α R C

− 2 = ω o 1− δ 2 , δ =

=

=

LC 4L

ωo 2 L

R

L

2

C

(d) Full-Wave Capacitor Smoothed

I ⎛ θ ⎞

V

! VR = DC ⎜ 1− c ⎟ , ! VR,rms = R

2fSC ⎝

π⎠

2 3

When the damping constant has ẟ < 0.5 (underdamped):

dv

/dt = maximum when cos ωt = ẟ( 3 - 4ẟ2 )

⎛ −δ ⎞

VR

⎛

V ⎞

− 2VDon , ! Vm = 2VS ,

θc = 2 × a cos ⎜ 1− R ⎟

2

2VS ⎠

⎝

⎛ 180 ⎞

2θ

! Im = 1.57 ⎜ o ⎟ Idc , ! IO,dc = 2c Im , ! IO,dc = IDC

π

⎝ θc ⎠

⎜

⎟ a cos ⎡⎣δ( 3−4δ ) ⎤⎦

2

dVo

(max) = E × ω o × e ⎝ 1−δ ⎠

dt

When ẟ > 0.5 (critically or over-damped):

dVo

4δ 2

E×R

1

(max) = E × ω o × 2δ =

E=

, δ≥

dt

τ

L

3

4δ 2 E

L × Smax

δ ≥ 0.5 : C =

, R=

R × Smax

VS

! VDC = Vm −

⎛ 180 ⎞

⎛ 180 ⎞

! IO,rms = IS = IDC 1.234 ⎜ o ⎟ , ! IC = IS = IDC 1.234 ⎜ o ⎟ − 1

θ

⎝ c ⎠

⎝ θc ⎠

Ip =

⎛ −δ ⎞

⎟ a cos[ δ ]

1−δ 2 ⎠

⎜

E

× 2δ × e ⎝

R

⎛

Vo,max = E × ⎜ 1+ e

⎝

3-phase diode rectifier

2δ

1−δ 2

2

, For δ ≤ 1, Ip ≈

a cos ⎡⎣ 2δ 2 −1⎤⎦

E

2δ

×

R

1− δ 2

⎞

2

⎟ , PR = CVpk fs

⎠

(a) Performance when the output current is ripple-free

3

! S = 2VLL IDC , ! PF = , ! Vo,dc = 1.35VLL − 2VDon

π

2

6

IDC , ! IH = 0.24IDC , ! IS =

IDC

! In =

nπ

3

! THD F = 31% , ! THD R = 31%

(b) Continuous Conduction Operation

3 2

3 3

VLL − 2VDon , ! Vo,rms = VLL 1+

− 2VDon

π

2π

6

6

5.5

! Von = 2

VLL ,n = 6, 12, 18,... ,! Vo6 =

VLL ≈

VLL

35π

100

n −1 π

! Vo,dc =

(

)

(c) half-wave

3

VLL − VDon

! Vo,dc =

2π

(d) definition of base values for using per-unit

! Vbase = VLL , fbase = 60 Hz, Pbase = rectifier input power

! Ibase =

Pbase

VLL

V2

, X base = R base =

= LL

3VLL

3Ibase Pbase

! L base =

2

VLL

L

, L pu =

2πfs Pbase

L base

ECE Dept. University of Alberta

!

Page 6 of 150

Fall 2013

Page 7 of 150

ECE Dept. University of Alberta

Page 7 of 150

Fall 2013

Page 8 of 150

ECE Dept. University of Alberta

Page 8 of 150

Fall 2013

Page 9 of 150

1-phase full-wave regulator

R-load: Vo,rms = VS

π−α+

π

sin 2α

2

Inr =

Ib ⎛ sin ( n + 1) α sin ( n − 1) α ⎞

+

n = 3, 5, 7,...

π ⎜⎝

n +1

n − 1 ⎟⎠

Ini =

Ib ⎛ 1− cos ( n − 1) α 1− cos ( n + 1) α ⎞

−

⎟⎠ n = 3, 5, 7,...

π ⎜⎝

n −1

n +1

I1r =

Ib ⎛

sin 2α ⎞

Ib ⎛ cos 2α − 1 ⎞

VS

⎜π−α+

⎟ , I1i = ⎜⎝

⎟⎠ , Ib =

π⎝

2 ⎠

π

2

R

R-L Load: VO,rms = VS

β − α sin 2β − sin 2α

−

π

2π

solve for β where: sin (β − φ ) − sin ( α − φ ) e

(α−β)

tanφ

=0

⎛ ωL ⎞

φ = a tan ⎜

⎝ R ⎟⎠

3-phase ac regulators: Y connected R-load

pu

VO,rms

= 1−

VOpu

3α 3

+

sin 2α,0 ≤ α ≤ 60°

2π 4π

pu

VO,rms

=

1 9

3 3

+

sin 2α +

cos 2α, 60° ≤ α ≤ 90°

2 8π

8π

pu

VO,rms

=

5 3α 3

3 3

−

+

sin 2α +

cos 2α, 90° ≤ α ≤ 150°

4 2π 8π

8π

ECE Dept. University of Alberta

Thyristor Firing angle - α

Heatsinks

t j − t a = PD × ⎡⎣ R jc + R ca / / ( R ch + R ha ) ⎤⎦

tj = junction temperature: °C, tc = case temperature: °C

th = heatsink temperature: °C, ta = ambient temperature:

Rjc = junction to case thermal resistance °C/W

Rca = case to ambient thermal resistance °C/W

Rch = case to heatsink thermal resistance °C/W

Rha = heatsink to ambient thermal resistance °C/W

PD = power semiconductor power loss - W

Page 9 of 150

Fall 2013

Page 10 of 150

Performance of 1-phase AC regulator with an R-L Load

ECE Dept. University of Alberta

Firing Angle -

α

Firing Angle -

α

Page 10 of 150

Fall 2013

Page 11 of 150

Power Semiconductor Losses

Ip = Io +

ΔIo

ΔI

, Im = Io − o

2

2

(b) diode: PD = I2diode,rms rD + Idiode,dcVDon

1-phase H-bridge PWM Inverter

ΔIo

ΔI

, Im = Io − o

2

2

E

×

I

E × Im

p

P1 =

× t1 × fc watts, P2 =

× t 2 × fc watts

2

2

E × IO

Psw =

fc ( t1 + t 2 ) watts, if Ip = Im = IO

2

conduction losses

I +I

Pon = Von × Idevice,dc , Idevice,dc = δ p m

2

ma = maximum amplitude modulation depth = vs,pk/vc,pk

ma = maximum amplitude modulation depth= vs,pk / vc,pk

Vs,pk = peak of the sinusoidal reference signal

Vc,pk = peak of the triangular carrier signal

E = bridge dc-link voltage

VO = bridge output voltage

VO,1 = fundamental of VO

IO = bridge output current

DIO= pk-pk ripple current of IO L= bridge output inductance

mf = frequency modulation ratio= fc/f1

fc = freq. of the carrier f1 = freq. of the ref. signal

⎛ I2 + I I + I2 ⎞

Pon = I2device,rms × R on , Idevice,rms = δ ⎜ p p m m ⎟

3

⎝

⎠

fundamental output voltage: VO1 =

switching losses: Ip = Io +

(a) Unipolar pwm switching: 0,±E

Motoring: VO,dc = E a + Ia R a

ma

m

Vdc , VAN,1 = a Vdc

2

2 2

V

output pk-pk current ripple with an L filter: ΔIO = dc

8fc L

Regenerating: VO,dc = E a − Ia R a

Normalized rms voltage harmonics: Vbase = E

DC Choppers

E a = K × Φ f × ω r if the field flux Φ f varies

ma | n=

E a = K1 × ω r if the field flux Φ f is constant

Motor output torque: Te = K1 × Ia

Motor output power: Pe = E a × Ia = Te × ω r

Unipolar PWM: VO,dc

V

= δVDC , ΔIa = DC × δ (1− δ )

fc L a

Bipolar PWM: VO,dc = ( 2δ − 1) VDC , ΔIa =

VDC

× 2δ (1− δ )

fc L a

Discontinuous conduction with unipolar pwm

critical conduction has: ΔIa = 2IO,dc

V

=> ΔIa = δ (1− δ ) dc

fc L a

IfL

condition for always continuous conduction; 2 a c a ≥ 0.25

Vdc

range of ẟ for disc. cond., solve for ẟ in: δ 2 − δ + 2

load current: IO,ac =

Ia fc L a

=0

Vdc

ΔIa

2 3

switch currents:

Irms =

I +I

δ 2

Ip + Ip Im + I2m , Idc = p m , Iac = I2rms − I2dc

3

2

(

)

Assume: Ia = Imotor,dc = IO,dc

ΔI

ΔI

Ip = Ia + a , Im = Ia − a

2

2

(a) motor

PRa = I2motor,rms R a , PEa = Pe = E a × Ia

E a = VO,dc − Ia R a = δVdc − Ia R a , Te =

Pe

, Pin = PRa + PEa

ωr

2

R DSon BJT: PBJT = Iswitch,dc × VCE,on

(a) mosfet: Pmos = Iswitch,rms

ECE Dept. University of Alberta

1

2mf± 1

2mf ± 3 2mf ± 5

0.1

0.07

0.069

0.001

0

0.2

0.142

0.135

0.002

0

0.3

0.212

0.189

0.007

0

0.4

0.283

0.231

0.017

0

0.5

0.354

0.255

0.031

0.001

0.6

0.425

0.262

0.05

0.003

0.7

0.495

0.25

0.073

0.005

0.8

0.566

0.222

0.098

0.009

0.9

0.636

0.18

0.125

0.015

1

0.707

0.128

0.15

0.024

(b) Bipolar pwm switching: ± E

ma

m

Vdc , VAN,1 = a Vdc

2

2 2

Vdc

pk-pk current ripple with an L filter ΔIO =

2fc L

fundamental output voltage: VO1 =

Normalized rms voltage harmonics (Vbase

= E)

ma | n=

1

mf

mf ± 2

mf ± 4

2mf ± 1 2mf ± 3 2mf ± 5

0.1

0.071

0.895

0.002

0

0.07

0.001

0

0.2

0.141

0.878

0.011

0

0.135

0.002

0

0.3

0.212

0.851

0.025

0

0.19

0.008

0

0.4

0.283

0.814

0.043

0

0.231

0.017

0

0.5

0.354

0.767

0.066

0.001

0.255

0.031

0.001

0.6

0.424

0.711

0.093

0.002

0.262

0.05

0.003

0.7

0.496

0.648

0.123

0.003

0.25

0.073

0.005

0.8

0.565

0.579

0.156

0.005

0.222

0.099

0.009

0.9

0.637

0.504

0.19

0.008

0.18

0.125

0.015

1

0.707

0.425

0.224

0.013

0.129

0.15

0.025

Page 11 of 150

Fall 2013

Page 12 of 150

DC DC Converters: Continuous Conduction: IO > IOB

I O ≥ I OB

G dc =

fc =

Vo

δ=

Vi

1

Tc

t ON

Tc

Buck

I base

pu

Boost

VO

2

2fcL

27

I OB

1 − G dc

G dc

δ

δ

G dc

ΔI L

Ip Im

ECE Dept. University of Alberta

4

fcL

Im = IO −

VO

fcL

2fcL

G 3dc

ΔI L

2

ΔI L

2

)

(G

1

+1

dc

1

δ

1−δ

1−δ

1

G dc

1−

o

Ip = IO +

VO

27 G dc − 1

(V − V ) δ

i

(

×

Buck-Boost

G dc

Vi

fcL

Im = Ii −

2

G dc + 1

Vi

δ

Ip = Ii +

)

fcL

ΔI L

2

ΔI L

2

δ

Ip = Ii + IO +

Im = Ii + IO −

ΔI L

2

ΔI L

2

Page 12 of 150

Fall 2013

Page 13 of 150

DC DC Converters: Discontinuous Conduction: IO < IOB

I o < I oB

G dc =

Vo

Tc =

Vi

1

δ=

fc

tz = zero current period in discontinuous conduction

t ON

Tc

t1 = conduction period of the inductor current

t2 = current fall time

δ| =

δ

Δ1

=

δ

1−

tZ

Δ1 =

t1

Tc

=1−

tz

Δ2 =

T

t2

Tc

= Δ1 − δ

Tc

Buck

Boost

I base

VO

2

2fcL

27

Ipu

OB

1 − G dc

G dc

δ

I p = ΔI L

Δ1

Δ2

Ipu

O

ECE Dept. University of Alberta

δ

δ′ =

tz

1−

=

(

4

δ

1

Δ1

1 − δ′

1 − G dc

4

27

G dc

δ

=

Δ

(G

Δ1

Δ2

)

fcL

δ

G dc

2

1

Vi

δ

−δ

δ2

G dc

)

(

fcL

1 − G dc

2fcL

G dc G dc − 1 Ipu

O

o

δ

fcL

1−

(V − V ) δ

G dc

VO

3

=

T

i

VO

27 G dc − 1

Ipu

O

G dc

×

Buck-Boost

27

1 − δ′

=

+1

dc

Δ1 − δ

fcL

δ

G dc − 1

δ

)

Δ1

G dc

G dc

(

δ

G dc + 1

δ

G dc G dc − 1

=

δ

G dc − 1

δ2

2

δ

Vi

G dc

)

G dc Ipu

O

δ

1

4

δ′

1

1

G2dc

δ2

Page 13 of 150

Fall 2013

Page 14 of 150

ECE Dept. University of Alberta

Page 14 of 150

Fall 2013

Page 15 of 150

1-Phase H-Bridge Performance Curves with Square-Wave Switching

Overlap Angle - α

E = dc-link voltage

VO = bridge output voltage VO,n = nth harmonic

α = overlap angle in deg./rad. VO,1 = fund. harmonic of VO

Vo,rms = rms of VO

n = nth harmonic

VO,n =

⎛ α⎞

Vdc cos ⎜ n ⎟ , n = 3, 5, 7, ...

n

⎝ 2⎠

0.9

⎛ α⎞

VO,1 = 0.9Vdc cos ⎜ ⎟

⎝ 2⎠

harmonics of a square-wave voltage magnitude Vo

assume perfect square wave, α = 0° , Vo = Vdc

Vn =

4

π

VO , n = 1, 3, 5, 7, 9, 11, 13, etc..

ΔI O,max =

⎛ V ⎞

Vdc ⎛

8⎞

dc

⎟

⎜ 1 − 2 ⎟ = 0.189 ⎜⎜

2fsL ⎝

π ⎠

2f

⎝ sL ⎟⎠

ECE Dept. University of Alberta

Page 15 of 150

Fall 2013

Page 16 of 150

Chapter 1: Power Semiconductors

1.1 Technical specifications of the main power semiconductor types

ECE Dept. University of Alberta

Page 16 of 150

Fall 2013

Page 17 of 150

1.2 V-I-F ratings of the main power semiconductors (source wikipedia power semiconductor page)

Fig. 1.1 power semiconductor with heatsink and electrical isolation

Fig. 2 Typical V-I-F switching ratings of the main power semiconductors

ECE Dept. University of Alberta

Page 17 of 150

Fall 2013

Page 18 of 150

1.3 SiC and GaN Devices (source IEEE APEC 2013 plenary session)

FOM is a Figure of Merit with consideration of power device conduction and switching losses,

thermal characteristics, and package. FOM is derived based on device theory.

ECE Dept. University of Alberta

Page 18 of 150

Fall 2013

Page 19 of 150

Chapter 2: Power Semiconductor Diodes

Diodes can be used in utility rectifiers to rectify mains ac voltage into dc, Part I of the class notes,

and in a huge variety of switch-mode power converters such as dc-dc converters and dc-ac converters,

see Part II of the class notes. The fundamental characteristics of power semiconductor diodes are

described in this chapter, with characteristics for switch-mode power supplies described in Part II.

The main application for a 1-phase diode rectifier is to provide a dc voltage supply for many electronicbased equipment. The most common 1-phase diode rectifier is the capacitor-smoothed full-wave diode

rectifier. The biggest application for 3-phase diode rectifiers are industrial drive systems. Several LC

filter combinations can be used in both the 1-phase and 3-phase diode rectifiers, primarily to reduce

device rms currents and also to improve the power quality of the rectifiers at its input terminals.

Understanding the operational characteristics of the power semiconductor diode is

necessary for understanding how the different types of diodes are used in different

circuits. Note that this section makes use of the current/voltage and power definitions

described in chapters 8 and 9 for the purpose of estimating the power losses in diodes.

2.1 Diode Model

The diode has an exponential V-I characteristic when conducting in the forward direction and

essentially does not conduct current in the reverse direction, until it reaches the breakdown region: the

latter is often considered a destructive operating region, see Fig. 2.1.

(a) forward bias

To understand the basic operation of the diode, consider the diode as being off unless a voltage

source tries to place a positive voltage drop across its terminals (Anode to Cathode).

(a) Actual Diode Characteristics

(b) Approximate Diode Characteristics

Fig. 2.1 Diode V-I Curve Characteristics

With a forward bias voltage greater than, VDon, the diode will conduct current as it is unable to hold

a forward voltage of more than 0.5 to 2.5 V (= typical values for power semiconductor diodes). The

exponential characteristic in the forward bias region means that the diode can be considered as

approximately having a constant forward conducting voltage of VDon, independent of the magnitude of

the current, see Figs. 2.1 and 2.2, as well as an “ohmic characteristic” r, where the forward bias voltage

can be approximately modeled as increasing linearly with the voltage, see r in Fig. 2.1 and 2.2

ECE Dept. University of Alberta

Page 19 of 150

Fall 2013

Page 20 of 150

Thus the approximate forward biased operating model of a diode may be considered as consisting of

a perfect diode (infinite reverse blocking voltage and a zero forward conducting voltage) with a dc

voltage source VDon (around 0.7 to 1.2 V) together with a series resistance r (around 0.01 to 0.1 ohms),

see Fig. 2.2. This model is sufficient for analyzing utility diode rectifiers and for estimating power

losses in the diode.

(b) Reverse Bias

If a diode is exposed to a reverse bias, or negative voltage, that is

trying to force current to flow through the device in the reverse

direction, then the diode “blocks” the voltage from reaching the

load or output, and no current flows, see Fig. 2.2. In reality a small

“leakage current” IL, Fig. 2.1. This current can be a few mA in a

large diode, but is often regarded as being very small and negligible

when it comes to diode power loss calculations. In diodes with large

voltage and current ratings, this “reverse bias leakage current” can

contribute to power losses, but is more significant when considering

diodes connected in series and determining the reverse bias voltage

dropped across each diode. The reverse bias leakage current is

represented in a simplified model by a perfect diode connected in

series with a large resistance RL, see Fig. 2.2. Lastly, all diodes have

a voltage rating based upon their “reverse bias breakdown voltage”. If a circuit attempts to expose a

diode to a voltage larger than this voltage, a large reverse current will flow through the branch

containing the “perfect diode” in series with a voltage source representing VB. As a result of a large

energy dissipation in the device, this condition is often associated with the destruction of the device.

The breakdown voltage can be modeled using a voltage source VB and a perfect diode, see Fig.2.2.

2.2 Series Connection of Diodes

In high power applications ( > kV ), several diodes can be connected in series to behave functionally

as one diode with a higher reverse bias breakdown voltage than for an individual diode, see Fig. 2.3(a).

However, the reverse bias V-I curves for each diode may be slightly different, see Fig. 2.3(b) (slightly

exaggerated for illustrative purposes). Since the leakage currents of all the diodes must be the same,

then the voltage drop across each diode may differ from the expected: in Fig. 2.3, E/3 might have been

expected but actually vD1 >> vD3.

One solution to this problem is to individually test each diode, and place together diodes with similar

characteristics. This is frequently done in high power applications where the cost of testing each diode

is justified. Another solution is to place a resistor in parallel with each diode. The resistor values

are chosen so that their currents may be 5 five times greater than the reverse bias leakage

currents through the diodes. Since resistors can be manufactured with very small tolerances, then the

voltage drops across each of the reverse bias diodes will be determined largely by the resistor values,

rather than then diode characteristics, and hence forced to be very similar.

ECE Dept. University of Alberta

Page 20 of 150

Fall 2013

(a) 3 diodes in series

Page 21 of 150

(b) reverse bias characteristics

(c) circuit solution for V sharing

Fig. 2.3 Series connection of Diodes

Since resistors are inductive, this voltage balancing technique is not very effective during transient

voltage changes, e.g. when the diodes are turning off and the reverse bias voltage is building up. Note

that the device capacitances can also vary from one device to the next and the dv/dt of each diode may

vary as a result. Hence, separate capacitors are often used, see Fig. 2.3(c), to keep the dv/dt across each

diode similar during this turn off transient. Again the capacitors must be chosen so that their values

are a few orders higher than the natural capacitance of each diode.

Finally, a complete solution would be to have both resistors and capacitors, see Fig. 2.3(c).

2.3 Parallel Connection of Diodes

Diodes may be connected in parallel in order to increase the current rating of one functional diode,

see Fig. 2.4. If three diodes are connected in parallel, the expectation is that the current through each

diode will divide equally: e.g. one third through each diode. This may not happen in reality because the

forward bias V-I characteristics of each diode may be different, see Fig. 2.4 (b). Since the diode

voltage drops are the same, their currents may be unequal e.g. iD1 > iD2. This can cause current crowding

and one diode may heat up higher than the others and fail as a result.

A solution in the steady-state is to place resistors in series with each diode. The resistor values can

be made to be very similar and large enough to guarantee equal current sharing (to within a few

percent), but small enough so as to minimize their power losses.

During device turn-on, currents may rise more rapidly in one diode than the other. The di/dt through

each diode can be made to be similar to guarantee current sharing, if similar inductors are placed in

series with each diode. Since wire-wound resistors are naturally inductive, then the resistance and

inductance can be merged into one component.

Lastly, to avoid saturation effects in the inductors, coupled inductors can be used, see Fig. 2.4(c). If

the currents increase at the same rate in each diode, the flux in the core is zero. If the currents rise

differently in each diode, a flux is created in the inductor core that produces a voltage to counterbalance the unequal di/dt. A low cost toroid transformer can be used for this purpose that is small but

has a large inductance for controlling the di/dt.

ECE Dept. University of Alberta

Page 21 of 150

Fall 2013

Page 22 of 150

(a) parallel

(b) forward bias characteristics

(c) circuit solutions for I sharing

Fig. 2.4 Parallel connection of Diodes

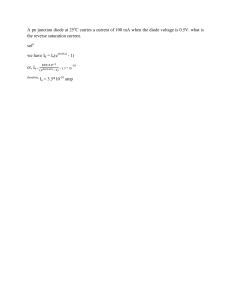

2.4 Examples

Example 1: A current pulse flows through a diode with a 50% duty cycle of magnitude Id.

Determine the average & rms of the current pulse. The diode has a forward conducting resistance

of 0.02 Ω & a junction voltage of 0.7 V. Determine the power loss in the diode if Id = 10A.

ECE Dept. University of Alberta

Page 22 of 150

Fall 2013

Page 23 of 150

Example 2: A repetitive pulsed current of 8 A magnitude and 60% duty cycle is passed through

two diodes connected in parallel. A series resistor of value 0.1 Ω is placed in series with each diode

to help the current share more equally between the two components. If the on-state junction

voltage of one diode is 0.7 V & the other is 0.8 V, determine: the total rms, dc & ac components of

the currents flowing through each diode, the power dissipated in each of the 4 components.

ECE Dept. University of Alberta

Page 23 of 150

Fall 2013

Page 24 of 150

Chapter 3: Thyristor

The Silicon Controlled Rectifier (SCR), or also referred to as the thyristor, is the oldest known

power semiconductor switch. For many decades, it was the only power semiconductor that could handle

large voltages and currents, ( > 1,000V, > 1,000 amps). Its multi-junction structure, see Fig. 3.1, and

vertical flow of current, allow the device to handle large current ratings together with a large forward

and reverse voltage blocking capabilities. Note: mosfets can have the current flowing parallel with the

surface and hence have low current and voltage ratings.The main applications for thyristors range from

low cost electronics, e.g. light dimmers, up to very high power 3-phase rectifiers and cycloconverters.

This section summarizes the main characteristics of the thyristor and associated control circuitry.

3.1 Power Semiconductor Structure

A cross section of the thyristor semiconductor is shown in Fig. 3.1 in simplified form, and then in

more detailed for an actual device structure. Essentially the device consists of four layers of

semiconductor doped material: P-N-P-N sequence of doping. The device behaves like a controlled diode

with current flowing into the anode terminal, A, and flowing out the cathode terminal C. The on-off

state of this diode can be controlled by applying a low power short duration pulse to the gate terminal

G. The circuitry supplying this pulse is referred to as the gate-drive and passes current into the device

gate terminal G and returning via the cathode terminal C. A thyristor normally has large leads for

connecting to the A and C terminals to conduct large currents, and separate small leads for passing low

current gate signals to the G and C terminals. The differences in lead size between these two

connection types can be very striking: the device main terminals are designed to conduct hundreds if

not thousands of amps, and the small gate terminals are designed to conduct milli-amps!

(a) simplified

(b) more detailed

Fig. 3.1 SCR Power Semiconductor X-section

Starting from the anode terminals, the first sequence of doped silicon: P2-N2-P1 behaves like a PNP

BJT transistor, the sequence of doped layers N2-P1-N1 connected to the cathode terminal behaves like

a NPN BJT transistor. This simplified way of looking at the thyristor produces a device based circuit

model with transistors as shown in Fig. 3.2(a), with the associated thyristor symbol in Fig. 3.2(b).

ECE Dept. University of Alberta

Page 24 of 150

Fall 2013

Page 25 of 150

3.2 Power Semiconductor Switching Characteristics

The two transistor model for the thyristor can be used to explain fundamental characteristicd of

the device, namely:

(a) A small short duration pulse is all that is required to turn

on the thyristor, after which the thyristor remains in the

on-state until the current flow through the device is

reduced to zero by external factors.

(b) Once in the on-state the thyristor behaves identical to

a diode, i.e. the device conducts current in the forward

direction, and blocks voltage/current in the reverse

direction.

(c) It is not required to have a continuous gate current to

keep the device on.

(d)A thyristor cannot be turned off at the gate by

discontinuing the gate current or by impinging a reverse or

(a) model using BJTs

(b) symbol negative gate current.

Fig. 3.2 SCR Symbol and circuit model

off-state: When forward biased, A is more positive than C. The base-emitter junctions of the two

transistors can not provide a voltage blocking capability. However, from the two transistor equivalent

circuit, the junction that can block, or hold voltage in the forward direction, is the C-B junction of

transistor T1. When a reverse biased voltage is dropped across the thyristor, C is more positive than A

and the collector base junction of T2 can hold the voltage to provide reverse bias. voltage blocking

turn-on process: When a gate current iG is applied, see Fig. 3.2(a), a base current iB1 is applied to the

transistor T1. This means that the gate current flows in the terminal G and out the terminal C. T1 is

hence turned on and its C-B junction voltage drops and the C-E voltage of T1 drops. With T1 turning on,

base current iB2 is drawn from T2 into C1, hence iC1. iB2 flows from the emitter of T2 as long as there is a

load current providing current into the terminal A of the device. With T2 turning on, collector current

iC2 flows into the base of T1, thus providing iB1.Thus with T2 on, T2 provides the base current for T1, and

T1 provides the base current for T2. Hence with both transistors turned on due to the presence of a

load current and current is flowing from terminals A to C, there is no need for a gate current iG to

provide the base current iB1 for T1. Typically the duration of the gate current can be a pulse of duration

10 to 200 mS and then it can be discontinued. The action of T1 AND T2 PROVIDING EACH OTHERS

BASE CURRENT, IS A POSITIVE FEEDBACK MECHANISM, and ONCE THE DEVICE IS ON,

IT STAYS ON!

turn-off process: Once on, the device behaves as a diode. i.e. the current will continue to flow

through the diode until external factors reduce the device current to zero and it turns it off.

3.3 Power Semiconductor V-I Characteristics

When forward biased, unlike the diode, the device will hold voltage and no current will flow. In fact

a small “forward leakage current” will flow similar to the reverse bias leakage current of a diode, see

Fig. 3.3. If the voltage is increased sufficiently enough, then this leakage current, which will flow into

ECE Dept. University of Alberta

Page 25 of 150

Fall 2013

Page 26 of 150

the base of T1, and may be sufficient to turn the device on. This is not the normal turn-on process and

could be harmful for the device.

A specially designed thyristor, know as the SIDAC, uses this forward bias leakage current to turn

the device on at some specific voltage threshold level. This device is used quite often in the gate driver

circuitry of thyristors used in provide pulse power supplies such as gaseous discharge lamps like the

metal halide HID lamp and high pressure sodium lamps.

However, a standard thyristor will not normally be placed in circuits where the voltage reaches a

high enough level in the forward direction such as to turn on the device: the forward breakdown voltage

level. For reliability purposes, the maximum forward bias voltage experienced by a thyristor in a circuit

would normally be around 50% relative to the device voltage rating or breakdown voltage.

The normal turn-on process has the device forward biased with a gate current, so the device goes

from an the off-state with a high forward bias voltage, curve 1 in Fig. 3.3, to an on-state with a low onstate voltage drop and a high forward conducting current, curve 2. The forward biased voltage scales

are exaggerated Fig. 3.3 so that the device on-state voltage can be observed.

Fig. 3.3 SCR V-I Operational Curves

Applying a gate current with the device forward biased is not the only condition required for the

device to turn-on. The device anode to cathode current must also increase above a threshold level for

the device to actually turn on and stay on after the gate pulse had been removed. This device current

level is referred to as the latching current. IL, This current level for a device is normally fairly small

when compared with the device rated current: a device might have a latching current level of say 20mA

but a rated current of say 200 A..

After the gate pulse is removed, once the device is on it stays on until the device current drops

below a threshold level known as the holding current, IH: IH < IL.

In the reverse bias condition, see Fig. 3.3, the device will hold a negative voltage VAC = -ve, and only a

small current will flow, similar to a diode characteristic, known as the reverse leakage current. This

current is a function of voltage, but the maximum expected current is normally used in calculations

ECE Dept. University of Alberta

Page 26 of 150

Fall 2013

Page 27 of 150

involving power dissipation and the design of external circuits. The device will start conducting a large

reverse current when it is exposed to a voltage that exceeds its reverse breakdown voltage limit. This

operating condition is normally destructive and is not allowed to occur in normal circumstances.

Normally, device ratings are chosen so that the device voltage is 50% relative to its reverse breakdown

level.

3.4 Gate-Drives

The circuitry that delivers the pulses to the thyristor to turn it on is referred to as the gatedrive. This circuit is required to deliver a pulsed current of the required size and duration so as to turn

on the device when required under all the expected operating conditions for the thyristor. The 0V or

gate drive GND terminal is connected to the thyristor cathode terminal. A three-phase thyristor

rectifier is shown in Fig. 3.4, and it should be noted that the thyristors connected to the dc output

positive terminals have their cathodes all connected together, whilst the cathodes of the thyristors

connected to the rectifier negative output terminals are connected to different phase voltages. This

means that their cathodes are at a different potential relative to one another and also at a different

potential relative to the cathodes of the +ve group of thyristors

Fig. 3.4 Gating Circuitry for a 3-phase SCR Rectifier

This is an important observation to make regarding thyristor gate-drive circuits in the same power

circuit: the gate drive GND terminals cannot be assumed to be at the same potential as each

other and also are not at the same potential as the controller GND. This means that thyristor gate

drives have to provide electrical isolation, and the pulses provide to the thyristor gate inputs are often

delivered using isolating pulse transformers, see Fig. 3.4. However, the input signals to each of the

pulsed transformer circuitry can be supplied from the same controller and GND potential. The output

of the pulsed transformers may also use circuitry for waveshaping the pulses as required.

ECE Dept. University of Alberta

Page 27 of 150

Fall 2013

Page 28 of 150

A sample range of gate drive circuits are shown in Fig. 3.5. Gate drive (a) uses a photo-sensitive high

voltage signal thyristor to deliver pulsed currents to the gate of the thyristor whose magnitude is

controlled via the resistor RG. The voltage for the gate driver output circuitry can often be the forward

conducting voltage across the main the thyristor itself and the photo-thyristor is turned on via a photodiode. Sometimes these light signals are delivered to the thyristor gate drive via fibre optic cables

using a transmitter and receiver circuit. This is done in order to locate the power electronics remotely

from the controller itself inside am industrial drive cabinet. This is done, because the power electronics

uses switching circuitry that can be a source of emi and rfi emissions, that in turn can interfere with

the sensitive digital controllers. So it is quite often desirable to locate power electronic equipment in

cabinets with emi/rfi shielding remote from the main controller.

Fig. 3.5 Sample of SCR Gate Drive Types

Gate drive circuit (b) is an example of using a pulse transformer who’s circuitry directly feeds the

gate of the thyristor. The transformer primary is supplied from a buffer transistor that receives a

pulse base current from an RC network. The diode connected across the transformer primary is

designed to take the transformer magnetizing current when the transistor is turned off. Quite often a

resistor is placed in series with this diode to allow the transformer magnetizing current to decay

rapidly after the pulse is removed and the transistor is turned off.

Gate drive circuit (c) is an example of a pulse transformer gate drive where a digital controller is

used to control the frequency and duration of the pulses to the thyristor, and extensive pulse

waveshaping circuitry is used at the thyristor input terminals.

ECE Dept. University of Alberta

Page 28 of 150

Fall 2013

Page 29 of 150

3.5 Examples

Example 1: Differentiate between the latching current and the holding current of a thyristor.

What maximum value of R must not be exceeded in the circuit below in order to ensure an R/L load

current when a 50 µS trigger pulse is employed. The SCR has a latching current of 50 mA and a

holding current of 10 mA. The freewheel diode Dm, has a reverse leakage current of 1mA at 100V

reverse bias, Sketch the waveforms.

ECE Dept. University of Alberta

Page 29 of 150

Fall 2013

Page 30 of 150

Chapter 4: BJT & MOSFET

The fundamental characteristics and electrical ratings of the power semiconductor transistors

determine many aspects regarding the nature of a switchmode power supply. For instance, a device

switching frequency is limited by its switching speed, e.g. 10nS for mosfets (metal oxide semiconductor

field effect transistor), 100nS for igbt (insulated gate bipolar transistor), 1.5 µS for bjt (bipolar

junction transistor), 20 mS for a gto (gate turn off thyristor). In turn, the device switching frequency

determines the size of the LC filtering requirements. Obviously the higher the switching frequency, the

smaller the size of the filter.

Several important transistor characteristics are as follows:

(a) switching speeds and switching frequency

(b) on-state voltage drop

(c) current and voltage ratings

(d) gate drive requirements: high power vs low power, current vs voltage signal, isolation.

The voltage/current ratings and gate drive design for a transistor should be considered in

conjunction with its switching speed. For instance, the fastest device, hence most desirable, is the

mosfet. Its gate drive is also very low power and only requires a voltage signal around 5 to 15V

depending upon the device. These characteristics are far superior for the mosfet as compared with any

other device, so the mosfet is generally the preferred device. However, the mosfet voltage and current

ratings maximize at around 500V and 100A (with recent increases up to 1,000 V). With higher voltage

ratings the device’s on-state resistance rise exponentially and hence it currents ratings fall

dramatically. Generally, the bjt has higher voltage and current ratings suitable for high power

applications, but its high base current makes the device have a high power gate drive circuit and it has a

much lower switching speed. So in high power, hence high voltage applications, the bjt is the preferred

device, but in low power the mosfet superior electrical characteristics make it the preferred device.

This section describes the nature of two power semiconductors: bjt and the mosfet. The igbt is a

very special device in high power industrial applications and can be considered as being a hybrid of the

mosfet with the bjt devices. This device should be treated separately and is described in another

section. This section summarizes the electrical characteristics of the mosfet and bjt from a user

perspective, and is not intended as a detailed description on the details of semiconductor physics.

4.1 BJT Transistor

This device has specialized applications and its characteristics and operation are useful for

comparison with other devices.

(a) device

A simplified vertical X-section of a power semiconductor bjt is shown in Fig. 4.1(a) together with its

circuit symbol in Fig. 4.1(b)(i). The device main feature is that its emitter terminal is at the top of the

silicon slice and the collector terminal is at the bottom. This means that the main current flow direction

is in the vertical direction. Many microelectronic devices are very low power and the current flows from

one contact at the top to another contact at the top, i.e. the main current flow is horizontal. Many

power semiconductors have gone through many design changes and improvements to maximize the main

ECE Dept. University of Alberta

Page 30 of 150

Fall 2013

Page 31 of 150

current flow in the vertical direction rather than the horizontal to maximize the current density and to

increase the current ratings of the device. The current density of a silicon transistor is lowered if the

main current flows horizontally at the top surface.

Fig. 4.1(c) shows that typical bjt emitter metallization contacts can consists of a mesh or lattice of

fingers covering the top surface of the silicon. This increases the current rating of the device.

Although the base is the input to the device, its connections are not small. This leads us to the second

major point regarding the bjt device. The device is current driven with the base current being the

controlling signal for turning the device on and off. Due to the fact that the base width has to be large

to give the device a high voltage rating, e.g. 1400V. A large base width also results in a low current gain

β. A low β means that the bjt has a large base current (amps) and its gate drive is large.

(d) npn darlington transistor X-section

(e) npn transistor V- Characteristics

Fig. 4.1 BJT power semiconductor

ECE Dept. University of Alberta

Page 31 of 150

Fall 2013

Page 32 of 150

A bjt can have a β as low as 5!. Thus a 100A β requires a base current of at least 20A!. Thus the

base connections for a transistor are required to be large.

High voltage bjts, = 1400V, require large base widths, so devices were invented to lower the input

current. Fig. 4.1 (b)(ii) and 4.1(d) show the darlington device where a second transistor, is used to

supply the base current of the main transistor. If the main transistor has a β of 5, and the second 20,

then the overall current gain is 100, so a 100A transistor needs a minimum base current of 1 A. This is

an improvement but is still considered large by Today’s standards. Consider that the device input

electrical characteristics consists of two series connected base-emitter junctions of 0.7 V, and a 1A

input current. This produces a base drive power requirement of 1.7 W. This current of 1A has to be

supplied from a dc voltage supply of 10 to 15 V, so the actual power required is closer to 12W. A three

transistor device was invented, the triple darlington, to lower the input current even further.

bjt base drives are noted for being large in size with large power requirements. The resultant

device driver circuits can be compared to mosfet and igbts where the inputs to the device can be

obtained using a 100 Ω resistor connected directly to a low power logic chip!

(b) V-I characteristics

The V-I operating characteristics of the bjt have many features, see Fig. 4.1(c). Note that power

semiconductors are operated in switchmode: when they are off their current is close to zero, when

they are on, their voltage is close to zero. These observations refer to the power terminals which are

the device collector and emitter terminals.

(i) hard saturation: This operating condition, see Fig. 4.1(e) is associated with a low on-state voltage

drop, hence low conduction losses, and is achieved by supplying a base current much larger than that

given by β and IC. A VCE as low as 0.2 V can be achieved even in very high power devices. In many

applications such as electronic ballasts, this cannot be beaten even by mosfets. So in some applications

the low cost, high efficiency of a bjt switchmode circuit can be the most feasible. Hard saturation is

associated with a large charge concentration in the devices base region, see Fig. 4.2 (b). This charge has

to be removed before the device can turn off, so the turn-off times of a b operated in hard saturation

can be very slow, tens of mS. This is undesirable since it means a low switching frequency, high turn-off

losses, higher power base drive, and poor short circuit protection.

(ii) quasi-saturation: In some applications, e.g. industrial drive systems, circuitry can be used to

increase the device on-state voltage drop and so put it in the quasi-saturation mode, see Figs. 4.1(e) and

4.2(b). This increases the on-state losses, but is also lowers the charge stored in the bjt device during

its on-time. Hence the devices turn-off time can be reduced drastically, e.g. 1-2 mS, and the device

switching frequency increased. The short-circuit protection of the device is also improved due to faster

turn-off times.

(iii) primary breakdown: This is caused by the avalanche breakdown of the collector base junction, see

Fig. 4.1 (e), due to excessive device current and voltage. Operation in this region is considered

destructive.

(iv) secondary breakdown: See Fig. 4.1 (e) and Fig. 4.2(c). This is caused by excessive current

concentration in specific regions of the device producing localized hot spots and is different to the

primary breakdown.

ECE Dept. University of Alberta

Page 32 of 150

Fall 2013

Page 33 of 150

Fig. 4.2 BJT power semiconductor characteristic

ECE Dept. University of Alberta

Page 33 of 150

Fall 2013

Page 34 of 150

4.2 MOSFET Power Semiconductor

The mosfet is the main device used in all low power and low voltage switchmode power supply

applications. This is primarily because of its very high switching speeds, and associated, high switching

frequencies, as well as its very low power gate drive requirements. Of course, the device itself is

relatively inexpensive to manufacture!

(a) device

The main characteristic of the mosfet are its input control terminals being consider as being

largely capacitive, see Figs. 4.3(a) and 4.3(b). The input terminals (gate-source) are separated by a

silicon oxide layer which provides electrical insulation and makes the terminals look capacitive. This

capacitance is small and can be charged and discharged rapidly to turn the device on and off. Unlike the

bjt, there is no need for a large continuous input gate current to keep the device on: the device gate

current is of the order of pA! The device is therefore said to be voltage activated, and unlike the

thyristor, can be turned on and off at the gate.

The main current flow is from drain to source, iDS, and flows in the vertical direction through the

silicon wafer as shown in Figs. 4.3(e), (f). A vertical current flow has the effect of increasing the

current density of the device as there is no need for large currents to flow into and back out of the

upper surface. However, the device works by forward biasing the device input terminals, VGS, which

induces a charge concentration in the channel region immediately beneath the gate, see Fig. 4.3(c). This

channel is essentially a surface phenomenon, placing limits on the current capability of the device.

To increase the device current ratings, a fairly complex web of metallization and gate-source

connections are used, see Fig. 4.3(d). International Rectifier has an historically famous device known as

the HEXFET, see Fig. 4.3(e), whose name comes from the hexagonal shape of its gate connections. This

device structure was to used maximize the combination of gate regions, hence channel regions, as well

as the source regions which carry the main current. For instance, there is no point having a large

percentage of the surface designated for the source regions and main current flow, if the channel

regions are compromised resulting in a large drain to source resistance.

The larger the gate voltage, the larger the concentration of charge in the channel regions and the

lower is the drain to source resistance, see Figs. 4.3(c), 4.3(f) and 4.3(g). Typical gate-to-source

voltages for low conduction losses can lie between 10 to 15 V. Fig. 4.4(b) identifies regions in the silicon

X-section that contribute to the device on-state resistance. A mosfet on-state characteristic can be

described as being resistive. Fig. 4.4(c) shows how the device resistance increases with the junction

temperature, the device is described as having a positive temperature coefficient of resistivity.

(b) on-state characteristic is resistive

The device on-state resistive characteristic allows the device to be connected in parallel with other

devices in order to get a total switch with a higher current rating. This is done on a regular basis inside

a semiconductor package: several mosfet cells and silicon die are connected in parallel inside the

package. The positive temp coefficient of resistivity also means that if current tends to crowd into one

of the devices, its temperature will increase and thus its resistance will increase so the current

eventually reduces. This shift in temprerature tends to offset the unbalance in currents between

parallel connected devices. In addition, the positive temperature coefficient of resistivity means that a

device conducting more current than expected, will increase in temperature as a result of the higher

ECE Dept. University of Alberta

Page 34 of 150

Fall 2013

Page 35 of 150

current and power losses. This temperature increase will increase the devices resistance, and so offset

the current unbalance.

Fig. 4.3

(c) device V-I characteristic.

The device is resistive when on. This can be seen in Fig. 4.3(g) when VDS is low. At high VDS, the ID vs

VDS characteristics are flat. Unlike the bjt, the device does not have a primary and secondary

breakdown characteristic, but has a square V-I operating range. This is more useful for maximizing the

voltage ratings of the device: in switchmode power supplies, the device can be exposed to the maximum

ECE Dept. University of Alberta

Page 35 of 150

Fall 2013

Page 36 of 150

voltage and current at the same time. The fbsoa characteristic shown in Fig. 4.4(d) shows the maximum

V and I values that can be withstood at the same time for a fixed duration. During normal pwm

switching, the device is exposed to the maximum V-I only for very short periods of time (nS), see Fig.

4.5, so the device can operate safely. The bjt secondary breakdown characteristics do not allow

maximum V and I to be withstood at the same time, so the bjt has more restrictions on its voltage

ratings. i.e. if the device is rated at 1400V, then it should only be considered in applications only up to

700 V, unless specialized snubber circuitry are used. A mosfet rated at 450 V, could be used in

applications with say 350 V. However, the mosfet has the characteristic that is turns off exceptionally

fast. Stray lead inductance can cause the device voltage to overshoot the supply dc rail voltage by a

larger amount than a similar bjt switching at lower speeds, see Fig. 4.5. This means that the design of a

mosfet switchmode circuit has to pay more attention on the lead lengths and the determination of lead

inductance. Even the leads within the mosfet package can result in a significant device voltage

overshoot that cannot be seen at the device output terminals!

During fault conditions, the fbsoa curves illustrate how long the device can survive for, and so are

useful when designing the over-current fault protection circuitry

Fig. 4.4 MOSFET power semiconductor characteristics

ECE Dept. University of Alberta

Page 36 of 150

Fall 2013

Page 37 of 150

Fig. 4.5 Typical device V-I trajectories during switching

4.3 Summary

(a) BJT

1 Can be turned on and off at its input base terminal and is essentially current controlled.

2 High voltage bjts have low β values, so the device driver circuitry is high power/expensive. The

device driver circuitry requires relatively large floating power supplies as a result.

3 Voltage ratings maximize at around 1400V and current ratings maximize at 200-400 A

4 Limited to some specialized applications where its very low on-state voltage is useful.

5 Medium switching speeds typically in the range 1 to 3 mS, with switching frequencies commonly in

the range 1 to 10 kHz, and in lower power up to around 30 kHz.

ECE Dept. University of Alberta

Page 37 of 150

Fall 2013

Page 38 of 150

(b) MOSFET

1

2

3

4

5

Can be turned on and off at its input gate terminal and is essentially voltage controlled, with its input

terminals characterized as being capacitive.

The device driver circuitry is very low power. Surface mount control ICs can be used as the gate

drivers have very low power ratings.

Voltage ratings maximize at around 450 V and current ratings maximize at a 100-200 A, but more

commonly used in the 1 to 50 A range.

A wide range of applications in low voltage and power switchmode power supplies, where the device’s

very high switching frequencies, and resulting small compact LC filters, cannot be beaten.

Very low switching speeds typically in the range 10 to 50 nS, with very high switching frequencies

typically in the range 20 kHz to 1MHz.

ECE Dept. University of Alberta

Page 38 of 150

Fall 2013

Page 39 of 150

Chapter 5: MOSFET & BJT Input Drivers & Snubbers

The bjt transistor is a current driven device and has a limited current gain β. The mosfet transistor

is a voltage driven device with a capacitive input control terminal and an on-state voltage VGS, typically

being in the region of 5 to 15 V. The bjt has a constant on-state voltage drop which can be as low as its

saturation voltage, VCEsat (0.2 V). The mosfet has a resistive on-state voltage drop that is a function of

its VGS and also temperature, and can be of the order of mΩ. This section describes some circuitry

that can be used for both devices to improve their operation and switching characteristics. Some of

the circuitry described for the bjt are also linked to their use for both mosfet and igbt devices.

A generic name for the driver circuitry of a power semiconductor device is a ”gate drive”. This

can be also be used for the bjt, though the more correct name for the bjt would be “base drive’.

5.1 BJT

The current gain of the bjt, β, can be as low as » 5-10 because of a large base width, which has to be

relatively large in order to increase the device’s voltage ratings. But a low β also means that the

transistor has a relatively large input control current (=base current). Classically, IC = β IB, but the base

current has to be made even larger than that given by this equation in order to force the device onstate voltage drop down: putting the device into saturation when it is on. This is done to lower the

devices conduction losses. This results in a large base current and a high power gate drive circuit.

(a) Darlington transistors

The darlington transistor, see Fig. 5.1(a) is used so that a secondary transistor T2 supplies the base

current of the primary transistor, and the driver circuitry for the complete switch only has to supply

the base current of T2. The resultant VCE1 can be given by VCE1 = VBE1+VCE2,sat . If VBE = 0.8V, VCEsat = 0.2

V, then the primary transistor VCE1 = 1V. This places this transistor out of saturation and into the quasisaturation region. This has the effect of increasing the on-state conduction losses, but also improves,

i.e. lowers, the turn-off switching time. This results in a higher device switching frequency.

(a) darlington

(b) triple darlington

(c) RD for switching

Fig. 5.1 bjt power semiconductor

The darlington is a device that can be manufactured on a single piece of silicon as can the triple

darlington, see Fig. 5.1(b). The latter device was produced in order to reduce the switch input control

ECE Dept. University of Alberta

Page 39 of 150

Fall 2013

Page 40 of 150

current even further, IB3 in this case. Both switch arrangements would not be implemented as shown

because of problems associated with slow switching speeds and the likely hood that all the devices will

turn-off at the same time. For instance, if T1 turns off first, the switch is in the quasi-saturation mode,

then the load current, I2, would flow into T2 and may even flow into the driver circuitry and destroy it.

Diodes and resistors are often placed across the base emitter junctions of the transistors as shown

in Fig. 5.1(c). When the transistors are on and their base-emitter junctions are forward biased, the

diodes and resistors have no effect. When the transistors are turned off, the driver circuitry would

normally draw a large negative pulse out of the base terminal of T2. This has the effect of drawing a

large negative current through the base-emitter junctions of the two transistors. This draws out base

region stored charge and reduces the storage time and device turn-off time. However, the junctions