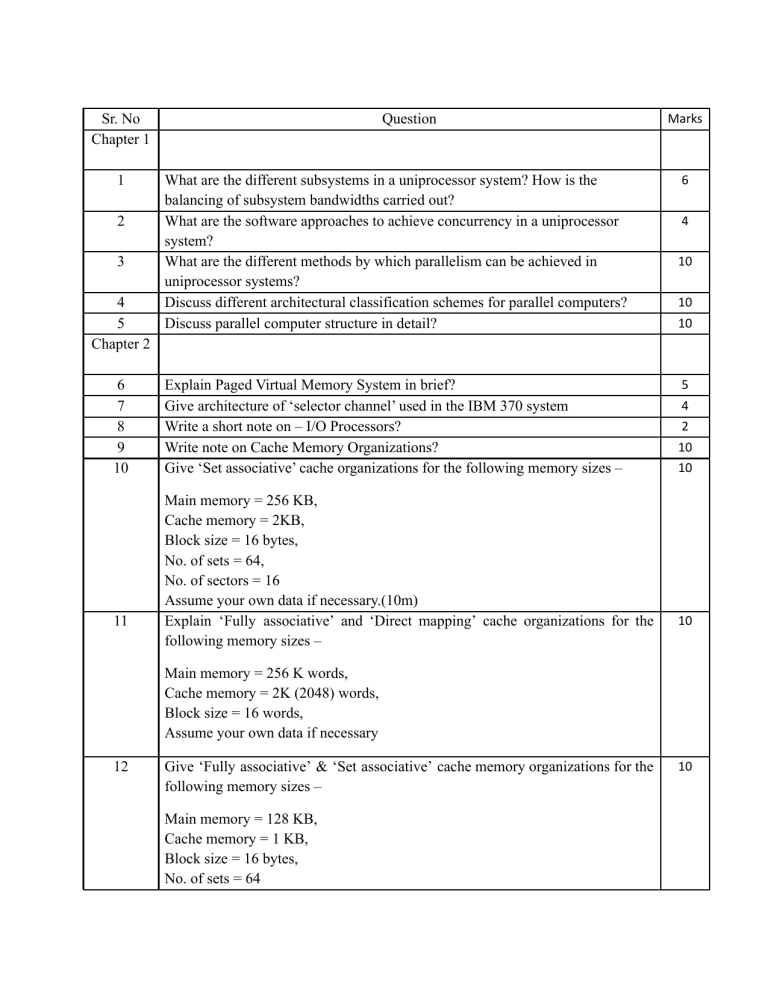

Sr. No Chapter 1 1 2 3 4 5 Chapter 2 6 7 8 9 10 11 Question What are the different subsystems in a uniprocessor system? How is the balancing of subsystem bandwidths carried out? What are the software approaches to achieve concurrency in a uniprocessor system? What are the different methods by which parallelism can be achieved in uniprocessor systems? Discuss different architectural classification schemes for parallel computers? Discuss parallel computer structure in detail? Explain Paged Virtual Memory System in brief? Give architecture of ‘selector channel’ used in the IBM 370 system Write a short note on – I/O Processors? Write note on Cache Memory Organizations? Give ‘Set associative’ cache organizations for the following memory sizes – Main memory = 256 KB, Cache memory = 2KB, Block size = 16 bytes, No. of sets = 64, No. of sectors = 16 Assume your own data if necessary.(10m) Explain ‘Fully associative’ and ‘Direct mapping’ cache organizations for the following memory sizes – Marks 6 4 10 10 10 5 4 2 10 10 10 Main memory = 256 K words, Cache memory = 2K (2048) words, Block size = 16 words, Assume your own data if necessary 12 Give ‘Fully associative’ & ‘Set associative’ cache memory organizations for the following memory sizes – Main memory = 128 KB, Cache memory = 1 KB, Block size = 16 bytes, No. of sets = 64 10 Assume your own data if necessary. 13 Explain how ‘segmented virtual memory system for multi-process environment’ is implemented? 10 14 Explain how overlapped instruction execution is carried out in a pipelined processor ? How much is the speed up achieved ? 5 15 Give different pipeline classification schemes as proposed by Ramamoorthy & Li? 6 16 Given DIMENSION X(8) , Y(10,4) What is represented by -X(2:8:2), Y(3:5, 3), Y(*, 3) & Y(5, 2:*) 4 17 18 4 19 Give ‘Pipelined CPU structure’ of a modem digital computer? Give the classification of pipeline processors according to the levels of processing? Define & give the expressions for 20 1. clock period 2. speed up 3. efficiency 4. throughput of a linear pipeline processor – Discuss the following design problems of pipeline processors – Chapter 3 3 4 12 1. Branch Handling 2. Internal forwarding & Register Tagging 3. Hazard detection & resolution 21 Prove that a k – stage linear pipeline can be at most k times faster than that of a non-pipelined linear processor 3 22 Describe the following terminologies associated with the pipeline computers – 4 1. Dynamic pipeline 2. Multifunctional pipeline 3. Instruction Pipeline Vectorizing compiler 23 Explain different ‘Pipelined Vector Processing Methods’ giving example. 10 24 Give 2-Dimensional Array pipeline for carrying out Matrix Multiplication C = A * B, where A, B & C are 3* 3 matrices? 5 25 Discuss different ‘principles of designing pipeline processors’? 10 26 Discuss the job sequencing problem in the design of a pipeline processor by giving suitable example. How is it resolved? Also explain the following terms – latency, control strategy, collision vector, greedy cycle, minimum average latency 10 27 What are pipeline hazards? Why are they caused? How can they be detected and resolved? 10 28 Discuss key design problems of pipeline processors? 20 29 Give T1 cache ASC arithmetic pipeline and give four functional configurations in the TI-ASC arithmetic pipeline? 30 Design a pipeline to multiply two 6-bit number for pipeline multiplication using CSA (Carry Save adder) tree/Wallace tree? 31 Design array pipeline for pipelined multiplication of two 3x3 dense matrices A and B giving elements of the matrix C using M cell where M cell has 3 input operands a, b, c and 3 outputs a’=a, b’=b and d=axb+c? 32 Design a pipelined floating point adder with four processing stages? 33 Following is the Reservation Table for a unifunction pipeline. Give 1) Forbidden list F 2) Collision Vector C 3) Draw state Diagram 4) Give Minimum Average Latency MAL 5) Simple cycles 6) Greedy cycles Chapter 4 34 What are the ‘Nine Common practices used in optimizing the vector Functions? Explain giving examples. 35 Given REAL X(10,10) ; what is represented by - 36 VECTOR X ROW 2(1:10) , VECTOR X DIAG(1:10) , VECTOR X COL 5(1:10:3) Convert the following ‘DO-loop’ statement to a single vector statement – 9 3 1 DO 20 I = 8,120,2 20 A(I) = B(I+3) + C(I+1) 37 Write a detailed note on Interconnection Networks for SIMD array processors. 10 38 Write a short note on ‘Vectorizing Compiler’? 4 39 Explain giving examples the common practices in optimizing the vector functions? 10 40 Explain giving examples the common practices in optimizing the vector functions. Also give the lists of optimizing functions that are used for 1)General optimization 2)Extended Optimization 3)Vector extended optimization 10 41 Draw an Illiac network with N = 16 PEs 2 42 explain masking and data routing mechanisms of an SIMD computer 5 Chapter 5 43 Give the architectural classification of SIMD computers systems? 2 44 Discuss the architectural organizations of SIMD array processor in brief? 8 45 Give different configurations of SIMD array processor? 6 46 Give structure of a basic Associative Memory? 6 47 Write a detailed note on Mesh-Connected Illiac Network 8 48 Write a detailed note on Cube Interconnection Networks? 8 49 Give algorithm for SISD matrix multiplication. Modify it for implementing on SIMD machine. How much is the speed gained? Explain 8 50 Write a detailed note on ‘Shuffle-Exchange’ and ‘Omega’ Networks for SIMD array processors? 10 51 Write a note on Associative Memory Organization 52 Write a short note on Associative Search Algorithm Chapter 6 53 Give different ‘performance enhancement methods’ for SIMD Array Processors. 10 54 Draw 42 * 32 delta network? 2 55 Discuss different ‘Bus Arbitration algorithms’ used in multiprocessors with time shared bus? 10 56 What are the different parallel language features used for programming in a multiprocessor system? 10 57 Discuss the following multiprocessor hardware organizations – 10 Chapter 7 Multiprocessor with time shared bus Multiprocessor with crossbar switch & Multiprocessor with multiport memory 58 Compare the following multiprocessor hardware organizations – 5 Multiprocessor with time shared bus Multiprocessor with crossbar switch & Multiprocessor with multiport memory 59 Discuss ‘Multiport Memory Organization’ for multiprocessors? 60 Discuss ‘Master Slave Operating System Configuration’ multiprocessor computer? 61 Discuss architecture of ‘Loosely Coupled Multi processor System’ in detail? 10 62 Discuss architecture of ‘Tightly Coupled Multi processor System’ in detail? 10 63 Write a detailed note ‘Multi stage networks for multiprocessors’? 10 64 Write a note on “Multiprocessor Scheduling Strategies” 10 65 Give classification of multiprocessor operating systems. Discuss advantages & disadvantages of each in brief? 10 66 What are the techniques for designing parallel memories for multiprocessors 10 67 Give Design of an x bn Delta network for multiprocessors 68 Give 23 x 23 delta network. 69 Give different language feature to exploit parallelism in MIMD multiprocessor system 70 Give functional structure of a cross point in a crossbar network 4 used for a 3 Chapter 8 71 Write a short note on ‘critical Sections’? 6 72 Explain how Process Synchronization is carried out using mutual exclusion in multi-processor system? 10 73 Explain how Process Synchronization is carried out using Conditional Critical Sections & Monitors in multi-processor systems? 10 74 Discuss the system deadlock problems in multiprocessors. Also discuss various protection mechanisms that can be used in a multiple process environment to ensure only authorized access to resources? 10 75 Discuss the system deadlock problems in multiprocessors. Also discuss deadlock detection and recovery mechanisms that are used in a multiple process environment? 10 Explain how data flow computing differs from control flow computing taking example of the execution for the computation a = (b+1)*(b-c) in a control flow computer using shared data memory and in a data flow computer 10 77 Discuss static Data Flow Computer Organization? 5 78 Discuss in brief different “Data Flow Machine Architectures”? 10 79 Write a detailed note on ‘Data Flow Graphs’. Also give dataflow graph representation of the computation z= xn 10 Chapter 10 76