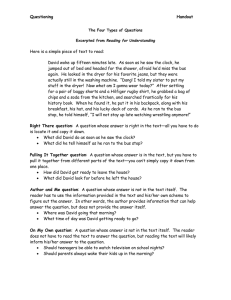

Get Connected: SerDes demystified Michael Peffers May 8, 2014 Welcome back to the Get Connected blog series here on the Analog Wire! In the previous Get Connected blog post LVDS for multipoint applications we looked at the TIA/EIA-899 or MLVDS standard and a typically end application. In this post, we will discuss SerDes (Serializer/Deserializer) and the various technologies and applications they are used in. SerDes are devices that compress a wide bit-width parallel bus into a few, typically one, differential serial link that is switching at a much higher rate than the low speed wide bit-width parallel bus. SerDes make it possible for large amounts of data to be transported point-to-point within a system, between systems, or between systems in two different locations while reducing power, board space and cost due to the serialization of the wide bit-width parallel bus. Figure 1 below depicts the basic concept the SerDes. Figure 1: Serialization / Deserialization As data rates increase, the number of problems associated with implementing a parallel bus are intensified. A faster switching bus will consume more power than a slower switching bus while layout becomes much more difficult with the increased number of lanes as timing tolerances are reduced. With increased data rates maintaining lane-to-lane skew becomes crucial because large discrepancies in skew lead to system timing problems as a receiver needs to clock in the parallel data bus as a group of aligned bits. Also, as today’s designs become more compact board space is at a premium, so a large parallel bus is going to eat into valuable PCB real estate. SerDes offer a good solution for the aforementioned design challenges by reducing cost, power, and board space. We will first take a simple SerDes example to describe their basic operation as some of today’s SerDes devices can be a bit cumbersome. Clocking is extremely important in applications that make use of a SerDes as everything has to happen at a given time and cannot occur randomly. A system clock can be distributed to all components including the SerDes aiding in synchronous operation. An end point device, such as a network processing unit (NPU) or FPGA, has parallel data output running at the desired system frequency, connected to the parallel interface of a SerDes device. The parallel data is clocked into the SerDes FIFOs on the rising, falling, or both clock edges of the system clock. How the data is clocked into the FIFO depends upon the SerDes vendor as well as the end application that is targeted. Parallel data will typically be encoded into a standard encoding scheme such as 8B/10B encoding to make it suitable for serialization. Raw application data can contain pathological patterns, long runs of ones and zeros, which can make it difficult for a SerDes to catch a bit transition. Encoding the data removes pathological patterns ensuring that the data stream is transition dense and DC balanced. Another challenge for un-encoded data is that word delineation is lost through the serialization process so encoding the data into ten bit words assures the receiver can determine proper word delineation. The comma character (0011111 or 1100000) or K28.5 (0011111010 or 1100000101) is commonly used, but other synchronization words can be used. The K28.5 character is inserted by the transmitting SerDes for the receiver to detect as an alignment character. The serialized data is then driven out into the media to the receiving SerDes device. Figure 2 below shows an example of 8B/10B encoding. Figure 2: 8B/10B Encoding The receiving SerDes translates the incoming bit stream, represented by voltage swings, into a digital bit stream. The receiver also incorporates a CDR (clock and data recovery circuit) which recovers a byte clock from the incoming DC balanced data stream. The receiving SerDes is running off of its own local reference oscillator, but this is phase aligned with the recovered byte clock and used to clock the received bit stream. The received bit stream is then de-serialized and feedback to the parallel bus to the awaiting end point device. The TLK1501 is a multigigabit transceiver that is used in high speed point-to-point data transmission systems. The TLK1501 supports a 16 bit wide parallel interface that reads data in on the rising clock edge of the reference clock. The parallel bus is 8B/10B encoded, serialized, and transmitted sequentially over a differential high speed media. The receiver portion of the TLK1501 accepts 8B/10B encoded data to which its CDR will lock to, extract a bit clock from and retime the input data stream. The serial data stream is then aligned into separate 10 bit word boundaries, decoded and driven out onto the 16 bit wide bus to the waiting end device. The TLK1501 is a simple device to design with that will reduce system cost, power and board space. For more information on specific SerDes application solutions, please visit the High Speed Interface Forum in TI’s E2E™ Community and check out existing posts from engineers already using TI interface products, or create a new thread to address your specific application. Additional information can be found regarding basic SerDes operation in the article “The basics of SerDes (serializers/deserializers) for interfacing” written by my colleague, Atul Patel. Please join me for my next post in the Get Connected series where we will discuss some industry standard interfaces that attach to SerDes. If you are not connected, you can get connected here with one of the broadest Interface portfolios in the industry. Leave your comments in the section below if you’d like to hear more about anything mentioned in this post or if there is a topic you'd like to see us tackle in the future! And be sure to check out the full Get Connected series! 0 comments 0 members are here