CPU Architecture: Registers, Instructions, Addressing Modes

advertisement

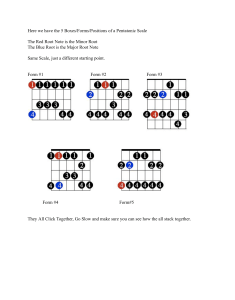

Reference: http://ecl.incheon.ac.kr/ We will study … • Chapter 8: Central Processing Unit: – – – – – – General Register Organization Stack Organization Instruction Formats Addressing Modes Data Transfer and Manipulation Program Control 2 Major Components of CPU • Storage Components – Registers – Flags • Processing Components – Arithmetic Logic Unit (ALU): Arithmetic/Logical computations, Shifts/Rotates • Transfer Components – Bus • Control Components – Control Unit 3 Registers • In BC, – Only one general purpose register, the Accumulator (AC) • In modern CPUs, – Many general purpose registers • Many registers --> advantageous because : – Transfer between registers within the processor are relatively fast – Going off the processor to access memory is much slower 4 General Register Organization 5 Operation of Control Unit • The Control Unit : Direct the info flow through ALU by : – selecting various Components in the system – selecting the Function of ALU • Example: R1 ← R2 + R3 – – – – [1] MUX A selector (SELA): BUS A ← R2 [2] MUX B selector (SELB): BUS B ← R3 [3] ALU operation selector (OPR): ALU to ADD [4] Decoder destination selector (SELD): R1 ← Out Bus • Control Word (14 bits) • Encoding of register selection fields: Table 8.1 6 ALU Control • Encoding of ALU operations: Table 8.2 Examples of ALU Microoperations: Table 8.3 7 In Class Activity Q8-4: Determine the microoperations that will be executed in the processor of Fig. 8-2 when the following 14-bit control words are applied. a. 001 010 011 00101 b. 000 000 000 00000 c. 010 010 010 01100 d. 000 001 000 00010 e. 111 100 011 10000 8 In Class Activity-Solution Q8-4: Solution: Control Word SELA SELB SELD OPR Microoperation a 001 010 011 00101 R1 R2 R3 SUB R3 R1 – R2 b 000 000 000 00000 Input Input None TSFA Output Input c 010 010 010 01100 R2 R2 R2 XOR R2 R2 R2 d 000 001 000 00010 Input R1 None ADD Output Input +R1 e 111 100 011 10000 R7 R4 R3 SHRA R3 shr R7 9 Register Stack Organization • Stack is good for : – Very useful feature for nested subroutines, nested interrupt services – Efficient for arithmetic expression evaluation • What is Stack? – Storage which can be accessed in LIFO – Stack Pointer (SP): the stack top pointer – Only PUSH and POP operations are applicable Register Stack Push-Pop operations 10 Memory Stack Organization • Memory stack: a portion of memory is used as a stack, With a processor register as a stack pointer • Memory partitioned into three types of segments: – Program, Data, Stack segments Push-Pop Overflow/underflow Most computers do not provide HW to check stack overflow (full stack) or stack underflow (empty stack) --> must be done in SW (Two registers are used to hold the upper(3000)/lower (4001) limits: After push/pop operation, SP is compared with the upper/lower limit) 11 Reverse Polish Notation • Common Arithmetic Expression: A + B A+B Infix notation +AB Prefix notation or Polish notation AB+ Postfix notation or reverse Polish notation - reverse Polish notation: very suitable for stack manipulation • Evaluation of Arithmetic Expressions – Any arithmetic expression can be expressed in parenthesis-free (reverse) Polish notation – A * B + C * D => AB*CD*+ – (A + B) * [C * (D + E) + F] => AB + DE + C * F + * 12 Reverse Polish Notation (cont.) • Arithmetic Expressions are evaluated as follows: – Scan expression from left to right – When an operator is reached, perform the operation of the with two operands found on the left side of the operator. – Remove the two operands and the operator and replace them by the number obtained from the result of the operation. – Repeat the procedure for every operator until there are no more operators 13 In Class Activity Q8-8: Convert the following arithmetic expressions from reverse Polish notation to infix notation. • ABC*/D–EF/+ 𝐴 • Solution: B∗C −𝐷+ 𝐸 𝐹 14 In Class Activity-Solution Q8-9 Convert the following numerical arithmetic expression into reverse Polish notation and show the stack operations for evaluating the numerical result. (3 + 4)[ 10 (2 + 6) + 8] Solution: (3 + 4) [10 (2 + 6) + 8] = 616 RPN: 3 4 + 2 6 + 10 * 8 + * Processor Organization • Most processors are organized in one of 3 ways : – Single register (Accumulator) organization • A good example: BC • Accumulator is the only general purpose register – General register organization • Used by most modern computer processors • Any of the registers can be used as the source or destination for computer operations – Stack organization • All operations are done using the hardware stack • For example, an OR instruction will pop the two top elements from the stack, do a logical OR on them, and push the result on the stack 16 Instruction Formats • Instruction Fields : – opcode field(s) – specify the operations to be performed – Address field(s) – designate memory address(es) or processor register(s) – Mode field – determine how the address field is to be interpreted to get effective address or the operand • The number of address fields in the instruction format : depend on the internal organization of CPU • The three most common CPU organizations : – Single accumulator organization : ADD X /* AC ← AC + M[X] */ – General register organization : ADD R1, R2, R3 /* R1 ← R2 + R3 */ ADD R1, R2 /* R1 ← R1 + R2 */ MOV R1, R2 /* R1 ← R2 */ ADD R1, X /* R1 ← R1 + M[X] */ – Stack organization : PUSH X /* TOS ← M[X] */ POP X /* M[X] ← TOS */ ADD 17 Three-, Two-address Instructions • Three-address Instructions – Program to evaluate X = (A + B) * (C + D) : ADD R1, A, B /* R1 ← M[A] + M[B] */ ADD R2, C, D /* R2 ← M[C] + M[D] */ MUL X, R1, R2 /* M[X] ← R1 * R2 */ – Results in short program – Instruction becomes long (many bits) • Two-address Instructions – Program to evaluate X = (A + B) * (C + D) : MOV R1, A /* R1 ← M[A] */ ADD R1, B /* R1 ← R1 + M[B] */ MOV R2, C /* R2 ← M[C] */ ADD R2, D /* R2 ← R2 + M[D] */ MUL R1, R2 /* R1 ← R1 * R2 */ MOV X, R1 /* M[X] ← R1 */ 18 One-, Zero-address Instructions • One-address Instructions – Use an implied AC register for all data manipulation – Program to evaluate X = (A + B) * (C + D) : LOAD A /* AC ← M[A] */ ADD B /* AC ← AC + M[B] */ STORE T /* M[T] ← AC */ LOAD C /* AC ← M[C] */ ADD D /* AC ← AC + M[D] */ MUL T /* AC ← AC * M[T] */ STORE X /* M[X] ← AC */ • Zero-address Instructions – Can be found in a stack-organized computer – Program to evaluate X = (A + B) * (C + D) : PUSH A /* TOS ← A */ PUSH B /* TOS ←B */ ADD /* TOS ← (A + B) */ PUSH C /* TOS ←C */ PUSH D /* TOS ←D */ ADD /* TOS ← (C + D) */ MUL /* TOS ← (C + D) * (A + B) */ POP X /* M[X] ← TOS */ 19 In Class Activity Q8-11: A computer has 32-bit instructions and 12-bit addresses. • If there are 250 two-address instructions, how many oneaddress instructions can be formulated? • Solution: 8 12 12 =32 bit Op code Address 1 Address 2 Two Address Instr 28 = 256 combinations 256 – 250 = 6 combinations for one address 20 Op code 12 =32 bit Address One Address Instr Maximum number of one address instruction = 6 x 212 = 24,576 20 In Class Activity Q8-12 Write a program to evaluate the arithmetic statement: 𝐴 − 𝐵 + 𝐶 ∗ (𝐷 ∗ 𝐸 − 𝐹) 𝑋= 𝐺+𝐻∗𝐾 a.Using a general register computer with three address instructions. b.Using a general register computer with two address instructions. c.Using an accumulator type computer with one address instructions. d. RPN: X AB –DE * F – C + * GHK * + /= In Class Activity-Solution A8-12: a. Three address SUB R1, A, B MUL R2, D, E SUB R2, R2, F MUL R2, R2, C ADD R1, R1, R2 MUL R3, H, K ADD R3, R3, G DIV X, R1, R3 b. Two address MOV R1, A SUB R1, B MOV R2, D MUL R2, E SUB R2, F MUL R2, C ADD R1, R2 MOV R3, H MUL R3, K ADD R3, G DIV R1, R3 MOV X, R1 d. RPN: X AB –DE * F – C + * GHK * + /= c. One address LOAD A SUB B STORE T LOAD D MUL E SUB F MUL C ADD T STORE T LOAD H MUL K ADD G STORE T2 LOAD T DIV T2 In Class Activity Q8-13 The memory unit of a computer has 256K words of 32 bits each. The computer has an instruction format with four fields: an operation code field, a mode field to specify one of seven addressing modes, a register address field to specify one of 60 processor registers, and a memory address. Specify the instruction format and the number of bits in each field if the instruction is in one memory word. Solution: Addressing Modes • Addressing Modes –Specifies a rule for interpreting or modifying the address field of the instruction before the operand is actually referenced. – The purpose of addressing modes • to give programming flexibility to the user • to use the bits in the address field of the instruction efficiently Mode field Opcode Mode Address • Opcode, specifies the operation to be performed • Mode, locate the operands needed for the operation • Address, it may denote a memory address or CPU register 24 Types of Addressing Modes – (1) • Implied Mode: – Address of the operands are specified implicitly in the definition of the instruction – No need to specify address field in the instruction – EA = AC, or EA = Stack[SP] – Examples from BC: CLA, CME, INP • Immediate Mode: – The operand is specified in the instruction itself, instead of specifying the address of the operand. LDA #NBR AC<-----NBR – No need to specify address field in the instruction LDA #10 – However, operand itself needs to be specified AC<---10 – (-) Sometimes, require more bits than the address – (+) Fast to acquire an operand – Useful for initializing registers when operand has constant value 25 Types of Addressing Modes – (2) • Register Mode: – Address specified in the instruction is the register address – The operand is in a register in the CPU - Add r1, r2, r3 – (+) Shorter address than the memory address • Saving address field in the instruction – (+) Faster to acquire an operand than the memory addressing – EA = IR(R) (IR(R): Register field of IR) • Register Indirect Mode: – Instruction specifies a register which contains the memory address of the operand – (+) Saving instruction bits since register address is shorter than the memory address – (-) Slower to acquire an operand than both the register addressing or memory addressing – EA = [IR(R)] ([x]: Content of x) • Autoincrement or Autodecrement Mode – Similar to the register indirect mode except : – When the address in the register is used to access memory, the value in the register is incremented or decremented by 1 automatically 26 Types of Addressing Modes – (3) • Direct Address Mode: – Instruction specifies the memory address which can be used directly to access the memory – (+) Faster than the other memory addressing modes – (-) Too many bits are needed to specify the address for a large physical memory space – EA = IR(addr) (IR(addr): address field of IR) – E.g., the address field in a branch-type instruction • Indirect Addressing Mode: – The address field of an instruction specifies the address of a memory location that contains the address of the operand – (+) Number of bits is less in the address – (-) Slow to acquire an operand because of an additional memory access 27 – EA = M[IR(address)] Types of Addressing Modes – (4) • Relative Addressing Modes: – The Address fields of an instruction specifies the part of the address, which can be used along with a designated register (R) to calculate the address of the operand, it a signed address, which can be either positive or negative – --> Effective Addr (EA)= addr part of the instr + content of a CPU-R – (+) Large physical memory can be accessed with a small number of address bits – EA = f(IR(address), R), R is sometimes implied – --> Typically EA = IR(address) + R – 3 different Relative Addressing Modes depending on R • (PC) Relative Addressing Mode (R = PC) • Indexed Addressing Mode (R = IX, where IX: Index Register) • Base Register Addressing Mode (R = BR (Base Register)) • Indexed addressing mode vs. Base register addressing mode: – Difference: the way they are used (NOT the way they are computed) • XR holds an index number that is relative to the address part of the instruction. • BR holds a base address and the address field of the instruction gives a displacement relative to this base address. – IR(address) (addr field of instr) : base address vs. displacement 28 – R (index/base register): displacement vs. base address Summary of Addressing Modes – (5) Addressing Mode Explanation Implied Mode Operands are built in the definition of the instruction. Example EA = AC, or EA = Stack[SP] CLA, CME, INP Immediate Mode The operand is the second part of the instruction Load R1, 5 Register Mode Operands are in registers that reside in CPU, no adds. Add R1, R2, R3 Register Indirect The memory address of the operand is specified in a EA = [IR (R)] Mode register. ([x]: Content of x) Autoincrement or The value in the register is incr. or decr. by 1 AC AC+1, ACAC–1 Autodecrement automatically SP SP +1, SP SP–1 Direct Mode The EA is the address part of the instruction ???? and EA = part of IR(addr) the operand to be loaded into AC is XXX (an operand in IR(addr)) Indirect Mode The 222 is stored in memory at address 111. Therefore, EA = Address 111 is the EA is 222 and the operand is 333. address of 222 that 333. EA = M[IR(address)] Relative The Address part of instruction added with the PC to EA=PC + add. field inst. Addressing Modes calculate the EA of operand. It is a signed address, can = 825(+1) + 24 be positive or negative. = 826 + 24 = 850 Indexed The EA = the content of XR added with the address part EA=XR/CPU reg.+instr. addressing Mode of the instruction. part Base register Similar to index, facilitate the relocation of programs in EA=BR+ add. part of 29 addressing Mode memory in multiprogramming systems instr. Addressing Modes: Examples 30 In Class Activity Q8-15: A relative mode branch type of instruction is stored in memory at an address equivalent to decimal 750. The branch is made to an address equivalent to decimal 500. a. What should be the value of the relative address field of the instruction (in decimal)? b.Determine the relative address value in binary using 12 bits. (Why must the number be in 2's complement?) c. Determine the binary value in PC after the fetch phase and calculate the binary value of 500. Then show that the binary value in PC plus the relative address calculated in part (b) is equal to the binary value of 500. 31 Tutorial - In Class Activity - Solution A8-15: Solution: a. Relative address = 500 – 751 = – 251 b. 251 = 0000 1111 1011; – 251 = 1111 0000 0101 c. PC = 751 = 001011101111; PC = 751 = 0010 1110 1111 RA = – 251 = +1111 0000 0101 ------------------------------------------EA = 500 = 0001 1111 0100. 32 Data Transfer Instructions Three classes in a basic set of operations: – Data transfer Instructions – Data manipulation Instructions – Program control Instructions Typical Data Transfer Instructions Data Transfer Instructions with Different Addressing Modes Example: load to AC 33 Data Manipulation Instructions • Three Basic Types of Data Manipulation instr’s: • logical and bit manipulation instr’s – arithmetic instr’s – logical and bit manipulation instr’s – shift instr’s • arithmetic instr’s • shift instr’s 34 Program Control Instructions +1 In-Line Sequencing (Fetch next instr from the next adjacent location in the memory) Address from other source (Current instr, Stack, etc.): Branch, Conditional Branch, Subroutine, etc. Program Control Instructions 35 Flag, Processor Status Word • In BC, – The processor has several (status) flags – Each flag : 1 bit value that indicates various info about the processor’s state – E, FGI, FGO, I, IEN, R • In some processors, – Flags are often combined into a register • processor status register (PSR) or processor status word (PSW) • Common flags in PSW : – – – – C (Carry): 1 if the carry out of the ALU is 1 S (Sign): the MSB bit of the ALU’s output Z (Zero): 1 if the ALU’s output is all 0’s V (Overflow): 1 if there is an overflow 36 Conditional Branch Instructions Table 8-11 37 Conditional Branch Instr. (cont.) • Subtraction is done in the same way in both signed and unsigned numbers. – For example, to evaluate (A – B) it is computed as the result of adding A to the 2’s complement of B. • Consider an 8-bit ALU, as shown in the previous figure. – Range of unsigned numbers 0 -> 255 – Range of signed numbers -128 -> +127 38 Conditional Branch Instr. (cont.) • Let A = 11110000, and B = 00010100 • To perform A – B, the ALU takes 2’s comp of B (11101100) and adds it to A – So, A-B = 11110000 + 11101100 = 11011100 – And flags C = 1, S = 1, V = 0, Z = 0 – A-B = 11011100, C=1, S=1, V=0, Z=0 39 Conditional Branch Instr. (cont.) • If we assume unsigned numbers – A = 240, B = 20 , A-B = 220. – A > B, A B, (C = 1, Z = 0), – So the instr that will cause branch after this comparison will be BHI, BHE, and BNE. • If we assume signed numbers – A = -16, B = 20 , A-B = -36. – A < B, A B, (S = 1, V = 0, Z = 0), – So the instr that will cause branch after this comparison will be BLT, BLE, and BNE. 40 In Class Activity Q8-29: Consider the two 8-bit numbers A = 0100 0001 and B = 1000 0100. a. Give the decimal equivalent of each number assuming that (1) they are unsigned, and (2) they are signed. b. Add the two binary numbers and interpret the sum assuming that the numbers are (1) unsigned, and (2) signed. c. Determine the values of the C, Z, S, and V status bits after the addition. d. List the conditional branch instructions from Table 8-11 that will have a true condition. 41 In Class Activity - Solution A8-29: Solution: Unsigned Signed a. A = 0100 0001 65 + 65 b. B = 1000 0100 A+B = 1100 0101 132 197 - 124 59 c. C = 0, Z = 0, S = 1, V = 0 d. BNC BNZ BM BNV 42 Subroutine Call and Return • Subroutine Call Instructions (instr that transfer program control to a subroutine): – aka: Call subroutine, Jump to subroutine, Branch to subroutine, Branch and save return address • Two most important operations : 1. Save the return address to get the address of the location in the calling program upon exit from the subroutine 2. Branch to the beginning of the subroutine (Same as the branch or conditional branch) • Locations for storing return address : – Fixed location in the subroutine (memory) – Fixed Location in memory – In a processor register – In memory stack -- most efficient way 43 Subroutine Call and Return • Call and return using stack : – Most efficient way – (+) Return address : always at the top of the stack • do not need to concern where the return addr was stored – (+) allow other calls before return – (+) allow recursive subroutine call • Implementation (microoperations) 44