[The Oxford Series in Electrical and Computer Engineering] Adel S. Sedra, Kenneth C. Smith - Microelectronic Circuits 7th edition(2014, Oxford University Press) - libgen.lc

advertisement

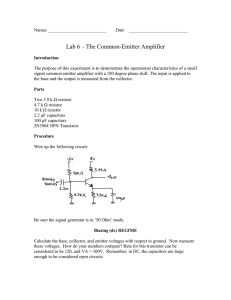

![[The Oxford Series in Electrical and Computer Engineering] Adel S. Sedra, Kenneth C. Smith - Microelectronic Circuits 7th edition(2014, Oxford University Press) - libgen.lc](http://s2.studylib.net/store/data/025736342_1-5c99b1d5fad6805f11fc8211d5d9578c-768x994.png)