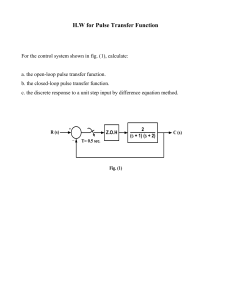

2016 IEEE International Conference on “Electrical Power and Energy Systems” High Power Pulsed Current Laser Diode Driver Ashutosh Sharma*,C.B.Panwar and R.Arya Solid State Laser Electronics Section, Raja Ramanna Center of Advanced Technology Indore (India) *e-mail: ashu@rrcat.gov.in Abstract— The design and implementation of a pulsed current drive for a high power Laser Diode has been presented. The singlestage SMPS does not use any linear regulator, and is able to pump upto 50A in a 2V laser diode or in two laser diodes in series for a maximum of 4V output with an achievable rise and fall times of around 80 μs. Various protections to safeguard costly and sensitive Laser Diode have been employed. Keywords— Pulsed Laser Diode driver; single stage SMPS; peak current programmed algorithm; 3rd order filter. I. INTRODUCTION Electrically, a semiconductor Laser Diode behaves as a normal diode with a turn on knee voltage greater than 1 V and a series resistance of the order of few milliohms. It begins to lase at a current greater than threshold current of around 8A at 1.4V. A further increase in the injected current results in a proportional increase in laser optical output [1]. Laser Diode (LD) pumped solid state lasers and fibre lasers have progressed spectacularly over the last decade. Applications range from their use in laboratory by a research scholar to their use in health care including laser imaging and ophthalmology and to an ever increasing commercial use upto kilowatt level in areas of defense, gas and oil well drilling, cutting and welding in manufacturing industry, ship yards, pipe lines and rocks [2,3]. All these laser systems need a high performance LD driver that drives the LD in Continuous Wave (CW) mode or pulsed mode. SMPS based Laser diode (LD) drivers are preferable over linear drivers for their better efficiency and compactness. Reference [4] details the design of an LD drive for pumping dc current or Quasi-CW current with slow rise and fall times. However, its low bandwidth limits its immediate use for fast pulsed operation of an LD. Pulsed LD drivers generally have two stages, an SMPS voltage source followed by a linear stage wherein power MOSFETs or BJTs are operated as linear regulators to drive pulsed current through the LD [5-6]. Such LD drivers can generate fast enough rise and fall times of 1µs to 10µs, but also suffer from lower electrical efficiency owing to power loss in the linear stage. Pulsed LD drivers generating very fast current rise-fall times of 20ns have been reported [7]. A constant current source is realized by a buck converter with single inductor filter. It is switched by providing complementary base drives in open loop to non-saturating emitter-coupled transistor pair in differential configuration to pulse the LD current, LD being in series with one of the transistors. However, the reported power handling capacity is upto 1.5W [7]. In this paper, design and implementation of a 978-1-5090-2476-6/16/$31.00 ©2016 IEEE 200W single stage pulsed current LD driver is presented. Section II briefly reminisces Quasi-CW and CW Laser Diode driver, details of which can be had from [4], and its limitations for fast pulsed applications. Section III introduces a novelty in control scheme wherein power stage of CW driver is appropriately transformed into pulsed current source with fast enough transition times and with good stability. Section IV describes equivalent control block diagram and transfer functions. Experimental results of a prototype 50A, 4V pulsed laser diode driver based on the proposed methodology are presented in section V, and summary of the contributions of this paper is given in section VI. II. SINGLE STAGE CW LASER DIODE DRIVER AND ITS LIMITATIONS FOR FAST PULSED APPLICATIONS A. Power Circuit and Control Strategy Before analyzing the proposed pulsed LD driver, power circuit of a single stage CW LD driver as in [4] is reminisced here briefly. It is based on buck converter in the form of a two switch forward converter. It is more suitable than other power topologies for an output power of upto 1kW because of its simple configuration, isolation from input source, ruggedness and high reliability. Its small signal transfer function is free from any RHP zero leading to easy controllability and higher phase margin, etc. To transform an SMPS into a rigid current source which can drive the LD, current mode control is the method of choice. Applicable current mode control techniques include average current mode control [8], peak current programmed control [8,9], integral charge control [10], etc. Peak current mode control is better option for controlling LD drivers owing to faster system dynamics, excellent line regulation, simple compensation design, robustness to large load variations, and inherent pulse by pulse current limiting[8,9]. The control structure adopted for the single stage CW LD driver has an inner loop based on pulse-by-pulse peak current mode control and outer loop for tighter control effected by a P-I type slow average current mode control. Fig. 1 and Fig. 2 respectively illustrate the circuit diagram and small signal equivalent control block diagram. A constant frequency clock turns on the two MOSFETs Q1 & Q2 at the beginning of each switching cycle. The switch current IQ1 = IQ2 = IL1 /N1 and hence its sensed signal Vs=IL1.RS1/N1.N2 grows until it reaches the control reference Vc coming from the outer loop controller Gc. Then the comparator changes its state and turns off the Chebyshev 0.5dB filter iL1 3 2 500uF BY V-26C iD MBR4045 Lm BY V-26C Hall sensor LA 100P Q2 1:N3::1:2000 IRF840 N1:1 Peak current sense Rs1 1:N2::1:50 Laser Diode 4 R 30mohm C Rs1=200 1 Power Transformer IRF840 Bulk Cap 230V ac mains EMI Filter 3uH L1 ,5uH MBR4045 Q1 Rect bridge L2 Vs UC3845N + S Pulse Trans 1 3 Vc + OUT - Q R Compensator Gc Vref Clock Pulse fs= 250kHz Fig. 1. Peak current programmed buck/forward converter based CW Laser Diode driver sufficiently attenuate current ripple of LD current with smaller MOSFETs. Thus the peak value of the current through size filter elements. Converter switching frequency fs is kept MOSFETs and correspondingly through the inductor L1 is sufficiently high (250 kHz) to further aid this goal. Output controlled directly whereas the pulse-width is not. This filter’s third element L2 being in series with LD gives the amounts to feedforward action which plays a vital role in converter a property of being a high output impedance current rejecting 100 Hz line perturbations ũin before they affect output source. Furthermore, whenever an LD is freshly connected to LD current ILD. The dynamic range of the outer loop the converter, any residual charge in output capacitor C can compensator Gc is not even used here. Gc compensates for only discharge in LD through inductor L1, thus preventing load and parametric variations, and for the error, if any, occurrence of current spike to pass through LD and possibly between LD current ILD and command reference Vref. damage it. Besides, Gc decides the phase margin and -3dB bandwidth of Design of third order filter with suitable cut-off and proper the LD driver. If Gc is designed as a phase-lag or P-I based load matching is as following. To filter the unipolar voltage at compensator that involves integration, Gc guarantees zero the secondary of the transformer, a Chebyshev 0.5dB passive steady state dc error for LD current. The output of Gc is Vc filter is selected with a cutoff frequency of 4.8 kHz and load which becomes reference for inner loop and acts as peak resistance of R= 30 mΩ. At a nominal frequency of ωn = 1 current limit for MOSFETs Q1 and Q2 every cycle. An rad/s, its elements are Rn=1Ω , L1n = 1.572 H. L2n= 0.932 H, artificial ramp is generally added, not shown in Fig. 1, to a and Cn = 1.518 F [12]. After frequency scaling and magnitude degree to the sensed MOSFET current Vs in order to eliminate scaling, these filter values nearly become L1= 5µH, L2= 3µH, the oscillation that occurs when the duty ratio d ≥ 0.5 [8,11]. In and C=500µF. Inductances L1 and L2 are wound on our case d<0.5 for all line and load conditions, but still some appropriate dust cores with Litz wires and have series ramp is added to increase relative stability and to make the resistance of around 2 mΩ each. Five low ESR capacitors of peak current controller more immune to noise especially at low 100uF, 63V are connected in parallel to add up to the required loads and the duty cycle d less jittery [11]. value of 500µF. Converter operates in continuous conduction Input Line ~ mode for an LD current range of 2A to 50A for these values of Variations, uin filter elements which has also been verified using P-spice L1 L2 R Vc simulation. The Chebyshev filter in Fig. 1 attenuates the input PWM + forward + Gc C Converter ripple of 250 kHz by nearly 70 dB. At LD current of 50 A dc, Vref the ripple current is 40mA pk-pk at 250 kHz. The ripple in L1 IL1/N1.N2 I Switch Current Vs LD is 2A under same conditions. Rs1 Rs2 Fig. 2. Equivalent block diagram of the CW Laser Diode driver B. Output Filter Design As is depicted in Fig. 1, instead of conventional second order filter, power transformer output is imposed on a third order passive filter consisting of elements L1, C and L2, to C. Transforming into Pulsed LD Driver CW diode drivers based on the above-mentioned design [4] and depicted in Fig. 1 are good for pumping LD with CW and slow QCW current-drive; however, very fast rise/fall time for LD current is not achievable owing to the bandwidth limitations of its control, and especially due to the average current mode PI type compensator Gc employed. When the LD driver described above is driven by a pulsed reference signal at ICEPES 2016 iL1 EMI Filter 1 4 3 2 IRF840 Power Transformer R 30mohm C 500uF BY V-26C MBR4045 Lm BY V-26C Bulk Cap 230V ac mains Rect bridge L2 3uH L1 ,5uH MBR4045 iD Laser Diode N1:1 IRF840 Rs1 1:N2::1:50 ~ Vs UC3845N Peak current sense + Q R OUT - 1 3 . Vc 10 Hz to 1kHz S Pulse Trans Clock Pulse fs= 250kHz Fig. 3. Opening the outer loop and driving the inner peak current programmed loop by a pulse reference. Vref, current rise time of more than a millisecond is achieved depending on outer loop bandwidth and system phase margin. The particular application considered in this paper requires one LD rated for 50A, 2V or two in series (50A,4V maximum) to be driven with rectangular current modulated between threshold level adjustable upto 15A and power level adjustable upto 48A, with a rise time of around 50-100µs and overshoot less than 5%. The pk-pk ripple should be less than 50mA. A pulse input reference signal of rep-rate of 1Hz to 1 kHz and duty cycle from 5 % to 80% shapes the current. In this work, we introduce a novelty in control scheme within the same power structure to bring down rise/fall times from 5 ms to ~ 80µs. Vc(s) . i L1(s) Fig. 4(a). îL1 as function of Vc(s) . i L1(s) 1/(1+ R.C.s +L2.C.s2) ~ i D(s) Fig. 4(b). ῑ D (s) function of ῑ L1(s) L2 Peak current programmed source R C III. THE CIRCUIT AND PRINCIPLE OF OPERATION OF SWITCHMODE PULSED LD CURRENT DRIVER Let us open the slow outer loop and apply a pulsed voltage at say 100 Hz rep-rate as the control signal Vc as given in Fig. 3. The peak current of inductor L1 is clamped every cycle by the value of Vc(t). If Vc is pulsed, the LD current is also pulsed, with rise and fall times governed by the filter values and its cut-off frequency, rise time being slightly bettered by high initial duty ratios (nearly 50% every switching cycle) during rise time till upper level peak-current limit is reached. Overshoot will also be minimal owing to peak current limit imposed by Vc every switching cycle. Additionally, since filter elements L1, L2 and C have lower Q factor and thus, resistive losses, there is insertion loss in the passband with no change in the stopband at high frequencies. The advantage gained in pulsed operation is that if Chebyshev filter is terminated in slightly unmatched load resistance, the reflections will be minimal as they are damped by the filter non-idealities and correspondingly current overshoot will be minimal. Also the filter passband ripple is reduced significantly. Undershoot at falling edge will also be minimized owing to aforementioned reasons. The converter of Fig. 3 can be represented by control blocks of Fig. 4(a) and (b). îL1, the peak current in inductor L1 is proportional to the pulse reference voltage Vc(s) every cycle; N1.N2/Rs1 1/3 iL1 = Vc.N1.N2/Rs1 iD Laser Diode Fig. 4(c). IL1 as current source ῑL1 is the average current in L1 and equal to the average diode current īD. 1:N2 is CT turns ratio (equal to 1:50 in present case) through which switch current is sensed, Rs1 is the CT burden, N1:1 is the power transformer turns ratio (equal to 24:1). Fig. 4(c) depicts iL1 as a pulse by pulse corrected current source driving the elements that follow it. Equation (1) gives the approximate composite average transfer function of the pulsed LD driver, and it holds when îL1, peak of inductor current L1 equals its average current ῑ L1, which is nearly valid when the ripple current in inductor L1 is small. Therefore, for low ripple case, ~ iD ( s ) (1 / 3 )( N 1 . N 2 / Rs 1) Gp ( s ) = ≈ 2 vc ( s ) 1 + RCs + L 2 Cs − ∧ , if i L 1 ≈ i L 1 (1) Fig. 3 and ῑ D – ῑ L1 – îL1 –VC relations given by the control block diagrams in Fig. 4(a) and Fig. 4(b) indicate that the steady pulsed reference VC directly controls the peak of inductor current îL1 every switching cycle, but not its average value ῑ L1 per switching cycle. It has been experimentally measured that īL1, the per cycle average of current in L1, which is equal to the average output diode current ῑD, ICEPES 2016 iL1 L1 Rect bridge EMI 1 4 Filter 3 2 L2 3uH 5uH R 30mohm Power Transformer C IRF840 Bulk Cap 230V ac mains MBR4045 500uF BY V-26C IRF840 24:1 Laser Diode iD MBR4045 Lm BY V-26C 1:2000 N1:1 Rs1=24 1:N2::1:50 Rs1=200 ~ Vs +15V S Vc Clock Pulse fs= 250kHz T=4us R2 W Y1 8k2 6 Z AD633 X1 X2 Y2 AD620 k 1 + 3 2 4 1M 1k 2 Reset 1 5 + RG1 OUT REF RG2 - 3 1 1k 8 2 1k Pulsed LD current reference Vp_ref(t) Power level Difference Amp 33k 1uF 5 -15V Weighted pulsed reference 6 - -15V R1 Pulse Trans 7 V+ 1 3 4 8 - V+ OUT V- Q R 7 +15V + V- UC3845N Integrator Multiplier X1.Y1/10 x(1+R2/R1) = X1.Y1/2 Threshold level 0A Rep rate 10Hz to 1kHz Duty 1 % to 80% Fig. 5. Realization of pulsed Laser Diode current drive with steady average value. for the case described. At the same time, zero steady state gradually drifts with time due to parametric changes such as a) error is achieved due to the integrator introduced, and the change in LD knee voltage that decreases with increase in average value of pulsed LD current ῑD remains constant with junction temperature b) change in diode bulk resistance which time and equal (or proportional) to the average value of the increases with increase in junction temperature c) change in pulsed reference Vp_ref. Slow changes in utility mains, in the number of diodes seriesed as load, etc. The drift was converter components, in LD knee voltage or its bulk recorded to be upto ± 10 % which is usually unacceptable in a resistance are thus rejected keeping the laser diode output typical laser system application. It is desirable that the power constant. It may be pointed here that the command drift/steady state error in average of pulsed diode current ῑ D is pulsed reference signal Vp_ref has two levels as can be seen in eliminated, and yet its fast rise/fall time is maintained. To Fig. 5, its lower threshold level corresponds to the LD current achieve this, a correcting mechanism is introduced by means value beyond which the LD just begins to lase and upper of constantly adjusting the pulsed signal Vc by a weighting corresponds to a given optical output power. For the LIMO35factor ‘k’. This weighting factor ‘k’ is generated as follows: F200-DL806 Laser Diode, the LD currents of 10A and 50A The command pulsed reference Vp_ref, that decides correspond to the threshold (0W optical) and to the full optical the instantaneous value and shape of output LD current, is power of 35W respectively at 806nm [13]. compared with the pulsed LD current sense signal by a difference amplifier (based on IC AD620 as shown in Fig. 5). IV. EQUIVALENT CONTROL MODELLING The error voltage is integrated by the op-amp based integrator block 1/s to generate a slow moving variable at its output Fig. 6 shows the control block representation of two switch designated as ‘k’. This near dc weighting factor ‘k’ is forward converter with the correcting loop added to eliminate multiplied with the pulsed reference Vp_ref to result in drift in average of pulsed laser current. The feedback element weighted pulse reference Vc. It is this weighted pulsed Rs2/N3 represents the high bandwidth Hall based current reference that, as Vc in Fig. 5, is applied to the inner peak sensor LA 100P, that senses pulsed laser diode current, with a current programmed loop. This weighted pulsed signal Vc burden equal to Rs2. R is equal to the sum of resistance of programs the peak of L1 current, îL1. The overall result is that inductor L2 and of laser diode. The output of the integrator 1/s the LD current is pulsed in nature with its rise/fall times is the weighting factor ‘k’. The block ½ comes from the limited by the output filter elements, and of the order of ~80µs multiplier of Fig. 5. Recalling the value of Gp(s) from (1), the + - 1/s k 1/2 Vc(s) 1/3 N1.N2/Rs1 1/(1+ R.C.s +L2.C.s2) Pulsed diode Current, iD(s) Pulsed reference, Vp_ref(s) Pulsed reference, Vp_ref(s) Rs2/N3 Fig. 6. s-domain control block representation of converter ICEPES 2016 hours of continuous operation, for different values of pulse power current, duty ratios and repetition rate, without drift. ~ uin ~ Vc(s) Gp(s) 1/2 1/s + ~ i D(s) Vp_ref(s) - ~ Vp_ref(s) 1/10 Fig. 7. Simplified Control Block diagram of pulsed LD driver. control block of Fig. 6 is simplified to the small signal averaged model in Fig. 7. The model represents slow variations in averaged output LD current resulting from the slow variations in reference signal or in the input ac mains or from other sources. From Fig. 7, ~ ~ ~ ~ i D ( s ) v p _ ref ( s ) .Gp ( s ) = i D ( s ) } v p _ ref ( s ) − 10 2s ~ v p _ ref ( s ) − ~ iD (s) 10 = or, i ~ (s) = D ~ 2 . s .i D ( s ) ~ Gp . v p _ ref ( s ) (2) (3) ~ 10 . v p _ ref ( s ) s 1+ ~ Gp . v p _ ref ( s ) / 20 or, (4) For the particular application, N1 = 24, N2 = 50, N3=2000, Rs2 = 200 Ω, Rs1 = 24 Ω, R = 30 mΩ , L2 = 3 µH, C = 500 µF. Putting these values in (2) and substituting for G(p), we have, ~ 10 . v p _ ref ( s ) i D (s) = s 1+ ~ 5/6 v p _ ref ( s ) 2 1 + RCs + L 2 Cs ~ (5) Since, the averaged model is for slow variations in say LD resistance or components or input, we approximate, 1 1 + RCs + L 2 Cs 2 ≈ 1 ≈ 1, 1+ Δ ~ i D (s) ≈ when Δ << 1 s Vp _ ref ( s ) Thus, (7) Again for slow variations, s is small enough and the integrator with its large integrator constant of 1 second removes their effect and has nearly dc output, ‘k’. So the nonlinear relation (7) can be further approximated for low frequency region as ~ ~ i D ( s ) ≈ 10 . v p _ ref ( s ) The prototype of the pulsed LD driver described is shown in Fig. 8(a) and has been employed to pump one Laser Diode or two in series between threshold current and the set power current at various rep-rates and duty-ratios, all independently adjustable from the front-panel. Fig. 8(b) shows LD current pulse for 10A threshold and 38A of power value, at 33% duty ratio and 500 Hz rep-rate. The rise time is ~80µs with an overshoot of 3.5%, and the fall time is slightly larger and nearly 120µs owing to gradual decay of energy in filter elements. The transition times can be lowered further if stripline is used instead of a meter of twisted wire that has been employed as output cable in the prototype whose lead inductance negatively affects the fall time. Fig. 8(c) shows current at 20Hz rep-rate at a base current of 17A and power value of 34A. The ripple in the current is 15mA pk-pk @ 20A as depicted in Fig. 8(d). Fig 8(e) shows the input voltage impressed to the filter input at the positive transition of LD current from 0A to 40A. Fig. 8(f) shows the softness of current buildup in LD at system turn on when pulsed reference is initially impressed on the converter. This is achieved by gradual build-up of the scaled variable ‘k’ in Fig.5 once the integrator reset is released at turn-on. These waveforms verify that the LD operation is free from initial overshoot at turn-on/at the application of reference and from individual pulse-to pulse over-shoot at steady-state. Gradual establishment of initial current helps thermal stabilization of Laser Diode and prevents it from thermal stresses. Various other protections to prevent costly LD from damage include prevention against ESD by an electro-mechanical relay shortening its output terminals when not in use, potentiometer based LD current-limit, over-voltage, over-current, and reverse voltage protections. Fig. 8(a) shows the front panel controls available. Two BNC ports delivers signals in real time for pulsed reference Vp_ref (t) and LD current ID(t) for monitoring on oscilloscope. LD (not shown) is mounted on a thermo-electric (TE) cooler and maintained at 25oC so that optical power remains constant at constant current. The LD was also run with sine modulated current at 1 kHz over a dc value of 20A. It was seen that the beam quality is improved significantly, in particular, to its CW operation at almost all optical power levels. VI. CONCLUSIONS (6) 10 .Vp _ ref ( s ) 1 + (6 / 5 ) V. EXPERIMENTAL RESULTS (8) With the correcting mechanism in place, the pulsed diode driver showed stable average of pulsed LD current over many Design aspects of a pulsed single stage ac-dc LD driver with fast enough transition times have been presented in detail that does not use any linear stages. Its controller is based on peak current controlled algorithm driven by a weighted pulsed reference. The prototype LD driver described can deliver pulsed LD current adjustable upto 50A, 4V at duty cycle limited to 85% and with a rise/fall time of around 80 µs. Since linear regulator stages and/or auxiliary components are not employed, high power conversion efficiency is achieved. If faster LD current rise/fall times are required, the same can be achieved by shifting up the corner frequency of the output filter elements of the converter, resulting in its smaller individual values. However, it will amount to increased switching ripple which can be mitigated by interleaving two or ICEPES 2016 Fig. 8(a) Prototype LD driver Fig. 8(d) Current ripple in LD current at 20A Fig. 8(b) LD current pulse at 500Hz base value =10A, power value = 38A Fig. 8(e) Voltage impressed at filter input at positive edge transition from 0A to 40A more cells of buck/two-switch forward converters with phase staggered gate-drive [14]. The low ripple requirement of an LD driver can alternatively be met by shifting up the corner frequency of filter along with the converter switching frequency to above 800 kHz. These single stage pulsed driver may best yield rise/fall times of upto 10µs. For fasters rise/fall time down to say 100ns, the techniques employing linear regulator stages may be resorted to albeit at the cost of poorer conversion efficiency [5-7]. Interconnections to the laser should be through closely spaced parallel copper planes resembling a stripline so that rise/fall times of pulsed LD current and overshoot thereof, are not adversely affected. Such pulse laser diode drivers are in use at our centre for fiber laser development. [4] ACNOWLEDGMENT [10] Authors duly acknowledge Shri Dipen Vachhani for contributing to the multiplier circuitry and Shri G Srikanth for providing the laser load, both of this centre. [11] REFERENCES [12] [1] [2] [3] D.W. Hughes and J.R.M. Barr, “Laser Diode pumped Solid State Lasers,” J.Phys. D.Appl. Phys. vol.25, No. 4,1992. Mark S. Zediker, “High power fiber lasers in geothermal, oil and gas,” in Proc. SPIE 8961, Fiber Lasers XI: Technology, Systems, and Applications, 89610D, March 12, 2014. Brahmanand Upadhyaya, “CW Fibre Laser-part I and II,” Invited Talk, DAE-BRNS National Laser Symposium (NLS-24), Indore, India, Dec.2015. [5] [6] [7] [8] [9] [13] [14] Fig. 8(c) LD current pulse at 20 Hz, base value =17A, power value = 34A Fig. 8(f) Soft buildup of pulsed LD current at turn on. A Sharma, C.B Panwar, R. Arya, and A.K Nath, “Design of a high frequency SMPS powering laser diode,” Journal of Instrument Society of India , vol. 38, no.1, pp. 63-70, March 2008. Koli M.K et al., “QCW laser diode driver - pulsed current sources,” in DAE-BRNS National Laser Symposium (NLS-02), SCTIMST, Thiruvanathapuram, Nov. 2002, pp. 175-176. M.B. Borage, H.K.Khatwani and S.R. Tiwari, “A Versatile Driver for Laser Diodes,” in DAE-BRNS National Laser Symposium, (NLS-19), Indore, India, Dec. 2010. M.T. Thompson and M.F.Schlecht, “High Power Laser Diode Driver Based on Power Converter Topology,” IEEE Trans Power Electron., vol. 12, no. 1, pp. 46-51, Jan 1997. R.W. Erickson and D Maksimovic, “Fundamentals of Power Electronics,” 2nd edn., Springer (2001), Chapter 12, pp 439-473. Ridley Ray, “A new continuous time model for current mode control,” IEEE Trans. Power Electron., vol. 6, no. 2, Jan. 1991. Maksimovic et al, “Non-Linear Carrier Control for High Power Factor Boost Rectifiers,” in IEEE (APEC), 1995 . N. Kondrath and M.K.Kazimierczuk, “Control current and relative stabilty of peak current-mode controlled pulse-width modulated dc-dc converters without slope compensation,” IET Power electronics, vol. 3, Iss. 6, pp. 936-946. A.I. Zverev, “ Handbook of Filter Synthesis,” Wiley-Blackwell, Revised edn., 15 July 2005, Chapter 6. Datasheet available: <https://www.limo.de/content/dokument/pdf/produkte_losungen/diodenl asermodule/fasergekoppelte_diodenlaser/LIMO35-F200-DL806EX1658.pdf> Chin Chang and Eden Prairie, “Current ripple bounds in interleaved DCDC power converters,” in Proceedings of 1995 International Conference on Power Electronics and Drive Systems(PEDS 95). ICEPES 2016