Magnetic Core Solenoid Power Inductors for Voltage Regulators

advertisement

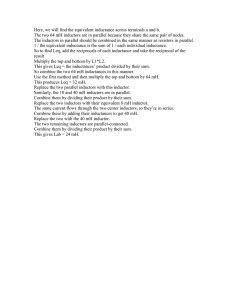

2682 IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS, VOL. 8, NO. 3, SEPTEMBER 2020 Magnetic Core Solenoid Power Inductors on Organic Substrate for System-in-Package Integrated High-Frequency Voltage Regulators Mohamed Lamine Fayçal Bellaredj , Anto Kavungal Davis , Paul Kohl , and Madhavan Swaminathan, Fellow, IEEE Abstract— In this paper, the design, modeling, fabrication, and characterization of System-in-Package (SiP) solenoid power inductor using a NiZn ferrite composite magnetic core material is demonstrated. A novel fabrication process has been developed for integrating the inductor into the buck-type integrated voltage regulator (IVR) module. The process uses stencil printing to deposit and pattern the magnetic core material. Photolithography and copper electroplating are used to form the windings. The electrical parameters of the fabricated inductors were extracted from measurements. The inductors had an average dc resistance of 19 m, average inductance of 28.3 nH, and average ac resistance of 2.28 at 100 MHz, which is the operating frequency of the IVR. The organic substrate parasitic effect led to an average shunt capacitance of 2.31 pF and an average parasitic conductance of 0.12 mS at 100 MHz. The 10% saturation current was 11.53 A. The electrical parameters of the fabricated inductors were modeled and showed good accuracy with measured data. The inductors showed an inductance to dc resistance ratio of 1613 nH/. The area and volume energy densities were 158.4 nJ/mm2 and 283.0 nJ/mm3 , respectively. These are the highest reported values for a solenoid magnetic core power inductor at 100 MHz. Index Terms— Energy densities, inductance to dc resistance ratio, integrated voltage regulators (IVRs), NiZn ferrite composite, package solenoid magnetic core power inductor, system-inpackage (SiP). I. I NTRODUCTION T HE need for miniaturized power conversion modules has motivated the development of integrated voltage regulators (IVR) [1] as a part of the power delivery network (PDN). Compared to conventional PDNs using multiple off-package voltage regulator modules (VRMs) with discrete passives Manuscript received November 27, 2018; revised March 2, 2019; accepted April 26, 2019. Date of publication April 30, 2019; date of current version August 4, 2020. This work was supported in part by the Power Delivery for Electronic Systems (PDES) Consortium, Georgia Tech and in part at the Georgia Tech Institute for Electronics and Nanotechnology, a member of the National Nanotechnology Coordinated Infrastructure, through the National Science Foundation under Grant ECCS-1542174. Recommended for publication by Associate Editor Paolo Mattavelli. (Corresponding author: Mohamed Lamine Fayçal Bellaredj.) The authors are with the Georgia Institute of Technology, Atlanta, GA 30332 USA (e-mail: mohamed.bellaredj@ece.gatech.edu; anto. kavungaldavis@ece.gatech.edu; kohl@gatech.edu; madhavan.swaminathan@ gatech.edu). Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org. Digital Object Identifier 10.1109/JESTPE.2019.2914215 [Fig. 1(a)], IVRs [either in package Fig. 1(b) or on-chip Fig. 1(c)] provide voltage regulation closer to the load, enabling miniaturization and modularity while reducing resistive losses due to shorter PDN interconnects, and enabling faster power management loops with better power integrity and savings. The system-in-package (SiP) IVRs [Fig. 1(b)] represent a cost-effective option allowing better modularity and thermal management compared to system-on-a-chip (SOC) IVRs [Fig. 1(c)] which achieve, however, better performances and integration densities when compared to SIP IVRs. The first IVRs used air core inductors [1]–[4] with operating frequencies from 80 [2] to 500 MHz [3] and load currents from 0.25 [3] to 30 A [1], [4] and showed low-inductance density [3] or large inductors with large cross-sectional windings [3], [4]. A smaller on-chip, 450-MHz, 0.18-A air core inductor with higher inductance density has been shown in [5] compared to that in [1], [4], [6], and [7]. However, the IVR peak efficiency was still relatively low due to the inductor ac losses. High peak power efficiency (93%) was predicted at 140-MHz switching frequency and 0.8-A load current [8] with a 3-D integrated fan-out (InFO) inductor using thick through-InFO-via (TIV) copper at the expense of a relatively small inductance density compared to [1], [4], [5], and [7]. These represent serious limitations for IVRs, which require the integration of low-loss and high-inductance-density power inductors. The use of lowloss magnetic core inductor with high switching frequency can increase inductance density and reduce inductor size for IVR integration. A 91.5% peak efficiency IVR (100 MHz, 0.15 A) was demonstrated in [9] with a surface mount technology (SMT) inductor. However, the commercial off-theshelf (COT) inductor approach restricts the IVR module design to chips with less flexibility in terms of size and interconnect length in order to minimize parasitic losses. A single-viawinding package embedded inductor using laminated senfoliage flake magnetic material (NEC/Token) was fabricated and used in a 20-MHz, 0.65-A 3-D IVR [10], [11]. Despite a simple inductor structure enabling multiphase integration with low dc resistance, the core showed a high loss density which should lead to low IVR efficiency. A ferromagnetic (FM) core (NiFe) racetrack spiral inductor was built on silicon interposer [12] with multiphase coupling for dc cancellation. However, the inductance density and the IVR efficiency at 2168-6777 © 2019 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information. Authorized licensed use limited to: UNIVERSITY COLLEGE CORK. Downloaded on May 18,2021 at 06:14:25 UTC from IEEE Xplore. Restrictions apply. BELLAREDJ et al.: MAGNETIC CORE SOLENOID POWER INDUCTORS ON ORGANIC SUBSTRATE Fig. 1. 2683 Voltage regulator architectures. (a) Discrete VRM with SOC load on PCB. (b) SiP IVR to SOC load on PCB. (c) SiP IVR with SOC load. 125-MHz and 3-A load current were relatively low due to the planar single windings topology of the racetrack inductor and the core losses when operated above a few megahertz. Solenoid inductors achieve a higher inductance density with reduced substrate parasitic losses compared to planar inductors due to confined parallel magnetic field lines to the substrate. Different processes have been developed for the fabrication of integrated magnetic core solenoid inductors. On silicon technology is the dominant technology in the past decades [13]–[15], as shown in Table I. On silicon FM magnetic core solenoid inductors using electroplated [16]–[18] or sputtered [19], FM thin film metal encased in polyimide [16], [20], air [17], or silicon oxide [19] insulation, and electroplated copper [16], gold [17], or sputtered aluminum [18] windings/vias have been reported. Despite high inductance densities, these inductors had high magnetic core losses at high frequency (>20 MHz) due to their low resistivity, which make them unsuitable for high-frequency high-efficiency IVRs. To suppress these losses, on silicon magnetic core solenoid inductors having laminated multilayer (LM) [21]–[31], nanogranular (NG) [34], [35], and ferrite [36], [37] magnetic cores deposited using sputtering [21]–[28], [34], [35], electroplating [29], electroplating/dip-coating [30], thermal evaporation/folding [31], manual filling [36], spin spraying [37], and enclosed in polyimide [24], [34], [35], [37], or SU-8 [23], [29], [30] insulated, electroplated copper [23], [24], [29], [30], [34]–[37], windings/vias or simply wire wound with a magnet wire [31] have been demonstrated. The NG inductors [34], [35] showed a higher inductance density at the expense of a lower Q compared to the LM inductors [21]– [31] while the ferrite inductors showed relatively similar characteristics at high frequency (100 MHz and beyond) to the LM inductors [21]–[30] while using simpler processes. However, the multiple depositions/laminations [21]–[30], stiction (due to copper sacrificial layers etching) [30], [31], failure risks due to high built-in stress/layers delamination between the dielectric/metallic layers [21]–[30], and manual placement/punching/wire wounding [29]–[31] increase the LM inductors process complexity. On-die solenoid inductors with single-lamination (SL) magnetic cores [32], [33] were used for 90–100 MHz, 0.025–0.365-A buck IVRs, and showed lower losses with higher inductance and current densities than the on-die spiral air core inductor [3]. However, the SL inductors showed low power density with very low saturation currents and IVR efficiencies of 84% and 80% due to dc losses in thin copper windings [32] and through silicon vias [33]. Similarly, the multiple sputtering steps associated with polyimide smoothness requirements [34], [35], the manual filling of the cavity [36] and the very low core deposition rate [37] limit the core thickness while increasing the NG and ferrite inductors process cost/time. Other limitations of on-silicon inductors include silicon wafers and processes cost, poor dielectric properties, and thin windings thickness (few microns) to comply with the CMOS metallization layers, which increases the dc resistance of the inductors, limiting the power density, and the IVR overall efficiency. Glass [38], [39] and ceramic [40], [41] dielectric substrates have been considered as alternatives to silicon for magnetic core solenoid inductors. On-glass inductors were fabricated using electroplated NiFe cores manually placed in [38] or wrapped with electroplated copper vias/windings, electrically insulated using a planarized polyimide layer [39]. The ceramic inductors [40], [41] were fabricated with low-temperature cofired ceramic (LTCC) technology with printed silver windings/vias inside a laminated ceramic stack enclosing a ferrite core. The glass inductors [38], [39] showed high inductance densities but poor Q factors due to high magnetic losses, while the LTCC inductors showed high Q factors at the expense of low inductance densities. However, the glass’s brittleness, coefficient of thermal expansion mismatch to silicon, and difficult processing as well as the high LTCC firing temperature and ceramic shrinkage pose serious challenges for the inductor and IVR integration. Compared to inorganic substrates, organic packages provide an option for inductor integration due to their lower cost, large area availability (stacking and lamination), low loss, and processing temperatures < 200 ◦ C. On-package NG core inductors [42] were fabricated by enclosing a sputtered NG film between the patterned bottom and electroplated top copper windings covered with an organic dielectric layer and interconnected with laser drilled copper vias. The inductors showed a relatively high Q due to reduced magnetic and substrate losses at the expense of a limited core thickness with a rough printed wiring board (PWB) surface, which degrades the core permeability. Bondwire inductors [43], [44] were built on-package by covering aluminum bondwires in a manually brushed MgZn composite [43], [44] or by assembling a laminated stack of Vitrovac 6155/dielectric tape and placing it between aluminum bondwires [45]. Although simple and relatively low cost, the process [43]–[45] is limited by the bondwire size, material (aluminum, gold) and inter-winding separation. Moreover, the hand-brushed core deposition [43], [44] lacks precision and can damage the bondwire windings. As an alternative approach, we showed [46]–[50] the advantages of a SiP solution using cooptimized chips and package magnetic core solenoid inductors with magnetic composite materials [48], [49] for implementing a high-efficiency IVR. In this work, a novel fabrication process Authorized licensed use limited to: UNIVERSITY COLLEGE CORK. Downloaded on May 18,2021 at 06:14:25 UTC from IEEE Xplore. Restrictions apply. 2684 IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS, VOL. 8, NO. 3, SEPTEMBER 2020 TABLE I M AGNETIC C ORE S OLENOID I NDUCTOR T ECHNOLOGIES (∗ E STIMATED F ROM THE P ROVIDED M ICROSCOPIC P ICTURES ; ∗∗ E STIMATED F ROM THE P ROVIDED W INDINGS W IDTH AND S EPARATION .) for package magnetic core solenoid power inductors is demonstrated for high-efficiency SiP IVRs based on design explorations [49], [50]. The process allows the deposition of a thick magnetic core at a high deposition rate compared to the FM [16], [20], LM [21]–[30] and NG [34], [35] cores, using a simple and cost-effective printing process. An organicsubstrate-compatible composite magnetic material [48], [49] was used for the magnetic core to allow very good adhesion to the substrate with low built-in stress at the core-substrate interface. The good dielectric properties of the composite material [48], [49], [51], [52] avoid the use of an insulation layer at the core-windings interface, which simplifies the process and reduces its overall cost and time. Moreover, the process takes advantage of the printed core shape to deposit the inductor’s top windings while simultaneously interconnecting them to the inductor’s bottom windings without the need for vertically patterned vias after successive planarization and photolithography steps [16], [18], [20]–[26], [29], [32]–[35], [37], [39]–[42]. This also simplifies the process compared to [16], [18], [20]–[26], [29], [32]–[35], [37], and [39]–[42] while lowering the dc resistance resulting from the contact resistance at the vias/windings interface. This paper is organized as follows. In Section II, the design/modeling procedure of the inductors is presented. In Section III, the fabrication process of the inductors is discussed in detail. The characterization results of the fabricated inductors are provided in Section IV and compared to simulation results. Finally, the fabricated induc- Fig. 2. Structure of the designed inductors (drawings not to scale). tors are compared with the state-of-the-art and commercially available magnetic core solenoid power inductors in Section V followed by conclusion in Section VI. II. D ESIGN AND M ODELING OF I NDUCTORS In [50], optimization of the architecture and inductors for a SiP IVR has been presented, based on the modeling approach presented in [53]. The optimization resulted in a four-phase buck IVR with 25-nH inductance per phase supporting a total current of 10 A for three conversion ratios, 5V/1V, 3.3V/1V, and 1.7V/1V. The IVR switching frequency was 100 MHz. In this section, the inductors were designed based on extensive modeling prior to fabrication. Fig. 2 shows a 3-D solenoid inductor with a magnetic core enclosed in copper windings, built on the top side of a two-copper-layer FR4 PWB with 70-μm-thick copper on each side to reduce the dc resistance and 500-μm-thick FR4 substrate. Authorized licensed use limited to: UNIVERSITY COLLEGE CORK. Downloaded on May 18,2021 at 06:14:25 UTC from IEEE Xplore. Restrictions apply. BELLAREDJ et al.: MAGNETIC CORE SOLENOID POWER INDUCTORS ON ORGANIC SUBSTRATE 2685 Fig. 3. Full-wave simulation of the inductor. (a) Electromagnetic properties of the NiZn ferrite magnetic composite material. (b) 3-D structure and lumped ports definition. (c) Simulated magnetic field (H -field) in the inductor cross section. The top copper layer of the PWB was used to define the bottom windings of the inductor which were covered with the magnetic core, along with the contact pads for the top copper windings. The bottom copper layer was used as a ground plane to reduce the electromagnetic interference (EMI) between the inductor and its surrounding. The magnetic core material was selected based on its electromagnetic properties and processability to allow the implementation and batch fabrication of power inductors on organic substrates. A NiZn ferrite epoxy composite magnetic material was chosen as the core material [48], [49] since it is a compatible organic substrate and can be deposited as a thick film using a low-cost printing process, which is suitable for high volume fabrication. The composite material showed good insulation properties combined with relatively high permeability and low electromagnetic losses at high frequency [48], [49]. Consequently, no insulation layer between the magnetic core and the copper windings [51], [52] was used for the inductor in this work as compared to the structure in [50]. Moreover, the dome-shaped magnetic core resulting from the stencil printing deposition process (Fig. 2) was also considered in the design instead of a rectangular core [50] by using experimentally measured core profiles in the simulations to accurately model the inductor. The design parameters of the inductors were the magnetic core size (thickness tmag_core , length lmag_core , and width Wmag_core ), the number N, and the width Wtrace of the copper windings, while the overall area A and the windings thicknesses (70 μm for both top tTop_copper and bottom tBottom_copper windings) were kept fixed. The inductors were designed for an inductance value of 25 nH. A 3-D model of the solenoid inductor of Fig. 2 was created in a full-wave simulator (Ansys Electronics Desktop ver. 2015.2) to account for the complex electromagnetic field distributions and loss effects in both the magnetic core (hysteresis and eddy current) and the copper windings (skin and proximity effects). The measured complex permeability and permittivity spectra of the NiZn ferrite magnetic material [48], [49], as shown in Fig. 3(a), were used in the solver to accurately represent the magnetic core. An example of a two-port simulated inductor is shown in Fig. 3(b) with the resulting magnetic field shown in Fig. 3(c) where the H -field in the inductor displays similar magnitudes in the magnetic core due to the moderate permeability of the magnetic composite material. The simulations were run from 10 MHz to 1 GHz. The material properties (at 100 MHz) used in the inductor simulations are summarized in Table II. The simulation results of TABLE II M ATERIALS P ROPERTIES ( AT 100 MHz) U SED I N THE I NDUCTOR S IMULATIONS the designed inductor were extracted as frequency-dependent two-port network parameters (S-parameters) and converted into a simple pi-equivalent circuit as shown in Fig. 4(a) where the series inductance L and resistance RAC represent the inductor’s effective inductance and resistance, respectively. The parallel conductance and capacitance represent the inductor’s parasitics originating from the organic substrate and the copper ground plane. A pi-topology is an acceptable representation of the inductor since the targeted switching frequency of the IVR (100 MHz) is below the first self-resonant frequency (SRF) of the inductor (>1 GHz), and consequently, the impedance is mainly inductive [48], [49]. The dc resistance RDC of the designed inductor was obtained using Ansys Maxwell ver.2015.2. The extracted inductor electrical parameters (RDC , L, RAC ) were used as inputs to evaluate the impact of the inductor on the overall IVR efficiency, following the same analytical approach described in [47], [50] which considers all major loss components from the buck chip, the passives (inductor and output capacitor) and PDN. Based on the overall IVR peak efficiencies (at maximum current load) evaluation, multiple cycles of simulation and modification of the inductor design parameters were carried out until the highest overall IVR efficiency was obtained for a given inductor geometry, with an inductance close to 25 nH. The inductor design approach is summarized in Fig. 4(a). Fig. 4(b) shows the efficiency evaluation (at maximum current load) obtained for the best inductor design as a function of the switching frequency of the buck converter for three voltage conversion ratios: 1.7: 1, 3:1, and 5:1. The efficiencies decrease from 93.38 %, 92.39%, and 84.55% at 10 MHz to 86.81 %, 86.28 %, and 68.44 % at 100 MHz for the 1.7:1, 3:1, and 5:1 conversions, respectively. Fig. 4(c) shows the efficiency versus load current at 100 MHz for the three conversion ratios. As can be seen in Fig. 4(c), the peak efficiencies at 100-MHz switching frequency are around 50 % load current condition and decrease by around 4 % at 100 % load condition (10-A load current). The 5V:1V Authorized licensed use limited to: UNIVERSITY COLLEGE CORK. Downloaded on May 18,2021 at 06:14:25 UTC from IEEE Xplore. Restrictions apply. 2686 IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS, VOL. 8, NO. 3, SEPTEMBER 2020 Fig. 4. Inductor design approach. (a) Simulation process flow. (b) IVR efficiency evaluation for 10-A current load. (c) IVR efficiency at 100-MHz versus load current. Fig. 5. Loss breakdown at 100 MHz. (a) 5:1 conversion (5 A, 0.48-W total loss, 72% peak efficiency). (b) 3:1 conversion (5 A, 0.16-W total loss, 88% peak efficiency). (c) 1.7:1 conversion (5 A, 0.13-W total loss, 89% peak efficiency). (d) 5:1 conversion (10 A, 1.18-W total loss, 68.44 % efficiency). (e) 3:1 conversion (10 A, 0.42-W total loss, 86.28 % efficiency). (f) 1.7:1 conversion (10 A, 0.41-W total loss, 86.81 % efficiency). TABLE III D IMENSIONAL P ROPERTIES AND M AIN F IGURES OF M ERIT ( AT 100 MHz) OF THE D ESIGNED I NDUCTOR efficiency drop is due to the high switching and conduction losses (3.5x higher than the 1.7:1V and 3V:1V conversion ratios) of the CMOS FETs (130-nm process from global foundries) as shown in Fig. 5 where the loss breakdown (at 100 MHz) at peak efficiency (around 5 A) and at maximum load condition (10 A) for the three conversion ratios is shown. At peak efficiency points [Fig. 5(a)–(c)], the FETs losses are almost balanced and represent between 74%–81% of the overall IVRs losses for the 1.7:1V and 3V:1V conversions and around 90% of the overall IVRs losses for a 5V:1V conversion. At 100 % load condition [Fig. 5(d) and (e)], the loss distribution is almost similar to the peak efficiency case (around 90% for 5V:1V and around 75 % for 1.7:1V and 3V:1V) with, however, more pronounced FETs conduction (compared to switching losses) and inductor dc losses, which is somehow expected due to a higher current condition (10 A). The extracted dc/RF parameters and the dimensions of the final inductor design are shown in Fig. 6 and Table III, respectively. The inductance decreases slightly with frequency and has a value of 27 nH at 100 MHz while the ac resistance increases significantly with frequency and has a value of 3.16 at 100 MHz. Below the maximum permeability point (MPP) of the magnetic material (around 20–30 MHz), the losses are mainly due to the copper windings. Above the MPP value, and especially around 100 MHz, the magnetic losses dominate the overall inductor losses as the magnetic material shows a slight decrease in the real part of the permeability (hence a decrease of the inductance) and an increase in the imaginary part of the permeability (hence the ac resistance increase) with frequency [48], [49]. The organic PWB substrates used for inductor fabrication were designed using Cadence Allegro and include patterns of the bottom copper windings connected to surface mount adaptors (SMA) pads with feedlines as well as process alignment marks (Fig. 7). Thru-reflect-line (TRL) deembedding structures were also included in the design for electrical characterization of the inductors. Authorized licensed use limited to: UNIVERSITY COLLEGE CORK. Downloaded on May 18,2021 at 06:14:25 UTC from IEEE Xplore. Restrictions apply. BELLAREDJ et al.: MAGNETIC CORE SOLENOID POWER INDUCTORS ON ORGANIC SUBSTRATE Fig. 6. 2687 Extracted RF parameters of the designed solenoid inductor. (a) Inductance. (b) AC resistance. (c) Parasitic capacitance. (d) Parasitic conductance. Fig. 7. Designed boards with (a) inductors’ bottom windings and (b) TRL deembedding structures. III. FABRICATION OF THE S OLENOID I NDUCTORS The fabrication process flow of the solenoid inductor is shown in Fig. 8. A 640-μm-thick, two-copper layer FR4 PWB (70-μm-thick copper on front and back, and 5000-μm-thick FR4 core) was used as a substrate Fig. 8(a). The substrate was cleaned thoroughly in acetone, IPA and DI water and the cleaning procedure was repeated after each fabrication step. First, the bottom inductor windings on the top side of the PWB were defined using standard PWB copper etching process Fig. 8(b). The copper traces width and separation were measured using an optical microscope and were found to be 450 and 225 μm, respectively, Fig. 9(a). The copper trace thickness was obtained using the Veeco Dektak 150 surface profilometer and found to be around 74 μm, Fig. 9(b). Then, the magnetic core was deposited on top of the bottom copper windings Fig. 8(c) by stencil printing using an MPM SPM 7279 semiautomatic stencil printer (PPM Inc) and a custom prepared FR4 compatible composite magnetic paste consisting of a Lica 38 activated magnetic powder (FP350 NiZn ferrite from pptechnology) mixed with bisphenol-A- diglycidyl ether (BPADGE) epoxy resin at 85 wt% [49]. The paste viscosity was tuned to ensure conformal deposition of the magnetic material and filling of the spaces between the bottom windings. After printing the magnetic layer, the substrate was cured for one hour at 180 ◦ C to form the magnetic core Fig. 9(c). The thermosetting resin used to form the composite magnetic material shrinks during the curing phase of the paste due to the epoxy’s molecules polymerization (crosslinking) process which results in the formation of a rigid magnetic core. However, this natural shrinkage process has no effect on the magnetic core. The use of BPADGE (bisphenol-Adiglycidyl ether) polymer [49] makes the composite magnetic material FR4- compatible, which reduces significantly the built-in stress at the core/organic substrate interface and results in a very strong adhesion of the magnetic composite to the organic substrate. The cured composite magnetic material was inert to common solvents such as acetone. The core had excellent adhesion to the substrate and good dielectric properties [49] assessed by a measured very high dc resistance (>30 M), which negated the need for an insulating layer between the magnetic core and the copper windings [51], [52]. The measured profile of the magnetic core is shown in Fig. 9(d), where the average measured core thickness is around 350 μm. After deposition of the core, a first photolithography step was used to pattern a seed layer on top of the magnetic core to obtain a conductive metallic surface for electroplating the top windings. A thick photoresist mold (>70 μm which is the bottom winding thickness) was used to ensure full coverage of the spaces between the bottom copper windings with photoresist. This also avoids the seed layer deposition on the sidewalls of the pads which could result in pads bridging (thus electrical shorts) after the top windings electroplating. Intervia 65a BPN photoresist was spray coated directly on the magnetic core and the bottom copper windings using a Suss DeltaAltaSpray spray coater. Spray coating was chosen so that excellent coverage of the 3-D topology of the magnetic core and bottom windings could be achieved in one step. The photoresist thickness was 100 μm [Fig. 9(e)] and no softbake was used to avoid air bubbles in the photoresist leading to microdefects. The photoresist was exposed using noncontact lithography (EVG 620 Mask aligner at 365-nm wavelength at an intensity of 5 mW/cm2 for 200 s). The photolithography masks were designed to account for pattern broadening resulting from noncontact exposure. The exposed photoresist was then developed in RD6 developer for 5 min, Fig. 8(d). The seed layer (50-nm chromium and 200-nm gold) was then sputtered at 5 mTorr using a Unifilm multisource sputtering system at a rate of 8.3 and 33 A/s, respectively, Fig. 8(e). A liftoff process [Fig. 8(f)] was used to pattern the seed layer and remove the photoresist, Fig. 9(f). A second photolithography step [Fig. 8(g)] was used to fabricate the photoresist mold for electroplating the top windings. A 170-um-thick Intervia 65a BPN photoresist was spray coated directly on top of the patterned seed layer and no softbake was used. A very thick mold was chosen to allow the deposition of very thick copper windings to reduce the dc resistance of the inductor. Non-contact lithography (EVG 620 mask aligner) was used to expose the photoresist at 365-nm wavelength at 5 mW/cm2 for 330 s. The exposed photoresist was developed in RD6 for 8 min. The top copper windings were electroplated [Fig. 8(h)] on the exposed seed layer shown in Fig. 8(g) since this was the only area in contact with the copper electroplating bath, which resulted in copper electrodeposition on the winding lines accurately. Authorized licensed use limited to: UNIVERSITY COLLEGE CORK. Downloaded on May 18,2021 at 06:14:25 UTC from IEEE Xplore. Restrictions apply. 2688 IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS, VOL. 8, NO. 3, SEPTEMBER 2020 Fig. 8. Fabrication process flow of the solenoid inductors. (a) Initial two-copper layer, FR4 PWB substrate. (b) PWB etching to define the bottom copper tracks. (c) Stencil printing of the NiZn ferrite magnetic core. (d) Photoresist deposition and patterning using photolithography. (e) Sputter deposition of a seed layer of 50 nm Cr + 200 nm Au. (f) Liftoff process to remove the photoresist and pattern the seed layer for the top windings electroplating. (g) Photoresist deposition and patterning using photolithography. (h) Electrodeposition of the top copper windings. (i) Removal of the photoresist. (j) Photoresist deposition and patterning using photolithography. (k) Seed layer and photoresist removal. Fig. 9. Fabrication process steps. (a) Optical view of the patterned bottom copper windings optical view. (b) Copper trace thickness (longitudinal scan). (c) Optical view of the printed magnetic core on top of the bottom copper windings. (d) Measured core profile (Lateral scan). (e) Photoresist mold for seed layer patterning. (f) Patterned seed layer after the liftoff process. (g) Optical view of the inductor after copper plating. (h) Optical view of the fabricated inductor. (i) Measured profile of the top copper windings. An acid copper bath (copper sulfate, sulfuric acid, and organic additives to improve the bath throwing power and the deposition uniformity) was used for the electroplating process. A pure copper bar was used as the anodic copper source and the electroplating was done at a current density of 10 mA/cm2 for 6 h [Fig. 9(g)]. The photoresist mold was removed after plating the top windings by immersion in acetone [Fig. 8(i)]. A third photolithography step was used to protect the plated top copper windings from the seed layer etching solutions. An 8-μm-thick AZ 4620 photoresist was spray coated on top of the inductor, softbaked for 2 min at 120 ◦ C, and exposed under the same exposure settings as before for 100 s. The photoresist was then developed in RD6 for 4 min[Fig. 8(j)]. The seed layer was removed using gold and chromium etching solutions (Sigma Aldrich) and finally, the AZ 4620 photoresist was removed in acetone [Fig. 8(k)]. An example of a fabricated inductor is shown in Fig. 9(h). The measured profile of the electroplated top copper windings is shown in Fig. 9(i), where 76.5-μm-thick copper was deposited on top of the magnetic core. IV. C HARACTERIZATION OF THE S OLENOID I NDUCTORS The dc resistance of the inductors was measured using the four-wire mode of the HP 34 401-A multimeter. The RF parameters of the inductors were characterized between 20 MHz and 1 GHz using an Agilent H8363B vector network Authorized licensed use limited to: UNIVERSITY COLLEGE CORK. Downloaded on May 18,2021 at 06:14:25 UTC from IEEE Xplore. Restrictions apply. BELLAREDJ et al.: MAGNETIC CORE SOLENOID POWER INDUCTORS ON ORGANIC SUBSTRATE 2689 Fig. 10. Extracted RF parameters for different inductors. (a) Inductance and (b) ac resistance for inductors fabricated on the same board. (c) Inductance, (d) ac resistance, (e) parasitic capacitance, and (f) parasitic conductance for inductors fabricated on different boards. analyzer. A standard SOLT calibration was carried out, followed by the measurement of the two-port S-parameters of the inductors and the TRL deembedding structures which were then mathematically postprocessed to remove the effect of the SMAs connectors and feedlines, allowing the extraction of the RF parameters. The dc saturation current was measured by coupling a dc current delivered by a dc power supply (P9611A-Picotest) to the ac voltage of the vector network analyzer through a bias tee (picotest). The effect of the bias tee connectors and feedlines was removed by measuring the S-parameters with and without the inductor, followed by deemebedding. The reproducibility of the fabrication process was demonstrated by the characterization of multiple inductors (from the same batch (on the same board) and from different batches (on different boards). The minimum average measured dc resistance of the inductors was 19 m. The extracted RF parameters of the inductors are shown in Fig. 10. Good reproducibility is observed for inductors fabricated on the same board with less than 1 % and 10 % variations (at 100 MHz) in inductance and ac resistance, respectively [Fig. 10(a) and (b)]. At 100 MHz, the fabricated inductors had an inductance of 25.6–31.0 nH (mean value of 28.3 nH) compared to the target 25-nH inductance. The average values for the ac resistance, parasitic capacitance, and parasitic conductance at 100 MHz were 2.28 , 2.31 pF, and 0.12 mS, respectively. The variation in values was mostly due to small differences in the magnetic core size (thickness and area) resulting from the stencil printing process. It is worth mentioning that the impedance of the average parasitic capacitance (2.31 pF) is more than 5e4 times higher than the buck output capacitor (100 nF) impedance, which is expected to reduce any parasitic oscillation induced between the inductor and the parasitic capacitor. Inductor fabrication reproducibility would be improved by better control of the magnetic composite paste viscosity and stencil printing conditions. For all the inductors (from 20 MHz to 1 GHz), the inductance decreased with frequency due to the permeability decrease of the NiZn ferrite composite above its MPP frequency [49] while the ac resistance increased due to magnetic core and RF (proximity and eddy current) losses at high frequency. At 100 MHz, inductor 1 (Ind 1, which is the closest to the average inductance value 28.64 nH) had an inductance of 27.1 nH, an ac resistance of 2.7 , an average parasitic capacitance (C1 /2 + C2 /2) of 1.3 pF, and an average conductance (G 1 /2 + G 2 /2) of 0.12 mS. The inductor models (Section II) were updated based on the measured dimensions of the fabricated inductors, Table IV and the simulation results were compared to the experimentally measured RF parameters (Fig. 11). A good match is observed between the experimental and modeling results with error values (at 100 MHz) less than 10 % for the inductance and parasitic capacitance C1 up to 1 GHz and 22 % for the for ac resistance up to around 300 MHz. The discrepancies observed for C2 , G 1 (although following the expected trend), G 2 and RAC (beyond 300 MHz) can be attributed to errors resulting from the deembedding process which was carried out using deembedding structures on a separate board. However, it is important to note that the resistance and inductance are the dominant parameters here with capacitance and conductance contributing to some losses. Moreover, the SRF of the inductor is beyond 1 GHz as can be seen in the extracted impedance plot shown in Fig. 11(e). This was also expected based on the design analysis of Section II. Therefore, the correlation between modeling and measurements is good at around 100 MHz. More accurate extracted RF parameters can be obtained if the deembedding structures are defined on the same board as the inductors since all the fabrication process steps affecting the board (both on the top and bottom ground plane) such as magnetic core curing, seed layer deposition/patterning/removal, and copper windings plating will be removed after deembedding. Moreover, the used pi-model assumed an ideal two-port inductor Authorized licensed use limited to: UNIVERSITY COLLEGE CORK. Downloaded on May 18,2021 at 06:14:25 UTC from IEEE Xplore. Restrictions apply. 2690 IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS, VOL. 8, NO. 3, SEPTEMBER 2020 TABLE IV U PDATED S IMULATION PARAMETERS BASED ON E XPERIMENTAL D ATA Fig. 11. Comparison of the measured and simulated (updated) inductor RF parameters. (a) Inductance. (b) AC resistance. (c) Parasitic capacitance. (d) Parasitic conductance. (e) Absolute value of impedance. model, which implies perfectly symmetric ports (thus C1 _sim = C2 _sim and G 1 _sim = G 2 _sim) while the fabricated inductors ports are not symmetric due to variations in the fabrication process and the deemebedding procedure which explains the differences observed between C2 -G2 and C2sim -G2sim . The effect of dc current on the inductance is shown in Fig. 12(a), where a 1.62-nH decrease is observed for 6 A at 100 MHz, which corresponds to a 5.2 % drop from the unbiased initial inductance value (Isat_5.2% ). The 10 % saturation current of the inductor (Isat_10% ) is estimated accordingly to be around 11.53 A, which is higher than the targeted maximum load current for the IVR (2.5 A/phase). The inductance decrease due to the dc current results in the decrease of the ac resistance as shown in Fig. 12(b), where a 16 % drop is observed for 6 A at 100 MHz. This can be attributed to a reduction of the effective core volume due to partial saturation. The saturated part does not contribute to the inductance and thus do not add to the inductor losses which explains the drops observed for both the inductance an ac resistance. A similar behavior has been reported in [54] for an FP 350 NiZn ferrite based composite magnetic material core. At 2.5 A, the ac resistance drop is estimated to be around 6.6 %. The effect of the ac peak current Ipk (up to 200-mA peak-to- peak) on the inductance and ac resistance is shown in Fig. 12(c) and (d), where both decrease slightly with the ac current increase to reach 1.4 % and 10 % drops around 100-mA peak ac current. This can be explained by a slight decrease of the relative permeability of the magnetic composite material with the increase of the ac current. While an increase of the B–H curve slope was expected (thus an increase of the relative permeability) due to large signal conditions, the increase of the imaginary part of the magnetic core permeability seems to be slightly higher than the increase of the real part of its permeability (due to higher magnetic core losses) which results in a reduction of the total relative permeability of the core and thus in a slight decrease of the inductance. A smaller inductance implies a lower magnetic flux density and thus less magnetic losses, which could explain the ac resistance drop. Equations (1) and (2) obtained by fitting the measured inductance and ac resistance data [Fig.12(c) and (d)] can be used to estimate the inductance and ac resistance at 100 MHz beyond 100-mA peak current L(nH) = a1 · e−b1 ·Ipk + c1 R() = a2 · e −(2(Ipk −b2 )/c2 ) (1) (2) where Ipk is given in milliamperes and a1 , b1 , c1 , a2 , b2 , and c2 are the fitting parameters given in Table VI. Based on the measured dc and ac large-signal excitation results, the combined effect of the dc and ac currents on the inductance, ac resistance, and the corresponding Q factor can then be estimated for the three voltage conversion ratios considered in this work as shown in Table V as follows. The dc current results in 2.16 % and 6.6 % drops of the initial inductance and ac resistance, respectively, while the ac current drops are estimated assuming IDC = 0, which implies L = 31.21 nH, RAC = 2.18 (initial inductor conditions), and thus, the initial ripple current values of the small signal conditions. For an initial ripple current of 129 mA (5V:1V conversion) and based on (1) and (2), the initial inductance and ac resistance drop Authorized licensed use limited to: UNIVERSITY COLLEGE CORK. Downloaded on May 18,2021 at 06:14:25 UTC from IEEE Xplore. Restrictions apply. BELLAREDJ et al.: MAGNETIC CORE SOLENOID POWER INDUCTORS ON ORGANIC SUBSTRATE 2691 Fig. 12. Large signal excitation of the inductors. (a) Inductance variation due to dc current. (b) AC resistance variation due to dc current. (c) Inductance variation due to ac current. (d) AC resistance variation due to dc current. Fig. 13. Loss breakdown at 100 MHz and 10-A load current (considering large signal measurement results) for (a) 5:1 conversion (1.16-W total loss, 68 % efficiency), (b) 3:1 conversion (0.41-W total loss, 85.73 % efficiency), and (c) 1.7:1 conversion (0.4-W total loss, 86 % efficiency). TABLE V F ITTING C OEFFICIENTS FOR (1)–(8) TABLE VI E STIMATED L ARGE S IGNAL RF PARAMETERS AT 100-MHz AND 2.5-A DC C URRENT by 3.3 % and 15.1 % respectively. The total inductance and ac resistance drops are thus 5.46 % and 21.7 %, which results in L = 29.5 nH, RAC = 1.7 , and a steady-state ripple current of 135 mA. As can be seen in Table V, at large signal conditions, a slight improvement is estimated for the inductor Q factor at the expense of a slightly higher ripple current resulting from the inductance drop. This trend is observed in the loss breakdown of the inductor where the FETs resistive losses increases slightly at the expense of the inductor’s ac losses compared to the loss breakdown shown in Fig. 14. The peak core loss Ppk per unit volume V, defined as the peak core loss density PV pk was estimated following the same approach presented in [55], by first extracting the core’s loss equivalent series resistance Rs under different sine wave excitations using the following equation: Rs = R AC − R0 (3) where RAC is the inductor‘s ac resistance and R0 is the ac resistance of the air core inductor of the same dimensions obtained from fenite elements method (FEM) simulations [Fig. 11(b)] and then applying the following equation: 2 Rs · Ipk Ppk = (4) V A e · Ie where Ipk is the ac current peak value, Ae is the effective magnetic cross section, and le is the mean magnetic length. The peak ac flux density is deduced from ac current using the following equation: PV pk = L s · Ipk N · Ae Ls = L − L0 Bpk = (5) (6) where L s represents the core’s equivalent inductance and L 0 is the inductance of the air core inductor of the same dimensions obtained from FEM simulations [Fig. 11(a)]. Fig. 13 shows the obtained core loss densities and the corresponding core losses at 30 and 100 MHz as a function of the peak ac flux density and the peak ac current, respectively. The core losses increase with the increase of the frequency and the ac current. At 1000-mA peak current (200-mA peak-to-peak), the core loss is 1.98 mW at 30 MHz and 18.89 mW at 100 MHz. As can Authorized licensed use limited to: UNIVERSITY COLLEGE CORK. Downloaded on May 18,2021 at 06:14:25 UTC from IEEE Xplore. Restrictions apply. 2692 IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS, VOL. 8, NO. 3, SEPTEMBER 2020 Fig. 14. Peak core loss density evaluation. (a) Peak core loss density versus peak ac flux density. (b) Peak core loss and the corresponding peak core loss density variation with peak ac current. (c) Core loss density variation with frequency and curve fitting using Steinmetz equation. be seen in Fig. 13(a) and (b), a simple quadratic polynomial equation can be used to fit the core loss density (in mW/cm3 ) as a function of the applied peak ac current (in mA) (or peak flux density): 2 PV pk = p1 · Ipk + p2 · Ipk + p3 (7) where p1 , p2 , and p3 are the fitting parameters provided in Table VI. Fig. 13(c) shows the extracted loss densities as a function of the frequency f and the corresponding fit curves using Steinmetz equation β PV pk = K · f α · Bpk (8) where K , α, and β are the fitting coefficients given in Table VI. Table V includes also the extracted loss densities using (7) and (8) for three peak ac currents, corresponding to the ripple currents for 5/3/1.7 to 1 V conversion ratios. As can be seen in Table V, (7) and (8) provide the close estimations of the core losses and can be used to evaluate the core loss for a given ac current frequency. The effect of the large signal conditions on the loss breakdown (at 100 MHz) at maximum load condition (10 A) for the three conversion ratios is shown in Fig. 14. Compared to Fig. 5 where small signal conditions were considered, the FETs losses increase (for the three voltage conversions) due to the ripple current increase while the inductor ac losses decrease due to the combined effects of the dc and ac currents on the inductor. V. C OMPARISON TO P REVIOUS W ORK Inductors are generally compared and selected based on the targeted application and their specific figures-of-merit related to both size and dc–RF characteristics such as dc resistance, inductance density, and quality factor. For integrated power inductors, both the effect of the inductor’s size and power handling capabilities need to be captured. This can be achieved by considering the energy density factors [29] 2 L ∗ Isat (9) 2∗ A 2 L ∗ Isat (10) E dV = 2∗V In (9) and (10), the combined effects of the inductance, saturation current and size (area and volume) are considered simultaneously. Based on these energy density factors, different power inductor technologies reported in the literature, as well as commercially available inductors, are compared to Ed A = Fig. 15. Basic dimensional representation of the targeted SiP IVR with the integrated solenoid inductors. the inductors fabricated in this work at 100 MHz and below, in Tables VII and VIII, respectively. The inductors demonstrated in this work show a low dc resistance with the highest reported inductance-to-dc resistance ratio (1613.57 nH/m), area (158.38 nJ/mm2 ), and volume (283.04 nJ/mm3 ) energy densities for a magnetic core power inductor at 100 MHz compared with the state-of-the-art and commercially available inductors with similar inductance values. The low dc resistance reduces the ohmic losses and increases the IVR overall efficiency, while the high energy densities allow the implementation of high-power-density SIP-based IVRs. A basic dimensional representation of the targeted two-chip SiP IVR architecture is shown in Fig. 15. The IVR provides 1-V output (from the direct down conversion of three input voltages 5/3/1.7) at 100 MHz to a load chip containing an low dropout (LDO) which employs asynchronous nonlinear control to achieve fast voltage drop mitigation under large load-transient events [56]. The inductors will be fabricated using the process developed in this work on the top surface while considering space limitations (package size), the surrounding routing traces and chips (buck converter and LDO with test load) pins. Having the inductors on the surface provides thermal insulation with limited coupling through cooptimized components placement with sufficient spacing between inductors and chips for heat reduction [47]. Package routing will be done using the copper layer of the first level package as well as through the underneath package layers. The module area was set to be relatively large to allow enough room for routing and testing for the first prototype that is being fabricated. For the initial demonstration of the SIP IVR module, cheap surface mount device (SMD) capacitors of 100 nF will be placed on the top surface of the module for buck converter output filtering. Based on our previous work Authorized licensed use limited to: UNIVERSITY COLLEGE CORK. Downloaded on May 18,2021 at 06:14:25 UTC from IEEE Xplore. Restrictions apply. BELLAREDJ et al.: MAGNETIC CORE SOLENOID POWER INDUCTORS ON ORGANIC SUBSTRATE 2693 TABLE VII C OMPARISON W ITH S TATE OF THE A RT OF FABRICATED M AGNETIC C ORE S OLENOID I NDUCTORS TABLE VIII C OMPARISON W ITH THE FABRICATED I NDUCTOR TO C OMMERCIAL I NDUCTORS (AT 100 MHz F REQUENCY ) [57], a PDN employing power transmission lines (PTL) [57] and properly selected SMD decoupling capacitors, according to target impedance requirements will be used between the buck and the LDO to minimize power supply noise (PSN) and coupling between signal and PDN in the package, thereby enhancing the bandwidth while reducing package impedance (thus voltage droop) to achieve optimum efficiency. It is worth mentioning that because the complexity of the IVR module, each element have/is been/being studied separately to fully assess its performance before building the full IVR, which shows the degree of flexibility/modularity that can be achieved with a SIP based IVR solution. VI. C ONCLUSION A SIP-based IVR represents a valuable approach to achieve combined high integration density and efficiency for point-of-load voltage regulation. In this work, a novel SiP magnetic core solenoid power inductor was demonstrated for the implementation of a high efficiency, 100-MHz switching buck-type IVR. The optimum inductor design linked to the IVR specifications and process node, was developed based on the highest achievable overall IVR efficiency while considering all major loss components, which include conduction and switching losses from the switches for a 130-nm CMOS process, passives (inductor and output capacitor), and PDN losses. The inductor was fabricated on an organic substrate using printing and noncontact lithography processes, which makes the technology cost-effective and batch fabrication compatible. A pi-equivalent circuit and standard TRL deembedding were used for the inductor characterization and a good match was obtained with the modeling results. The inductor showed the highest reported inductance-to-dc resistance ratio and area/volume energy densities for a magnetic core inductor of the same inductance at 100 MHz. The developed fabrication process will be used for the integration of the magnetic core solenoid power inductors in both single phase and four Authorized licensed use limited to: UNIVERSITY COLLEGE CORK. Downloaded on May 18,2021 at 06:14:25 UTC from IEEE Xplore. Restrictions apply. 2694 IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS, VOL. 8, NO. 3, SEPTEMBER 2020 phase SIP-based IVRs allowing three voltage conversion ratios (5:1, 3:1, and 1.7:1). The use of a higher resistivity NiZn ferrite powder such as FA100 (×100 compared to FP350) will improve the inductor’s Q factor by reducing the core losses at high frequency. A tradeoff between the dc and ac resistance losses can be found to shrink the inductor size while keeping the same inductance range by increasing the windings number. By reducing the inductor footprint, better control on the core printing conditions is expected (low magnetic paste spreading after printing due to a smaller core size) which should improve the repeatability of the fabrication process. The inductor process demonstrated in this work can lay the foundations for the development of next-generation SiP heterogeneous integration technologies, where the power inductors are integrated and interconnected with multitechnology (Si, GaAs, GaN, etc.) chips with different optimized specific functions such as dc–dc converters, logic and memory, antennas arrays, etc., in a single package using PTLs and redistribution layers (RDLs) to implement ultraefficient fabrics such as GaN FET-based converters with integrated magnetics. R EFERENCES [1] E. A. Burton et al., “FIVR—FIVR Fully integrated voltage regulators on 4th generation intel core SoCs,” in Proc. IEEE Appl. Power Electron. Conf. Expo.-(APEC), Mar. 2014, pp. 432–439. [2] N. Sturcken et al., “A switched-inductor integrated voltage regulator with nonlinear feedback and network-on-chip load in 45 nm SOI,” IEEE J. Solid-State Circuits, vol. 47, no. 8, pp. 1935–1945, Aug. 2012. [3] H. Krishnamurthy et al., “A 500 MHz, 68% efficient, fully on-die digitally controlled buck voltage regulator on 22 nm tri-gate CMOS,” in Symp. VLSI Circuits Dig. Tech. Papers, Jun. 2014, pp. 1–2. [4] W. J. Lambert, M. J. Hill, K. Radhakrishnan, L. Wojewoda, and A. E. Augustine, “Package embedded inductors for integrated voltage regulators,” in Proc. IEEE 64th Electron. Compon. Technol. Conf. (ECTC), May 2014, pp. 528–534. [5] N. Tang et al., “Fully integrated buck converter with fourth-order lowpass filter,” IEEE Trans. Power Electron., vol. 32, no. 5, pp. 3700–3707, May 2017. [6] W. J. Lambert, M. J. Hill, K. Radhakrishnan, L. Wojewoda, and A. E. Augustine, “Package inductors for Intel fully integrated voltage regulators,” IEEE Trans. Compon., Packag. Manuf. Technol., vol. 6, no. 1, pp. 3–11, Jan. 2016. [7] K. Bharath and S. Venkataraman, “Power delivery design and analysis of 14 nm multicore server CPUs with integrated voltage regulators,” in Proc. IEEE 66th Electron. Compon. Technol. Conf. (ECTC), May/Jun. 2016, pp. 368–373. [8] C.-L. Chen et al., “Ultra-low-resistance 3D InFO inductors for integrated voltage regulator applications,” in IEDM Tech. Dig., Dec. 2016, pp. 35.2.1–35.2.4. [9] F. Neveu, B. Allard, C. Martin, P. Bevilacqua, and F. Voiron, “A 100 MHz 91.5% peak efficiency integrated buck converter with a three-MOSFET cascode bridge,” IEEE Trans. Power Electron., vol. 31, no. 6, pp. 3985–3988, Jun. 2016. [10] D. Hou, F. C. Lee, and Q. Li, “Very high frequency IVR for small portable electronics with high-current multiphase 3-D integrated magnetics,” IEEE Trans. Power Electron., vol. 32, no. 11, pp. 8705–8717, Nov. 2017. [11] Y. Su, W. Zhang, Q. Li, F. C. Lee, and M. Mu, “High frequency integrated point of load (POL) module with PCB embedded inductor substrate,” in Proc. ECCE, Sep. 2013, pp. 1243–1250. [12] N. Sturcken et al., “A 2.5 D integrated voltage regulator using coupledmagnetic-core inductors on silicon interposer,” IEEE J. Solid-State Circuits, vol. 48, no. 1, pp. 244–254, Jan. 2013. [13] C. Ó Mathúna, T. O’Donnell, N. Wang, and K. Rinne, “Magnetics on silicon: An enabling technology for power supply on chip,” IEEE Trans. Power Electron., vol. 20, no. 3, pp. 585–592, May 2005. [14] C. Ó Mathúna, N. Wang, S. Kulkarni, and S. Roy, “Review of integrated magnetics for power supply on chip (PwrSoC),” IEEE Trans. Power Electron., vol. 27, no. 11, pp. 4799–4816, Nov. 2012. [15] C. R. Sullivan, D. V. Harburg, J. Qiu, C. G. Levey, and D. Yao, “Integrating magnetics for on-chip power: A perspective,” IEEE Trans. Power Electron., vol. 28, no. 9, pp. 4342–4353, Sep. 2013. [16] C. H. Ahn, Y. J. Kim, and M. G. Allen, “A fully integrated planar toroidal inductor with a micromachined nickel-iron magnetic bar,” IEEE Trans. Compon., Packag., Manuf. Technol., vol. 17, no. 3, pp. 463–469, Sep. 1994. [17] B. Löchel, A. Maciossek, M. Rothe, and W. Windbracke, “Microcoils fabricated by UV depth lithography and galvanoplating,” Sens. Actuators A, Phys., vol. 54, nos. 1–3, pp. 663–668, Jun. 1996. [18] Y. Zhuang, M. Vroubel, B. Rejaei, and J. N. Burghartz, “Integrated RF inductors with micro-patterned NiFe core,” Solid-State Electron., vol. 51, no. 3, pp. 405–413, Mar. 2007. [19] Y. Zhuang, B. Rejaei, E. Boellaard, M. Vroubel, and J. N. Burghartz, “Integrated solenoid inductors with patterned, sputter-deposited Cr/Fe10 Co90 /Cr ferromagnetic cores,” IEEE Electron Device Lett., vol. 24, no. 4, pp. 224–226, Apr. 2003. [20] D. W. Lee, K.-P. Hwang, and S. X. Wang, “Fabrication and analysis of high-performance integrated solenoid inductor with magnetic core,” IEEE Trans. Magn., vol. 44, no. 11, pp. 4089–4095, Nov. 2008. [21] X. Xing, N. X. Sun, and B. Chen, “High-bandwidth low-insertion loss solenoid transformers using FeCoB multilayers,” IEEE Trans. Power Electron., vol. 28, no. 9, pp. 4395–4401, Sep. 2013. [22] Y. Gao et al., “Significantly enhanced inductance and quality factor of GHz integrated magnetic solenoid inductors with FeGaB/Al2 O3 multilayer films,” IEEE Trans. Electron Devices, vol. 61, no. 5, pp. 1470–1476, May 2014. [23] A. El-Ghazaly, R. M. White, and S. X. Wang, “Gigahertz-band integrated magnetic inductors,” IEEE Trans. Microw. Theory Techn., vol. 65, no. 12, pp. 4893–4900, Dec. 2017. [24] M. A. Arasu et al., “Thin-film magnetic inductor for integrated power management,” in Proc. IEEE 67th Electron. Compon. Technol. Conf. (ECTC), Orlando, FL, USA, May/Jun. 2017, pp. 1485–1490. [25] N. Wang et al., “High-Q magnetic inductors for high efficiency on-chip power conversion,” in IEDM Tech. Dig., Dec. . 2017, pp. 35.3.1–35.3.4. [26] R. P. Davies, C. Cheng, N. Sturcken, W. E. Bailey, and K. L. Shepard, “Coupled inductors with crossed anisotropy CoZrTa/SiO2 multilayer cores,” IEEE Trans. Magn., vol. 49, no. 7, pp. 4009–4012, Jul. 2013. [27] N. Sturcken et al., “Magnetic thin-film inductors for monolithic integration with CMOS,” in IEDM Tech. Dig., Dec. 2015, pp. 11.4.1–11.4.4. [28] N. Sturcken, “Thin film inductors for integrated power conversion,” in Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC), Tampa, FL, USA, 2017, pp. 1–31. [29] J. Kim, M. Kim, J.-K. Kim, F. Herrault, and M. G. Allen, “Anisotropic nanolaminated CoNiFe cores integrated into microinductors for highfrequency DC–DC power conversion,” J. Phys. D, Appl. Phys., vol. 48, Oct. 2015, Art. no. 462001. [30] M. Kim, M. G. Allen, and J. Kim, “Nanolaminated CoNiFe cores with dip-coated fluoroacrylic polymer interlamination insulation: Fabrication, electrical characterization, and performance reliability,” in Proc. IEEE 67th Electron. Compon. Technol. Conf. (ECTC), Orlando, FL, USA, May/Jun. 2017, pp. 798–803. [31] J. Kim, “Fabrication of highly-nanolaminated metal inductor core by pressing and punching,” in Proc. 12th IEEE Int. Conf. Nano/Micro Eng. Mol. Syst., Los Angeles, CA, USA, Apr. 2017, pp. 661–664. [32] H. K. Krishnamurthy et al., “A digitally controlled fully integrated voltage regulator with on-die solenoid inductor with planar magnetic core in 14 nm tri-gate CMOS,” in ISSCC Dig. Tech. Papers, San Francisco, CA, USA, Feb. 2017, pp. 336–338. [33] H. K. Krishnamurthy et al., “A digitally controlled fully integrated voltage regulator with 3-D-TSV-based on-die solenoid inductor with a planar magnetic core for 3-D-stacked die applications in 14-nm Tri-gate CMOS,” IEEE J. Solid-State Circuits, vol. 53, no. 4, pp. 1038–1048, Apr. 2018. [34] L. Wang et al., “Integrated on-chip solenoid inductors with nanogranular magnetic cores,” IEEE Trans. Magn., vol. 52, no. 7, Jul. 2016, Art. no. 8400604. [35] Y. He, L. Wang, Y. Wang, H. Zhang, D. Peng, and F. Bai, “Coupled and decoupled on-chip solenoid inductors with nanogranular magnetic cores,” Solid-State Electron., vol. 138, pp. 51–55, Jul. 2017. [36] C. Yang et al., “Ferrite-integrated on-chip RF solenoid inductor,” in Proc. IEEE Sensors, Oct. 2008, pp. 1040–1043. Authorized licensed use limited to: UNIVERSITY COLLEGE CORK. Downloaded on May 18,2021 at 06:14:25 UTC from IEEE Xplore. Restrictions apply. BELLAREDJ et al.: MAGNETIC CORE SOLENOID POWER INDUCTORS ON ORGANIC SUBSTRATE [37] X. Wang et al., “A novel NiZn ferrite integrated magnetic solenoid inductor with a high quality factor at 0.7–6 GHz,” AIP Adv., vol. 7, no. 5, 2017, Art. no. 056606. [38] H. Lu, D. Flynn, C. Bailey, and M. Desmulliez, “An analysis of a microfabricated solenoid inductor,” in Proc. IEEE Electron. Syst. Integr. Technol. Conf. (ESTC) Dresden, Germany, Sep. 2006, pp. 556–561. [39] X.-Y. Gao, Y. Cao, Y. Zhou, W. Ding, C. Lei, and J.-A. Chen, “Fabrication of solenoid-type inductor with electroplated NiFe magnetic core,” J. Magn. Magn. Mater., vol. 305, no. 1, pp. 207–211, 2006. [40] A. Marić, N. Blaž, L. Živanov, and G. Radosavljević, “Fine tuning of 3D LTCC inductor properties using combination of different ferrite and dielectric tapes,” Int. J. Appl. Ceram. Technol., vol. 12, no. 5, pp. 1034–1044, Sep./Oct. 2015. [41] A. Marić, G. Radosavljević, N. Blaž, and L. Živanov, “Influence of fabrication parameters on performance of LTCC ferrite core solenoid inductor,” in Proc. 40th Int. Spring Seminar Electron. Technol. (ISSE), May 2017, pp. 1–6. [42] L. Li et al., “Small-resistance and high-quality-factor magnetic integrated inductors on PCB,” IEEE Trans. Adv. Packag., vol. 32, no. 4, pp. 780–787, Nov. 2009. [43] J. Lu, H. Jia, X. Wang, K. Padmanabhan, W. G. Hurley, and Z. J. Shen, “Modeling, design, and characterization of multiturn bondwire inductors with ferrite epoxy glob cores for power supply system-on-chip or system-in-package applications,” IEEE Trans. Power Electron., vol. 25, no. 8, pp. 2010–2017, Aug. 2010. [44] H. Jia, J. Lu, X. Wang, K. Padmanabhan, and Z. J. Shen, “Integration of a monolithic buck converter power IC and bondwire inductors with ferrite epoxy glob cores,” IEEE Trans. Power Electron., vol. 26, no. 6, pp. 1627–1630, Jun. 2011. [45] S. Kulkarni, D. Li, D. Jordan, N. Wang, and C. ÓMathuna, “PCB embedded bondwire inductors with discrete thin-film magnetic core for power supply in package,” IEEE J. Emerg. Sel. Topics Power Electron., vol. 6, no. 2, pp. 614–620, Jun. 2018. [46] S. Mueller et al., “Design of high efficiency integrated voltage regulators with embedded magnetic core inductors,” in Proc. IEEE 66th Electron. Compon. Technol. Conf., May 2016, pp. 566–573. [47] S. Mueller et al., “Modeling and design of system-in-package integrated voltage regulator with thermal effects,” in Proc. IEEE 25th Conf. Elect. Perform. Electron. Packag. Syst. (EPEPS), Oct. 2016, pp. 65–68. [48] M. L. F. Bellaredj, S. Mueller, A. K. Davis, P. Kohl, M. Swaminathan, and Y. Mano, “Fabrication, characterization and comparison of FR4compatible composite magnetic materials for high efficiency integrated voltage regulators with embedded magnetic core micro-inductors,” in Proc. IEEE 67th Electron. Compon. Technol. Conf. (ECTC), Orlando, FL, USA, May/Jun. 2017, pp. 2008–2014. [49] M. L. F. Bellaredj, S. Mueller, A. K. Davis, Y. Mano, P. A. Kohl, and M. Swaminathan, “Fabrication, characterization and comparison of composite magnetic materials for high efficiency integrated voltage regulators with embedded magnetic core micro-inductors,” J. Phys. D, Appl. Phys., vol. 50, Oct. 2017, Art. no. 455001. [50] S. Müller, M. L. F. Bellaredj, A. K. Davis, P. A. Kohl, and M. SwamiXnathan, “Design exploration of package-embedded inductors for high-efficiency integrated voltage regulators,” IEEE Trans. Compon., Packag. Manuf. Technol., vol. 9, no. 1, pp. 96–106, Jan. 2019. doi: 10.1109/TCPMT.2018.2856882. [51] M. L. F. Bellaredj, C. A. Pardue, P. A. Kohl, and M. Swaminathan, “Fabrication of package embedded spiral inductors with two magnetic layers for flexible SIP point of load converters in Internet of Everything devices,” Microelectron. Eng., vol. 189, pp. 18–27, Apr. 2018. [52] C. A. Pardue et al., “Design and Characterization of Inductors for SelfPowered IoT Edge Devices,” IEEE Trans. Compon., Packag. Manuf. Technol., vol. 8, no. 7, pp. 1263–1271, Jul. 2018. [53] V. Kursun, S. G. Narendra, V. K. De, and E. G. Friedman, “Efficiency analysis of a high frequency buck converter for on-chip integration with a dual-V D D microprocessor,” in Proc. 28th Eur. Solid-State Circuits Conf. (ESSCIRC), Sep. 2002, pp. 743–746. [54] H. T. Le et al., “High-QThree-dimensional microfabricated magneticcore toroidal inductors for power supplies in package,” IEEE Trans. Power Electron., vol. 34, no. 1, pp. 74–85, Jan. 2019. [55] Y. M. Nguyen et al., “Soft ferrite cores characterization for integrated micro-inductors,” J. Micromech. Microeng., vol. 24, Sep. 2014, Art. no. 104003. [56] S. B. Nasir et al., “A 65 nm, 1.15–0.15 V, 99.99% current-efficient digital low dropout regulator with asynchronous non-linear control for droop mitigation,” in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), May 2018, pp. 1–5. doi: 10.1109/ISCAS.2018.8351653. 2695 [57] D. C. Zhang, M. Swaminathan, A. Raychowdhury, and D. Keezer, “Enhancing the bandwidth of low-dropoutregulators using power transmissionlines for high-speed I/Os,” IEEE Trans. Compon., Packag. Manuf. Technol., vol. 7, no. 4, Apr. 2017, pp. 533–543. Mohamed Lamine Fayçal Bellaredj received the Engineering degree “diplome d’ingenieur” in electronics and the Magister degree in physics from the University of Sciences and Technologies of Oran (USTO), Bir El Djir, Algeria, in 2005 and 2007, respectively, and the Ph.D. degree in microengineering from the University of Franche-Comté, Besançon, France, in 2013. His current research interests include embedded passives engineering for RF, digital, and power electronics, flexible hybrid electronics (FHE), microengineering/nanoengineering, MEMS/NEMS modeling, fabrication and characterization, physics and technology of semiconductor devices, and third-generation solar cells. Anto Kavungal Davis received the B.Tech. degree in electrical and electronics engineering from the National Institute of Technology Tiruchirappalli, Tiruchirappalli, India, in 2006, and the M.Tech. and Ph.D. degrees both in electronics design from the Indian Institute of Science, Bangalore, India, in 2010 and 2015, respectively. From 2006 to 2007, he was with Huawei Technologies, Bangalore, India. In 2011, he was with Brocade Communications, Mumbai, India. His current research interests include electromagnetic compatibility, power integrity, switched capacitor converters, switched inductor converters, wireless power transfer, and Internet of Things. Paul Kohl received the B.S. degree in chemistry from the Bethany College, Lindsborg, KS, USA in 1974 and the Ph.D. degree in chemistry from The University of Texas at Austin, Austin, TX, USA. From 1978 to 1989, he was with the AT&T Bell Laboratories, Murray Hill, NJ, USA. In 1989, he joined the School of Chemical and Biomolecular Engineering, Georgia Institute of Technology, Atlanta, GA, USA, as a Faculty Member, where he is currently a Regents’ Professor and the Thomas L. Gossage/Hercules Inc. Chair. His current research interests include energy storage and conversion, and new materials and processes for advanced electronic devices Dr. Kohl is the President of The Electrochemical Society. He served as the Editor for Journal of The Electrochemical Society and as the Founding Editor for Electrochemical and Solid-State Letters. Madhavan Swaminathan (M’95–SM’98–F’06) received the M.S. and Ph.D. degrees in electrical engineering from Syracuse University, Syracuse, NY, USA, in 1989 and 1991, respectively. He was with IBM, East Fishkill, NY, USA where he was involved in packaging for supercomputers. He was the Joseph M. Pettit Professor in electronics with the School of Electrical and Computer Engineering (ECE) and the Deputy Director of the NSF Microsystems Packaging Research Center, Georgia Institute of Technology, Atlanta, GA, USA, where he is currently the John Pippin Chair Professor in microsystems packaging and electromagnetics with the School of ECE and the Director of the Center for Co-Design of Chip, Packages, and System. He is also the Founder and the Co-Founder of two startup companies, E-System Design, Savannah, GA, USA, and Jacket Micro Devices, Atlanta, GA, USA. He has authored more than 450 refereed technical publications, and is the primary author and a coeditor of 3 books. He holds 29 patents. He has served as the Distinguished Lecturer for the IEEE EMC Society. He is the Founder of the IEEE Conference Electrical Design of Advanced Packaging and Systems, a premier conference sponsored by the CPMT Society on Signal Integrity in the Asian region. Authorized licensed use limited to: UNIVERSITY COLLEGE CORK. Downloaded on May 18,2021 at 06:14:25 UTC from IEEE Xplore. Restrictions apply.