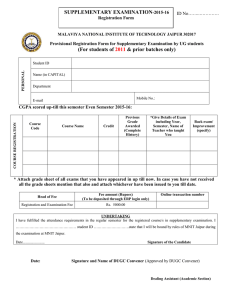

Arjun Singh Chauhan (Ph.D. Pursuing) Q Ó 7 ° arjunsingharyan@gmail.com, 2015REC9055@mnit.ac.in +91-9785324861 29, Shekhawati Nagar, Road No - 14, VKIA, Jaipur, 302013 @arjunsingharyan http://linkedin.com/in/arjunsinghchauhan/ Employment History 2011 -- 2013 Lecturer. Jaipur Institute of Engineering & Technology, Kukas, Jaipur. Education 2015 -- 2019 Ph.D.: Malaviya National Institute of Technology, Jaipur in Hardware Security. Thesis title: Security in Hardware for Internet of The Things Devices. The work is based on Physical Unclonable Functions (PUF) to provide secure device authentication and reliable cryptographic key generation from hardware (FPGA/ASIC). Supervisor: Dr. Vineet Sahula (Professor, ECE, MNIT, Jaipur) Joint Supervisor: Dr. Atanendu Sekhar Mandal (Chief Scientist, CEERI, Pilani) CGPA: 8.75 2013 -- 2015 M.Tech. VLSI Design: Malaviya National Institute of Technology, Jaipur Thesis title: Probabilistic Modeling approach for Impulse Noise Removal and Image Segmentation. Supervisor: Dr. Vineet Sahula (Professor, ECE, MNIT, Jaipur) CGPA: 8.67 2006 -- 2010 B.Tech. (Hons): Electronics Instrumentation & Control Engineering, Arya College of Engineering & Information Technology, Jaipur. Percentage: 70.81 2005 -- 2006 XII (Higher Secondary Examination): School, Alwar. Percentage: 58.62 2003 -- 2004 X (Secondary Examination): Bal Bharti Senior Secondary School, Alwar. Percentage: 77.33 Ramanand Senior Secondary Skills Coding Operating Systems HDL Databases Writing Hardware Design Tools C, C++, J A V A, M A T L AB. L I N U X, W I N D O W S. V H DL, V E R I L OG, S YS T E M V E R I L OG. MyS Q L. LATEX, Microsoft Office V I VA D O, I S E, Q U E S T A - S I M and S Y N O P SYS. Research Publications Journal Articles 1 Arjun Singh Chauhan, Vineet Sahula, & Atanendu Sekhar Mandal. (2019). Equipartitioning frequency groups & randomized placement for enhanced uniqueness and robustness in an FPGA-ROPUF based random sequence generator. ACM Transaction on Reconfigurable Technology and Systems (TRETS) [Submitted]. Conference Proceedings 1 Arjun Singh Chauhan, Vineet Sahula, & A. S. Mandal. (2019, January). Novel randomized & biased placement for FPGA based robust random number generator with enhanced uniqueness. In 2019 32nd international conference on VLSI Design and 2019 18th international conference on Embedded Systems (VLSID). 2 Arjun Singh Chauhan, Vineet Sahula, & A. S. Mandal. (2018, March). Novel placement bias for realizing highly reliable physical unclonable functions on FPGA. In 2018 ieee international conference on electronics, computing and communication technologies (conecct) (pp. 1–6). doi:10.1109/CONECCT.2018.8482381 3 Arjun Singh Chauhan & Vineet Sahula. (2015, September). High density impulsive noise removal using decision based iterated conditional modes. In 2015 international conference on signal processing, computing and control (ispcc) (pp. 24–29). doi:10.1109/ISPCC.2015.7374992 Miscellaneous Experience Awards & Achievements 2019 Fellowship Award: 32nd international conference on VLSI Design & 18th international conference on Embedded System, held at Manekshaw Center, New Delhi. 2017 Fellowship Award: 30th international conference on VLSI Design & 16th international conference on Embedded System, held at Hyderabad. 2014 Fellowship Award: Embedded System Week - 2014, held at Noida. Winning Award: College Level winner in "Texas Instruments Innovation Challenge India Analog Design Contest" 2014 held at MNIT, Jaipur. 2012 1st Runner-up Award: "LAN-Gaming" Event at "ROSTRUM - Tech Fest" at Jaipur Engineering College, Kukas, Jaipur. 2009 1st Runner-up Award: Shradhanjali: 8th National Level Technical Symposium cum Fest for the event CERN (Software Competition) at Arya Group of Colleges. 2008 2nd Runner-up Award: Shradhanjali: 7th National Level Technical Symposium cum Fest for the event CERN (Software Competition) at Arya Group of Colleges. Participation 2015 Participation Certificate: "Texas Instruments India Analog Maker Competition 2015" held at MNIT, Jaipur conducted by Texas Instruments India University Program. Miscellaneous Experience (continued) 2010 Completion Certificate: "Infosys Campus Connect Completion Award" held at Arya College of Engineering & Information Technology. Workshops & Short-term Courses Workshops & Short-term Courses 2017 EICT-Workshop: Academic Training Programme on "VLSI Design Verification" held at MNIT, Jaipur. EICT-Workshop: Faculty Development Programme on "CMOS Analog Integrated Circuit Design" held at MNIT, Jaipur. 2016 GIAN: Global Initiative of Academic Network course on "Advanced System Security: Attacks and Defenses" held at MNIT, Jaipur. Synopsys-Workshop: Workshop on "SMDP-C2SD Synopsys Tool Training Workshop" held at MNIT, Jaipur. INUP: INUP Familiarization Workshop on "Nanofabrication Technologies" held at MNIT, Jaipur. EICT-Workshop: Academy Workshop on "Modern Embedded Processors" held at MNIT, Jaipur. EICT-Workshop: Academic Training Programme on "Communication Channels for Information Transfer" held at MNIT, Jaipur. 2015 NICA: Nature Inspired Computing & Applications held at MNIT, Jaipur. 2014 ETEDM: "Emerging Technology: Electronic Devices & Materials" held at Material Research Center, MNIT, Jaipur. Workshop: National Workshop on "Embedded Systems" conducted by Computer Science and Engineering, MNIT, Jaipur. 2011 ISTE-Workshop: ISTE Workshop on "Solar Photovoltaic: Fundamentals, Technologies and Applications" conducted by IIT Bombay at JEC Group of Colleges. References Dr. Vineet Sahula Dr. A.S. Mandal Dr. D. Boolchandani Professor, ECE Chief Scientist Professor, ECE MNIT, JLN Marg Cognitive Computing Group MNIT, JLN Marg Jaipur, 302017 CEERI, Pilani, 333031 Jaipur, 302017 Q vsahula.ece@mnit.ac.in Q atanu@ceeri.res.in Q dbool@ieee.org