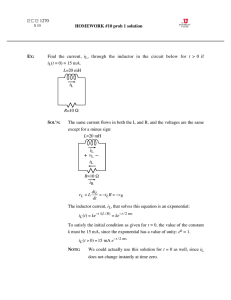

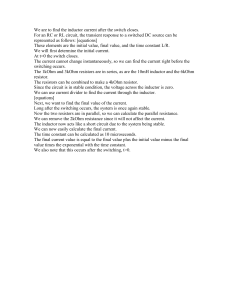

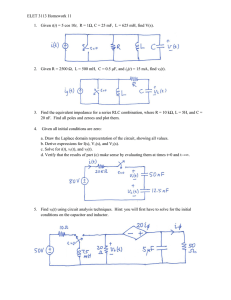

Accepted manuscript to appear in JCSC Accepted Manuscript J CIRCUIT SYST COMP Downloaded from www.worldscientific.com by UNIVERSITY OF NEW ENGLAND on 04/25/18. For personal use only. Journal of Circuits, Systems, and Computers Article Title: Tunable CMOS Active Inductor Using Widlar Current Source Author(s): Dhara P Patel, Shruti Oza-Rahurkar DOI: 10.1142/S0218126619500270 Received: 28 December 2017 Accepted: 18 April 2018 To be cited as: Dhara P Patel, Shruti Oza-Rahurkar, Tunable CMOS Active Inductor Using Widlar Current Source, Journal of Circuits, Systems, and Computers, doi: 10.1142/S0218126619500270 Link to final version: https://doi.org/10.1142/S0218126619500270 This is an unedited version of the accepted manuscript scheduled for publication. It has been uploaded in advance for the benefit of our customers. The manuscript will be copyedited, typeset and proofread before it is released in the final form. As a result, the published copy may differ from the unedited version. Readers should obtain the final version from the above link when it is published. The authors are responsible for the content of this Accepted Article. Click here to download Manuscript (pdf) ws-jcsc_Dhara.pdf March 9, 2018 16:5 WSPC/INSTRUCTION FILE ws-jcsc DM AN US Journal of Circuits, Systems, and Computers c World Scientific Publishing Company CR IP Accepted manuscript to appear in JCSC T Manuscript (pdf) Tunable CMOS Active Inductor Using Widlar Current Source Shruti Oza-Rahurkar§ Department of Electronics and Telecommunication,Bharti Vidyapeeth Deemed University College of Engineering Laboratory, Pune,Maharashtra 411043, India § shruti.oza11@gmail.com Received (Day Month Year) Revised (Day Month Year) Accepted (Day Month Year) TE A novel tuning principle for simple gyrator based CMOS active inductor circuit is presented. The method makes use of widlar current source to enhance the quality factor. The simulation of proposed active inductor provides maximum quality factor of 1819 at 2.88 GHz. The active inductor shows the inductive bandwidth of 1.66 GHz to 3.16 GHz and power consumption of 6.87 mW. The other characterization factors such as linearity, supply voltage sensitivity and noise analysis are discussed. The performance of tunable active inductor using widlar current source are compared with the same using simple current mirror. An active inductor using conventional current mirror and widlar current source have been implemented in 0.18 µm CMOS technology. Keywords: Active inductor (AI); conventional current mirror (CCM); quality factor (Q); widlar current source. 1. Introduction EP The increasing demand of RF integrated circuit is a significant reason that motivates to design power efficient and configurable architectures. The inductor has been an essential component in RF system design blocks such as voltage controlled oscillator, low noise amplifier, matching network, filter, power divider design, power supply noise reduction etc 1 -7 . The drawbacks of spiral inductor are large chip area, limited inductance value and weak quality factor, which are the main constraints for RF design 8 . Moreover, advantages of active inductors are small chip area, high AC C J CIRCUIT SYST COMP Downloaded from www.worldscientific.com by UNIVERSITY OF NEW ENGLAND on 04/25/18. For personal use only. Dhara P Patel Electronics and Communication Engineering Department, Charotar University of Science and Technology, Changa, Gujarat 388421, India∗ † dharapatel.ec@charusat.ac.in ∗ State completely without abbreviations, the affiliation and mailing address, including country. Typeset in 8 pt Times Italic. 1 WSPC/INSTRUCTION FILE Authors’ Names ws-jcsc EP TE DM AN US quality factor, wide inductance band and low voltage operation. The most vital advantage of active inductor over passive counterpart is its tunability. Nevertheless, the main drawbacks are power consumption, higher noise, poor linearity - all these are inherent in active inductor circuits 4 . The several techniques have been employed successfully to implement active inductor in literature 2 -12 . Each of them has attempted to achieve the optimal tradeoff between chip area, power consumption, quality factor, inductive bandwidth, noise and tuning range. Tuning network is one of the key factors to improve the performance of active inductor. Basically, current mirror is utilized for course tuning and varactors are for fine tuning of active inductor 13 . Recently, Common gate (CG)Common source (CS) gyrator based active inductor has been discussed in 1 . Less number of transistors proves the small chip area and low power consumption of active inductor circuit but the higher value of parasitic series resistance and lower value of parallel resistance value provide the lower value of quality factor. The multi cascode stage has been used to reduce the series resistance in 1 , subsequently it increases the quality factor and self resonance frequency of active inductor. It shows the wider inductive frequency range but the maximum quality factor is 567. In proposed AI circuit, quality factor has been further improved by adopting widlar current source and post layout results are compared with 1 . In presented work, gyrator based an active inductor circuit is considered as shown in Fig. 13 . It is composed of two transconductors realized by MOS transistors in common source configuration connected in feedback configuration. The common source facilitates low conductance at critical nodes (Zin and Zout ) and follows the high quality factor of 1819 at 2.88 GHz. Two cases are discussed in paper. In first case AI has been tuned by simple current mirror and in second case it has been tuned by employing widlar current source. The results of both the cases are compared in terms of quality factor, power consumption and supply voltage sensitivity, noise and linearity. Based on intense literature review it is fair to assert that the adoption of widlar current source in designing of active inductor has been demonstrated first time. The organization of paper is as follows. The core active inductor topology and widlar current source are described in Section 2. The performance of active inductor with widlar current source circuit is presented in Section 3. The simulation results of AI are presented in Section 4. Finally, conclusions are summarized in Section 5. 2. The Core Active Inductor Topology The CMOS based active inductor circuit and its simplified small signal model are shown in Figs. 1 and 2, respectively. It is assumed that the gate-source capacitance (Cgs ) is much greater than gate-drain capacitance (Cgd ). The input impedance Zin at the input port is given by the following equation: sCgs3 + gm4 + gds2 sCgs1 + gds3 1 1 + + (1) Zin = sCgs2 gds1 gm1 gm2 gm3 AC C J CIRCUIT SYST COMP Downloaded from www.worldscientific.com by UNIVERSITY OF NEW ENGLAND on 04/25/18. For personal use only. 2 16:5 T March 9, 2018 CR IP Accepted manuscript to appear in JCSC 16:5 WSPC/INSTRUCTION FILE ws-jcsc T March 9, 2018 CR IP Accepted manuscript to appear in JCSC 3 J CIRCUIT SYST COMP Downloaded from www.worldscientific.com by UNIVERSITY OF NEW ENGLAND on 04/25/18. For personal use only. DM AN US Instructions for Typesetting Manuscripts (Condensed Title for the Paper) TE Fig. 1. Conventional high quality factor active inductor. Fig. 2. Small signal equivalent circuit of active inductor in Fig. 1. 0 Zin sCgs3 + gm4 + gds2 sCgs1 + gds3 = gm1 gm2 gm3 (2) AC C EP By considering Cgs3 << Cgs1 + Cgs2 , the equivalent component values can be derived as, Cgs1 gm4 + gds2 Leq = (3) gm1 gm2 gm3 gds3 gm4 + gds2 Rs = (4) gm1 gm2 gm3 Cp = Cgs2 (5) T March 9, 2018 4 16:5 WSPC/INSTRUCTION FILE ws-jcsc Authors’ Names Rp = 1 gds1 CR IP Accepted manuscript to appear in JCSC (6) DM AN US Fig. 3. (a)Equivalent gyrator-C realization of the active inductor,(b) Simplified passive model. For very high value of parallel resistance Rp of active inductor, the quality factor can be determined as 14 , QL = ωLeq Rs (7) TE For applications such as voltage controlled oscillator and band pass filters, the active inductors with a large quality factor are very important. There are various techniques of enhancing the quality factor of active inductor such as basic cascode, regulated cascode, negative resistor etc, though it is at the cost of power consumption 14 -15 . In the presented work, Q enhancement by reducing the effect of Rs has been adequately discussed. The conductance at node 3 is responsible for the series resistance of active inductor. Response of active inductor are observed by adopting the simple current mirror and widlar current source at node 3. 2.1. Widlar Current Source EP The basic widlar current source is presented in Fig. 4 14 . The output impedance of widlar current source is higher than simple current mirror by the factor of 1+gm8 Rs . The modification of widlar current source as depicted in Fig. 4 are shown in Fig. 5. In order to make it self biased R1 (in Fig. 4) is replaced with transistors M6 − M7 as shown in Fig. 5. The value of resistance Rs decreases the current of M8 while the PMOS transistors (M6 and M7 ) require that Iout = Iref because they have identical dimensions. Therefore, it can be written as, AC C J CIRCUIT SYST COMP Downloaded from www.worldscientific.com by UNIVERSITY OF NEW ENGLAND on 04/25/18. For personal use only. Where Leq , Rs , Rp and Cp are equivalent inductor, series resistance, parallel resistance and parallel capacitance of active inductor circuit. According to eqs. (3) and (4), it is noteworthy that Leq and Rs are independently tunable by Cgs1 and gds3 , respectively. The gyrator circuit can be modelled as equivalent resonator as shown in Fig. 3. Vgs9 = Vgs8 + Iout Rs (8) T March 9, 2018 16:5 WSPC/INSTRUCTION FILE ws-jcsc CR IP Accepted manuscript to appear in JCSC 5 DM AN US J CIRCUIT SYST COMP Downloaded from www.worldscientific.com by UNIVERSITY OF NEW ENGLAND on 04/25/18. For personal use only. Instructions for Typesetting Manuscripts (Condensed Title for the Paper) Fig. 4. Widlar current source. Fig. 5. Self biased widlar current source. TE s 2Iout + VT H9 = µn Cox (W/L)9 s 2Iout + VT H8 + Iout Rs µn Cox K(W/L)8 EP By ignoring the body effect, s 2Iout 1 1− √ = Iout Rs µn Cox (W/L)9 K (9) (10) Simplified form, Iout = 2 1 1 2 . 2 1− √ µn Cox (W/L)9 Rs K (11) AC C As stated in eq. (11), current Iout will flow as long as K is not equal to 1. Constant K is the (W/L) ratio of transistors M9 and M8 . WSPC/INSTRUCTION FILE Authors’ Names ws-jcsc J CIRCUIT SYST COMP Downloaded from www.worldscientific.com by UNIVERSITY OF NEW ENGLAND on 04/25/18. For personal use only. DM AN US 6 16:5 T March 9, 2018 CR IP Accepted manuscript to appear in JCSC TE Fig. 6. Active inductor using conventional current source. EP Fig. 7. Active inductor using widlar current source. 3. Performance of Active Inductor AC C The primary effect of active inductor (as shown in Fig. 1) by adopting two different tuning networks is analyzed. Figs. 6 and 7 represent the active indcutor circuit using simple current mirror and widlar current source, respectively. In Fig. 6, the current mirror is connected in shunt at node 3 and the conductance can be calculated as gds3 ||gds5 . In Fig. 7, the widlar current source is connected at the gate 16:5 WSPC/INSTRUCTION FILE ws-jcsc Instructions for Typesetting Manuscripts (Condensed Title for the Paper) 7 DM AN US of transistor M5 . The degenerated source resistance Rs at the source of transistor M8 will pull down the drain current of M5 and henceforth the value of gds5 will be reduced. Consequently, the conductance at node 3 (gds3 ||gds5 ) will get diminished compared to former. The main property of widlar current source is its infinite output impedance means very low conductance. The active inductor circuit using widlar current source reduces the Rs and as per Eq. (7), it results into improvement of quality factor. In order to adopt a low power technique, transistor M1 of active inductor circuit has been operated in sub-threshold region. To fulfill the sub-threshold condition, gate-source voltage of transistor M1 is set slightly less than the threshold voltage. The widlar current source generates low current compared to the current mirror source 17 . Hence, it reduces static power and subsequently improves the total power consumption. The frequency range over which active inductor circuit behaves as an inductor is defined as inductive bandwidth and it is limited by series resistance Rs 14 . The widlar current source reduces the series resistance and enhances the inductive frequency range. The supply voltage sensitivity of the inductance of active inductors is a figure-ofmerit quantifying the effect of the variation of the supply voltage on the inductance of the active inductors. The supply independent widlar current source makes the overall circuit less sensitive to the supply voltage variation. 4. Simulation Results EP TE In Fig. 6, the biasing current I2 is replaced with current mirror and in Fig. 7 same with the widlar current source. To tune the circuits, MOSFET is biased in triode region that functions as a resistor Rs . The layout of active inductor using conventional current source and widlar current source are shown in Fig. 8 and 9, respectively. The minimal output conductance of widlar current source reduces the series resistance and improves the quality factor. The active inductor using widlar current source results into maximum quality factor Qmax = 1819 at 2.88 GHz whereas using current mirror provides Qmax = 269 at 3.6 GHz. The micro current generation in widlar source reduces the static current of active inductor and minimizes the power consumption. The power consumption using simple current mirror is 10.2 mW whereas using widlar, it is 6.87 mW which is comparable. The inductive behavior of active inductor can be verified from the Bode plot. The phase angle should be 90◦ in the the phase plot. The phase error is due to parasitic series resistance RS and parallel resistance RP . Therefore, inductance value can be calculated when the phase angle in phase plot becomes equal to 90◦ . The corresponding frequency can be called as inductive frequency as illustrated in Fig. 10. The inductive frequency as a function of control voltage (Vctrl ) is shown AC C J CIRCUIT SYST COMP Downloaded from www.worldscientific.com by UNIVERSITY OF NEW ENGLAND on 04/25/18. For personal use only. T March 9, 2018 CR IP Accepted manuscript to appear in JCSC WSPC/INSTRUCTION FILE ws-jcsc DM AN US Authors’ Names Fig. 9. Layout of active inductor using widlar current source. EP TE Fig. 8. Layout of active inductor using conventional current source. Fig. 10. Bode plot of active inductor as shown in Fig. 7 at Vctrl = 0.8V . AC C J CIRCUIT SYST COMP Downloaded from www.worldscientific.com by UNIVERSITY OF NEW ENGLAND on 04/25/18. For personal use only. 8 16:5 T March 9, 2018 CR IP Accepted manuscript to appear in JCSC 16:5 WSPC/INSTRUCTION FILE ws-jcsc T March 9, 2018 CR IP Accepted manuscript to appear in JCSC 9 J CIRCUIT SYST COMP Downloaded from www.worldscientific.com by UNIVERSITY OF NEW ENGLAND on 04/25/18. For personal use only. DM AN US Instructions for Typesetting Manuscripts (Condensed Title for the Paper) Fig. 11. Variation in inductive frequency range with control voltage. EP TE Fig. 12. Supply sensitivity of active inductor using simple current mirror. Fig. 13. Supply sensitivity of active inductor using widlar current mirror. AC C in Fig. 11. The inductive bandwidth using simple current mirror is 0.9 GHz (3.1 GHz - 4 GHz), whereas using widlar current source it expands to 1.5 GHz (1.66 GHz - 3.16 GHz). It is clearly seen that widlar current source expands the inductive WSPC/INSTRUCTION FILE ws-jcsc Authors’ Names J CIRCUIT SYST COMP Downloaded from www.worldscientific.com by UNIVERSITY OF NEW ENGLAND on 04/25/18. For personal use only. DM AN US 10 16:5 T March 9, 2018 CR IP Accepted manuscript to appear in JCSC Fig. 14. Quality factor as a function of control voltage. EP TE Fig. 15. THD performance of active inductor. Fig. 16. Noise performance of active inductor using conventional current mirror. AC C bandwidth. The widlar current source is supply independent that helps to reduce the overall supply voltage sensitivity. The supply voltage sensitivity of active inductor has been 16:5 WSPC/INSTRUCTION FILE ws-jcsc DM AN US Instructions for Typesetting Manuscripts (Condensed Title for the Paper) 11 Fig. 17. Noise performance of active inductor using widlar current source. EP TE measured over the tuning range. The active inductor with widlar current source experiences the variation in range of 1.44 nH - 3.58 nH (as shown in Fig. 12)whereas with current mirror it feels the changes in range of 5.14 nH - 34.2 nH (as shown in Fig. 13). It is observable that the AI circuit using widlar current biasing is more robust against voltage variation. The nonlinear behavior of AI has been described by Total Harmonic Distortion (THD). It describes the ratio of total harmonic current to fundamental current when a fundamental ac input signal has been injected into the active inductor 9 . As depicted in Fig.15, AI with current mirror shows slightly higher linearity than same using widlar current source. Fig. 16 and 17, represent the noise analysis. AI using widlar manifests better noise performance. Active inductor using widlar current source uses additional two PMOS transistors (M6 and M7 ) as shown in Fig.7. The mobility of NMOS in submicron technologies is 4 to 5 times to that of PMOS. The lower value of mobility will restrict the operation at high frequency. The addition of two PMOS transistors limit the higher inductive frequency of active inductor. Therefore, AI using current mirror results in high inductive frequency whereas by using widlar current source, it operates in low inductive frequency range. Another tradeoff is that number of total transistors are higher than conventional current mirror that increases the chip area. Table 1 shows the comparison of active inductor by employing the two various current sources - current mirror and widlar current source. AI with widlar current source enhances the quality factor, noise performance, inductance variation against supply voltage and power consumption. It follows the trade-offs with inductive bandwidth, linearity and area consumption. AC C J CIRCUIT SYST COMP Downloaded from www.worldscientific.com by UNIVERSITY OF NEW ENGLAND on 04/25/18. For personal use only. T March 9, 2018 CR IP Accepted manuscript to appear in JCSC T March 9, 2018 12 16:5 WSPC/INSTRUCTION FILE ws-jcsc Authors’ Names CR IP Accepted manuscript to appear in JCSC Table 1. Comparison of active indcutor using two current sources. AI using current mirror source AI using widlar current source 269 at 3.6 GHz 0.9 5.14 - 34.2 16 - 22 < 44.68 616 10.2 1819 at 2.88 GHz 1.5 1.44 - 3.58 12.7 - 14.4 < 54 1230 6.87 DM AN US Table 2. Comparison of active indcutor. Technology (µm) Quality factor Inductive frequency range (GHz) THD (%) Noise ( √nV ) Hz Power dissipation (mW) Area (µm2 ) 5. Conclusion [1 ] This work (AI using widlar current source) 0.18 10-567 0.1 - 6.2 2 934.4 0.18 34-1819 1.9 -3.45 < 54 14.5 6.87 1230 Table 2 compares the performance of presented active inductor using widlar current source with the architecture presented in 1 . The quality enhancement technique offers the high quality factor that is comparable with 1 . The proposed circuit with better quality factor can be used in RF applications for inductive bandwidth of 1.9 GHz to 3.45 GHz. TE References EP 1. Mustafa Konal and Firat Kacar, MOS Only Grounded Active Inductor Circuits and Their Filter Applications, Journal of Circuits, Systems and Computers, 2017, vol. 26, No.6. 2. H. G. Momen, M. Yazgi,Design of a new low loss fully CMOS tunable floating active inductor, Analog Integrated Circuits and Signal Processing, 2016, vol.89, No.3, pp 727737. 3. A. Taparia, B. Banerjee, and T R Viswanathan, Power-supply noise reduction using active inductors in mixed-signal systems, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2011, vol. 19, No.11, pp 1960-1968. 4. S. Saad, M. Mhiri, A B Hammadi, A New Low-power, High-Q, Wide Tunable CMOS Active Inductor for RF Applications, IETE Journal Paper, 2016, vol.62, No.2, pp 265273. 5. H. Xiao, R. Sshaumann, A 5.4-GHz high-Q tunable active-inductor bandpass filter in standard digital CMOS technology , Analog Integr Circ Sig Process, 2007, pp 1-9, vol. 51. No. 1. 6. L. Pantoli, V. Stornelli, G. Leuzzi, A low-voltage low-power 0.25 µm integrated single AC C J CIRCUIT SYST COMP Downloaded from www.worldscientific.com by UNIVERSITY OF NEW ENGLAND on 04/25/18. For personal use only. Maximum quality factor Inductive bandwidth (GHz) Inductance variation (n H) against supply voltage Noise ( √nV ) Hz THD (%) Area (µm2 ) Power consumption (m W) 16:5 WSPC/INSTRUCTION FILE ws-jcsc Instructions for Typesetting Manuscripts (Condensed Title for the Paper) 13 EP TE DM AN US transistor active inductor-based filter , Analog Integr Circ Sig Process, 2016, vol. 87, No.3, pp-463-469. 7. R. Bhattacharya, A. Banu, and S.K. Koul, A Highly Linear CMOS Active Inductor and Its Application in Filters and Power Dividers , IEEE Microwave and Wireless Components Letters, 2015, pp 715-717, vol. 25, No.11. 8. T.Sato, T. Ito, Design of low distortion active inductor and its applications , Analogue Integrated Circuits and Signal Processing,2013, pp 245-255, vol.75,No.2. 9. Ler, Chun-Lee, Abu Khari Bin A’ain and Albert Victor Kordesch, CMOS active inductor linearity improvement using feed-forward current source technique, IEEE transactions on microwave theory and techniques, 2009, pp 1915-1924, vol.57, No.8. 10. C. Andriesei and L. Goras,On Frequency and Quality Factor Independent Tuning Possibilities for RF Band-pass Filters with Simulated Inductors, Romanian journal of information science and technology,2008,pp.367382, vol.11. 11. R.Mukhopadhy,Tunable active inductor, U.S Patent no. 2006/0170523, August,2006. 12. H.U.Uyanik, N Tarim, Compact low voltage high-Q CMOS active inductor suitable for RF applications, Analog integrated circuits and signal processing, 2007,pp.191-194, vol. 51, No.3. 13. A. I Karsilayan, R. Schaumann, A high-frequency high-Q CMOS active inductor with DC bias control, 43rd IEEE Midwest Symp. on Circuits and Systems, 2000, pp.486-489, Vol. 1. 14. H. G. Momem, M. Yazgi, R. Kopru and A. N. Saatlo, A new high performance CMOS active inductor, 2016 39th International Conference on Telecommunications and Signal Processing (TSP),2016, pp. 291-294. 15. H. Xiao, R Schaumann and W. R Daasch, High frequency active inductor, U.S Patent No. 7,042,317.9, 2006. 16. F.Yuan, CMOS Active Inductors and Transformers Principle, Implementation and Applications, springer,pp 21-99 2008. 17. U. Yodprasit and J. Ngarmnil, Q-Enhancing Technique for RF CMOS Active Inductor , IEEE International Symposium on Circuits and Systems,2000, pp. 589-592. 18. A. Sedra, K. C.Smith, Microelectronic Circuits Theory and Applications, Oxford University press, 2012, ISBN-10: 0199476292. 19. R. J. Widlar, Low-value current source for integrated circuits, U.S. Patent Application No. US3320439 A, May 1965. 20. Y. J. Jeong, Y. M. Kim, H. J. Chang and T. Y. Yun, Low-power CMOS VCO with a low-current, high-Q active inductor, IET Microwaves, Antennas and Propagation, 2012, vol. 6, no. 7, pp. 788-792. AC C J CIRCUIT SYST COMP Downloaded from www.worldscientific.com by UNIVERSITY OF NEW ENGLAND on 04/25/18. For personal use only. T March 9, 2018 CR IP Accepted manuscript to appear in JCSC