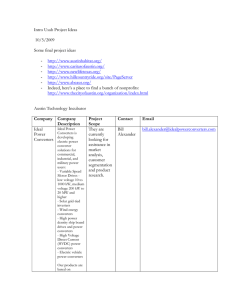

ECE 730 Course Project, milestone 1: due Nov 9th, 4 pm (Late submission → 5% reduction for every 24 hours delay) In this project milestone, the converters shown in Fig. 1 should be analyzed in the steady-state condition. The modulation scheme of the converter switches is shown in Fig.2. Please obtain the following items for both converters. Section 1: (A) Provide switch realization for all the switches of both converters. (B) Calculate the steady-state DC values for inductor currents and capacitor voltages. (C) Obtain the voltage conversion ratio (VL/VH) of both converters and then plot the voltage conversion ratio versus the duty cycle for both converters in a curve. (D) Plot the steady-state waveforms of inductor voltages and capacitor currents. (E) Calculate the ripple currents of inductors, ripple current of IX and ripple voltage of capacitors. (F) Obtain the peak and RMS current of the switches and inductors. (G) Obtain the peak voltage of the switches. (H) Compare the converters in a table based on the obtained parameters in C, E, F and G. (I) Using the following values, simulate1 the converter. Then using the simulated voltage and current waveforms of inductors, capacitors and switches, and IX, verify the analysis for parts B,C,E,F,G,H. Summarize the results of the comparison in a table that includes both simulated estimation and analysis calculations. Table.1: Simulation parameters Parameter value Switching frequency 100 kHz VH 48 V VL 12 V Ro 1.2 Ω L1 200 µH Co 20 µF C1, C2 10 µF Section 2: Considering the parasitic components (Inductors resistances (RL), Switch on resistances (RDSON), Diode forward bias voltage (Vγ) and capacitor resistances (ESR)): (A) Obtain the voltage conversion ratio VL/VH of both converters. (B) Add parasitic components to both of the converters and, using the following values, calculate the efficiency of the converters. Table.2: Parasitic components values parameters Parameter value RL 0.1 Ω RDSON 0.05 Ω Vγ 1V ESR 1Ω (C) Simulate the converter with the mentioned values. Show and compare the results with section 1(I). (D) obtain the simulation efficiency and compare it with the calculations. Section 3: assume the output resistor (R) is replaced with a DC voltage source VL in Fig 1. (A) Realize the switches so that the power can flow in both directions from VH to VL as well as VH to VL. For simulation you can use PSIM, MATLAB Simulink and PSPICE. If you don’t have access to any of these software please contact mesteki@ualberta.ca. 1 (B) Assume the power flows from VL to VH, obtain the voltage conversion ratio VH/VL of both converters and then plot the voltage conversion ratio versus the duty cycle for both converters in a curve. IX L1 S1 S2 Co Ro VH S3 S4 L2 + VL - (a) +S 1 VC1 S2 C1 VH L1 Co + VC2 C2 - + Ro VL - S4 S3 (b) Fig. 1: (a) Conventional Interleaved Buck Converter, (b) A Modified Interleaved Buck Converter S1 D.Tsw S4 (0.5).Tsw S2 (1-D).Tsw Tsw S1 (0.5).Tsw S3 S4 D.Tsw (1-D).Tsw Tsw Fig. 2: Modulation scheme of the converter’s switches