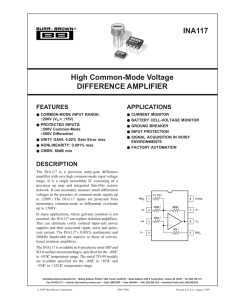

INA117 INA 117 INA 117 www.ti.com High Common-Mode Voltage DIFFERENCE AMPLIFIER FEATURES APPLICATIONS ● COMMON-MODE INPUT RANGE: ±200V (VS = ±15V) ● PROTECTED INPUTS: ±500V Common-Mode ±500V Differential ● UNITY GAIN: 0.02% Gain Error max ● NONLINEARITY: 0.001% max ● CMRR: 86dB min ● ● ● ● ● CURRENT MONITOR BATTERY CELL-VOLTAGE MONITOR GROUND BREAKER INPUT PROTECTION SIGNAL ACQUISITION IN NOISY ENVIRONMENTS ● FACTORY AUTOMATION DESCRIPTION The INA117 is a precision unity-gain difference amplifier with very high common-mode input voltage range. It is a single monolithic IC consisting of a precision op amp and integrated thin-film resistor network. It can accurately measure small differential voltages in the presence of common-mode signals up to ±200V. The INA117 inputs are protected from momentary common-mode or differential overloads up to ±500V. In many applications, where galvanic isolation is not essential, the INA117 can replace isolation amplifiers. This can eliminate costly isolated input-side power supplies and their associated ripple, noise and quiescent current. The INA117’s 0.001% nonlinearity and 200kHz bandwidth are superior to those of conventional isolation amplifiers. 21.11kΩ RefB 1 –In 2 +In 3 V– 4 380kΩ 8 Comp 7 V+ 6 VO 5 RefA 380kΩ 380kΩ 20kΩ The INA117 is available in 8-pin plastic mini-DIP and SO-8 surface-mount packages, specified for the –40°C to +85°C temperature range. The metal TO-99 models are available specified for the –40°C to +85°C and –55°C to +125°C temperature range. Copyright © 2000, Texas Instruments Incorporated SBOS154A Printed in U.S.A. December, 2000 SPECIFICATIONS At TA = +25°C, VS = ±15V, unless otherwise noted. INA117AM, SM PARAMETER CONDITIONS MIN GAIN Initial (1) Error vs Temperature Nonlinearity (2) OUTPUT Rated Voltage Rated Current Impedance Current Limit Capacitive Load IO = +20mA, –5mA VO = 10V To Common Stable Operation INPUT Impedance Differential Common-Mode Differential Common-Mode, Continuous Voltage Range Common-Mode Rejection DC AC, 60Hz vs Temperature, DC AM, BM, P, KU SM 10 +20, –5 INA117BM TYP MAX 1 0.01 2 0.0002 0.05 10 0.001 MIN ✻ ✻ ✻ ✻ ✻ 12 TYP INA117P, KU MAX MIN ✻ ✻ ✻ ✻ 0.02 ✻ ✻ ✻ TYP ✻ ✻ MAX UNITS V/V % ppm/°C % ✻ ✻ ✻ V mA Ω mA pF 0.01 +49, –13 1000 ✻ ✻ ✻ ✻ ✻ ✻ 800 400 ✻ ✻ ✻ ✻ ✻ ✻ kΩ kΩ V V ✻ ✻ dB dB ✻ dB dB ±10 ±200 ✻ ✻ (3) VCM = 400Vp-p TA = TMIN to TMAX OFFSET VOLTAGE Initial KU Grade (SO-8 Package) vs Temperature vs Supply vs Time RTO DYNAMIC RESPONSE Gain Bandwidth, –3dB Full Power Bandwidth Slew Rate Settling Time: 0.1% 0.01% 0.01% POWER SUPPLY Rated Voltage Range Quiescent Current TEMPERATURE RANGE Specification: AM, BM, P, KU SM Operation Storage RTO 80 80 86 66 94 94 66 60 75 75 80 90 74 120 1000 8.5 90 200 40 80 ✻ 1000 ✻ ✻ ✻ 40 ✻ ✻ ✻ 600 ✻ ✻ ✻ ✻ 2000 µV µV µV/°C dB µV/mo (5) ✻ ✻ 25 550 ✻ 200 VO = 20Vp-p VCM ✻ ✻ (4) TA = TMIN to TMAX VS = ±5V to ±18V OUTPUT NOISE VOLTAGE fB = 0.01Hz to 10Hz fB = 10kHz 70 66 30 2 VO = 10V Step VO = 10V Step = 10V Step, VDIFF = 0V Derated Performance VO = 0V ±5 2.6 6.5 10 4.5 ±15 1.5 –25 –55 –55 –65 ✻ ✻ ✻ ✻ ✻ ✻ ✻ ✻ ✻ ±18 2 ✻ +85 +125 +125 +150 ✻ ✻ µVp-p nV/√Hz ✻ kHz kHz V/µs µs µs µs ✻ ✻ ✻ ✻ ✻ V V mA ✻ ✻ ✻ ✻ ✻ –40 +85 ✻ ✻ ✻ ✻ –40 –55 +85 +125 ✻ ✻ ✻ ✻ °C °C °C °C ✻Specification same as for INA117AM. NOTES: (1) Connected as difference amplifier (see Figure 1). (2) Nonlinearity is the maximum peak deviation from the best-fit straight line as a percent of full-scale peak-to-peak output. (3) With zero source impedance (see discussion of common-mode rejection in Application Information section). (4) Includes effects of amplifier’s input bias and offset currents. (5) Includes effects of amplifier’s input current noise and thermal noise contribution of resistor network. 2 INA117 SBOS154A PIN CONFIGURATION Top View TO-99 INA117AM, BM, SM Tab 8 Ref B –In Top View DIP/SO INA117P, KU Comp 1 7 V+ 2 6 3 RefB 1 8 Comp –In 2 7 V+ +In 3 6 Output V– 4 5 RefA Output 5 Ref A +In 4 V– Case internally connected to V–. Make no connection. ELECTROSTATIC DISCHARGE SENSITIVITY ABSOLUTE MAXIMUM RATINGS Supply Voltage .................................................................................. ±22V Input Voltage Range, Continuous ................................................... ±200V Common-Mode and Differential, 10s ........................................... ±500V Operating Temperature M Metal TO-99 ................................................................ –55 to +125°C P Plastic DIP and U SO-8 ................................................ –40 to +85°C Storage Temperature M Package ....................................................................... –65 to +150°C P Plastic DIP and U SO-8 .............................................. –55 to +125°C Lead Temperature (soldering, 10s) ............................................... +300°C Output Short Circuit to Common ............................................. Continuous This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications. PACKAGE/ORDERING INFORMATION PRODUCT INA117P INA117KU " PACKAGE DRAWING NUMBER SPECIFIED TEMPERATURE RANGE DIP-8 006 –40°C to +85°C INA117P INA117P Rails SO-8 Surface-Mount 182 " INA117KU INA117KU Rails PACKAGE PACKAGE MARKING ORDERING NUMBER(1) TRANSPORT MEDIA " " " " INA117KU/2K5 Tape and Reel INA117AM TO-99 Metal 001 –25°C to +85°C INA117AM INA117AM Rails INA117BM " " " INA117BM INA117BM Rails INA117SM " " –55°C to +125°C INA117SM INA117SM Rails NOTE: (1) Models with a slash (/) are available only in Tape and Reel in the quantities indicated (e.g., /2K5 indicates 2500 devices per reel). Ordering 2500 pieces of “INA117KU/2K5” will get a single 2500-piece Tape and Reel. INA117 SBOS154A 3 TYPICAL PERFORMANCE CURVES At TA = +25°C, VS = ±15V, unless otherwise noted. COMMON-MODE REJECTION vs FREQUENCY POWER-SUPPLY REJECTION vs FREQUENCY 100 INA117BM Power-Supply Rejection (dB) Common-Mode Rejection (dB) 100 90 80 INA117AM, SM, P, KU 70 60 50 40 100 1k 10k 100k V+ 70 60 50 2M 1 10 100 1k 10k Frequency (Hz) Frequency (Hz) POSITIVE COMMON-MODE VOLTAGE RANGE vs POSITIVE POWER-SUPPLY VOLTAGE NEGATIVE COMMON-MODE VOLTAGE RANGE vs NEGATIVE POWER-SUPPLY VOLTAGE –400 TA = –55°C 350 TA = +25°C 300 Max Rating = 200V 250 TA = +125°C 200 150 –VS = –5V to –20V 100 50 Negative Common-Mode Range (V) 400 Positive Common-Mode Range (V) V– 80 40 20 –350 TA = +25°C –300 Max Rating = –200V –250 TA = –55°C to +125°C –200 –150 +VS = +5V to +20V –100 –50 5 10 15 Positive Power-Supply Voltage (V) 4 90 20 –5 –10 –15 –20 Negative Power-Supply Voltage (V) INA117 SBOS154A TYPICAL PERFORMANCE CURVES (Cont.) At TA = +25°C, VS = ±15V, unless otherwise noted. SMALL SIGNAL STEP RESPONSE CL = 0 SMALL SIGNAL STEP RESPONSE CL = 1000pF LARGE SIGNAL STEP RESPONSE INA117 SBOS154A 5 APPLICATION INFORMATION Figure 1 shows the basic connections required for operation. V– Applications with noisy or high-impedance power-supply lines may require decoupling capacitors close to the device pins. V+ 4 The output voltage is equal to the differential input voltage between pins 2 and 3. The common mode input voltage is rejected. 2 V2 Internal circuitry connected to the compensation pin 8 cancels the parasitic distributed capacitance between the feedback resistor, R2, and the IC substrate. For specified dynamic performance, pin 8 should be grounded or connected through a 0.1µF capacitor to an AC ground such as V+. 380kΩ 6 380kΩ 3 V3 7 380kΩ VO = V3 – V2 21.1kΩ 20kΩ 8 –15V 1 +15V 5 100kΩ +15V (a) + + 1µF Tantalum 4 2 7 R1 380kΩ 10Ω 1µF Tantalum R2 380kΩ V– V+ 4 –In = V2 R3 3 2 6 380kΩ VO = V 3 – V 2 7 380kΩ 380kΩ V2 +In = V3 R5 21.1kΩ 50kΩ ±1.5mV Range –15V R4 20kΩ 3 6 380kΩ VO = V3 – V2 V3 8 1 5 V+ 21.1kΩ 8 20kΩ 1 100µA 1/2 REF200 5 FIGURE 1. Basic Power and Signal Connections. 100Ω COMMON-MODE REJECTION Common-mode rejection (CMR) of the INA117 is dependent on the input resistor network, which is laser-trimmed for accurate ratio matching. To maintain high CMR, it is important to have low source impedances driving the two inputs. A 75Ω resistance in series with pin 2 or 3 will decrease CMR from 86dB to 72dB. (b) OPA27 ±10mV 10kΩ 100µA 1/2 REF200 Resistance in series with the reference pins will also degrade CMR. A 4Ω resistance in series with pin 1 or 5 will decrease CMRR from 86dB to 72dB. Most applications do not require trimming. Figures 2 and 3 show optional circuits that may be used for trimming offset voltage and common-mode rejection. TRANSFER FUNCTION Most applications use the INA117 as a simple unity-gain difference amplifier. The transfer function is: VO = V3 – V2 100Ω Offset adjustment is regulated— insensitive to power supply variations. V– FIGURE 2. Offset Voltage Trim Circuits. Some applications, however, apply voltages to the reference terminals (pins 1 and 5). A more complete transfer function is: VO = V3 – V2 + 19 • V5 – 18 • V1 V5 and V1 are the voltages at pins 5 and 1. V3 and V2 are the voltages at pins 3 and 2. 6 INA117 SBOS154A MEASURING CURRENT The INA117 can be used to measure a current by sensing the voltage drop across a series resistor, RS. Figure 4 shows the INA117 used to measure the supply currents of a device under test. The circuit in Figure 5 measures the output current of a power supply. If the power supply has a sense connection, it can be connected to the output side of RS to eliminate the voltage-drop error. Another common application is current-to-voltage conversion, as shown in Figure 6. V– V+ (+200V max) +VS 4 7 380kΩ 2 380kΩ C RS RC* 6 380kΩ 3 VO = RS IDUT+ IDUT+ 21.1kΩ V– V+ 8 4 V2 2 20kΩ 1 5 7 380kΩ Device Under Test 380kΩ V+ V– 4 6 V3 3 380kΩ 380kΩ 2 21.1kΩ 8 10Ω RS 6 380kΩ 3 5 200Ω 380kΩ RC* 20kΩ 1 7 IDUT– VO = V3 – V2 VO = RS IDUT– CMR Adjust 21.1kΩ 10Ω 8 –VS 20kΩ 1 5 (–200V max) If offset adjust is also required, connect to offset circuit, Figure 2. *Not needed if R S is less than 20Ω —see text. FIGURE 4. Measuring Supply Currents of Device Under Test. FIGURE 3. CMR Trim Circuit. V– V+ 4 7 Power Supply ±200V max 2 Out 380kΩ 380kΩ Sense RS RC* Optional Load Sense Connection (see text) 3 6 380kΩ VO = IL RS IL 21.1kΩ 20kΩ Load 8 1 5 *RC = RS not needed if RS is less than 20Ω—see text. FIGURE 5. Measuring Power Supply Output Current. INA117 SBOS154A 7 VS (±200V max) 2 380kΩ 380kΩ RS 250Ω 3 250Ω RC* 4 to 20mA 6 380kΩ VO = 1V to 5V 21.1kΩ 8 20kΩ 1 5 VS (a) (±200V max) *Not needed if RS is less than 20Ω—see text. 2 380kΩ 380kΩ 250Ω RC * RS 250Ω 3 6 380kΩ VO = –1V to –5V 4 to 20mA 21.1kΩ 8 20kΩ 1 5 (b) 4 to 20mA 2 380kΩ 380kΩ *Not needed if RS is less than 20Ω—see text. 250Ω RC * RS 250Ω 3 6 380kΩ VO = 1V to 5V 20kΩ 21.1kΩ 8 VS 1 5 (±200V max) 4 to 20mA (c) *Not needed if RS is less than 20Ω—see text. 2 380kΩ 380kΩ RS 250Ω 6 3 380kΩ VO = –1V to –5V 250Ω RC * 21.1kΩ VS (±200V max) 8 20kΩ 1 5 (d) *Not needed if RS is less than 20Ω—see text. FIGURE 6. Current to Voltage Converter. 8 INA117 SBOS154A Example: For a 1V/mA transfer function, the nominal, uncorrected value for RS would be 1kΩ. A slightly larger value, RS' = 1002.6Ω, compensates for the gain error due to loading. In all cases, the sense resistor imbalances the input resistor matching of the INA117, degrading its CMR. Also, the input impedance of the INA117 loads RS, causing gain error in the voltage-to-current conversion. Both of these errors can be easily corrected. The 380kΩ term in the equation for RS' has a tolerance of ±25%, so sense resistors above approximately 400Ω may require trimming to achieve gain accuracy better than 0.02%. The CMR error can be corrected with the addition of a compensation resistor, RC, equal in value to RS as shown in Figures 4, 5, and 6. If RS is less than 20Ω, the degradation in CMR is negligible and RC can be omitted. If RS is larger than approximately 2kΩ, trimming RC may be required to achieve greater than 86dB CMR. This is because the actual INA117 input impedances have 1% typical mismatch. Of course, if a buffer amplifier is added as shown in Figure 7, both inputs see a low source impedance, and the sense resistor is not loaded. As a result, there is no gain error or CMR degradation. The buffer amplifier can operate as a unity gain buffer or as an amplifier with non-inverting gain. Gain added ahead of the INA117 improves both CMR and signal-to-noise. Added gain also allows a lower voltage drop across the sense resistor. The OPA1013 is a good choice for the buffer amplifier since both its input and output can swing close to its negative power supply. If RS is more than approximately 100Ω, the gain error will be greater than the 0.02% specification of the INA117. This gain error can be corrected by slightly increasing the value of RS. The corrected value, RS', can be calculated by: R S' = R S • 380 kΩ 380 kΩ – R S –15V V1 +15V 4 7 I 380kΩ 2 VX V1 –21V to +10V –5V to –36V –20V to –51V +15V Ground –15V 380kΩ R2 * RS 6 380kΩ 3 VO = I • RS • (1 + 1/2 OPA1013 21.1kΩ R1 * 8 –VX Op amp power can be derived with voltagedropping zener diode if –VX power is relatively constant. |VX| = (5V to 36V) + VZ e.g., If VZ is 50V then VX = –55V to –86V. R2 ) R1 20kΩ 1 5 *Or connect as buffer (R2 = 0, omit R1). Regulated power for op amp allows –VX power to vary over wide range. 180k Ω VZ VX = –30V to –200V MPS-A42 0.01µF IN4702 or –VX V– V+ 4 2 I 7 380kΩ 380kΩ RS 3 6 380kΩ V O = I • RS 1/2 OPA1013 0.1µF 21.1kΩ 8 20kΩ 1 5 –VX FIGURE 7. Current Sensing with Input Buffer. INA117 SBOS154A 9 Figure 8 shows very high input impedance buffer used to measure low leakage currents. Here, the buffer op amp is powered with an isolated, split-voltage power supply. Using an isolated power supply allows full ±200V common-mode input range. these resistors produces approximately 550nV/√Hz noise. The internal op amp contributes virtually no excess noise at frequencies above 100Hz. Many applications may be satisfied with less than the full 200kHz bandwidth of the INA117. In these cases, the noise can be reduced with a low-pass filter on the output. The twopole filter shown in Figure 9 limits bandwidth to 1kHz and reduces noise by more than 15:1. Since the INA117 has a 1/f noise corner frequency of approximately 100Hz, a cutoff frequency below 100Hz will not further reduce noise. NOISE PERFORMANCE The noise performance of the INA117 is dominated by the internal resistor network. The thermal or Johnson noise of ±200V max 1kΩ +15V 100MΩ +15V Isolated DC/DC Converter 9kΩ D1,2* PWS725 Com OPA111 –15V IL 100kΩ Device Under Test 2 *D1 and D2 are each a 2N3904 transistor base-collector junction (emitter open). 3 380kΩ 380kΩ 6 380kΩ eO = IL x 109 (1V/nA) 21.1kΩ 20kΩ INA117 8 1 5 FIGURE 8. Leakage Current Measurement Circuit. V+ V– 4 V2 V3 2 3 7 380kΩ C2 0.02µF 380kΩ 6 380kΩ R1 11.0kΩ R2 11.3kΩ OPA27 2-Pole Butterworth Low-Pass Filter C1 0.01µF 21.1kΩ 8 VO = V2 – V3 20kΩ 1 5 BUTTERWORTH LOW-PASS OUTPUT NOISE f–3dB (mVp-p) 200kHz 100kHz 10kHz 1kHz ≤100Hz(1) See Application Bulletin AB-017 for other filters. 1.8 1.1 0.35 0.11 0.05 R1 11kΩ 11kΩ 11kΩ 11kΩ R2 C1 No Filter 11.3kΩ 100pF 11.3kΩ 1nF 11.3kΩ 10nF 11.3kΩ 0.1µF C2 200pF 2nF 20nF 0.2µF NOTE: (1) Since the INA117 has a 1/f noise corner frequency of approximately 100Hz, bandwidth reduction below this frequency will not significantly reduce noise. FIGURE 9. Output Filter for Noise Reduction. 10 INA117 SBOS154A V2 380kΩ 2 380kΩ V– V+ 4 V3 6 380kΩ 3 VO = 1+ 19 R7 380kΩ 2 V2 R6 21.1kΩ 7 V3 – V 2 380kΩ 20kΩ INA117 8 1 5 R7 V3 R6 6 380kΩ 3 VO = V3 – V2 + VX 21.1kΩ OPA27 Refer to Application Bulletin AB-001 for details. GAIN (V/V) R7 (kΩ) R6 (kΩ) 1/2 1/4 1/5 1.05 3.16 4.22 20 20 20 20kΩ INA117 8 1 5 OPA27 VX FIGURE 11. Summing VX in Output. FIGURE 10. Reducing Differential Gain. V2 2 R1 380kΩ 3 R3 380kΩ Refer to Application Bulletin AB-010 for details. (a) R2 380kΩ 6 VOUT = V3 – V2 V3 R5 21.1kΩ V2 V3 2 R1 380kΩ R2 380kΩ R4 20kΩ INA117 8 1 5 100pF 3 R3 380kΩ R6 5kΩ 6 VOUT = V3 – V2 R4 20kΩ R5 21.1kΩ A1 OPA27 R9 400kΩ 8 1 5 R10 10kΩ 100pF R6 5kΩ R7 10kΩ –V3 /20 100pF INA117 R8 10kΩ A2 OPA27 (b) R7 10kΩ VCM /20 A1 OPA27 FIGURE 12. Common-Mode Voltage Monitoring. INA117 SBOS154A 11 +9V 7 2 V2 380kΩ 380kΩ 7 VCM Range = +50V to +200V (VS ±9V) 3 V3 21.1kΩ (a) 2 6 380kΩ 25kΩ 25kΩ 5 6 20kΩ VO = V3 – V2 INA117 8 1 5 4 3 25kΩ –3V > VO > –6V swap A2 pins 2 and 3 for +4V > VO > 3V. INA105 25kΩ 1 4 –9V +9V 7 2 V2 380kΩ 380kΩ 7 VCM Range = –12V to +200V (VS = ±9V) 3 V3 6 380kΩ 2 25kΩ 25kΩ 5 6 21.1kΩ (b) INA117 8 VO = V3 – V2 20kΩ 1 5 4 3 25kΩ 25kΩ 1N4684 3.3V (V–) +3.3V 0V > VO > –6V swap A2 pins 2 and 3 for +4V > VO > 0V. INA105 10kΩ 1 4 –9V V2 2 380kΩ 380kΩ VCM Range = ±200V (VS = ±9V) V3 3 6 380kΩ 21.1kΩ 2 25kΩ 25kΩ 5 6 20kΩ VO = V3 – V2 INA117 (c) 8 1 5 3 R7 1MΩ 25kΩ 25kΩ INA105 1 13.7kΩ (VS = ±9V) Refer to Application Bulletin AB-015 for details. R8 1MΩ OPA602 FIGURE 13. Offsetting or Boosting Common-Mode Voltage Range for Reduced Power-Supply Voltage Operation. 12 INA117 SBOS154A +200V max V– V+ 4 2 7 380kΩ 380kΩ + – 3 6 380kΩ 21.1kΩ 20kΩ INA117 8 1 5 V– V+ 4 2 7 380kΩ 380kΩ + 6 – 3 380kΩ 21.1kΩ 20kΩ INA117 Repeat for each cell 8 1 eO = Cell Voltage 5 MUX V– V+ 4 2 7 380kΩ 380kΩ + – 3 6 380kΩ 21.1kΩ 20kΩ INA117 8 1 5 Cell Select V– V+ 4 2 7 380kΩ 380kΩ + – 3 6 380kΩ 21.1kΩ 20kΩ INA117 8 1 5 –200V max FIGURE 14. Battery Cell Voltage Monitor. INA117 SBOS154A 13 VS (200V max) +15V –15V 7 2 4 380kΩ 380kΩ R1 0.1Ω 3 6 380kΩ –0.1 (I1) I1 20kΩ 21.1kΩ INA117 8 1 Load A1 VIN 5 ILOAD = I1 – I2 +15V 7 +15V –15V 7 4 –15V 4 I2 2 380kΩ 100kΩ 380kΩ 2 R2 0.1Ω 5 10kΩ 6 6 3 380kΩ 3 –0.1 (I2) 10kΩ VO VO = I 1 – I2 = ILOAD 100kΩ 21.1kΩ INA106 20kΩ 1 INA117 8 1 5 VS (–200V max) FIGURE 15. Measuring Amplifier Load Current. V2 V3 2 3 R1 380kΩ R2 380kΩ R3 380kΩ 6 VOUT = V3 – V2 R5 21.1kΩ R4 20kΩ INA117 8 1 5 C1 R1 0.47µF 1MΩ OPA602 Refer to Application Bulletin AB-008 for details. FIGURE 16. AC-Coupled INA117. 14 INA117 SBOS154A PACKAGE OPTION ADDENDUM www.ti.com 6-Feb-2020 PACKAGING INFORMATION Orderable Device Status (1) Package Type Package Pins Package Drawing Qty Eco Plan Lead/Ball Finish MSL Peak Temp (2) (6) (3) Op Temp (°C) Device Marking (4/5) INA117AM NRND TO-99 LMC 8 20 Green (RoHS & no Sb/Br) AU N / A for Pkg Type INA117AM INA117BM NRND TO-99 LMC 8 20 Green (RoHS & no Sb/Br) AU N / A for Pkg Type INA117BM INA117KU ACTIVE SOIC D 8 75 Green (RoHS & no Sb/Br) NIPDAU-DCC Level-3-260C-168 HR INA117KU/2K5 ACTIVE SOIC D 8 2500 Green (RoHS & no Sb/Br) NIPDAU-DCC Level-3-260C-168 HR INA 117KU 2 INA117KU/2K5G4 ACTIVE SOIC D 8 2500 Green (RoHS & no Sb/Br) NIPDAU-DCC Level-3-260C-168 HR INA 117KU 2 INA117KUG4 ACTIVE SOIC D 8 75 Green (RoHS & no Sb/Br) NIPDAU-DCC Level-3-260C-168 HR INA117P ACTIVE PDIP P 8 50 Green (RoHS & no Sb/Br) NIPDAU N / A for Pkg Type INA117P INA117PG4 ACTIVE PDIP P 8 50 Green (RoHS & no Sb/Br) NIPDAU N / A for Pkg Type INA117P INA117SM NRND TO-99 LMC 8 20 Green (RoHS & no Sb/Br) AU N / A for Pkg Type INA117SM INA117SMQ NRND TO-99 LMC 8 20 Green (RoHS & no Sb/Br) AU N / A for Pkg Type INA117SMQ -40 to 85 -40 to 85 INA 117KU 2 INA 117KU 2 (1) The marketing status values are defined as follows: ACTIVE: Product device recommended for new designs. LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect. NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design. PREVIEW: Device has been announced but is not in production. Samples may or may not be available. OBSOLETE: TI has discontinued the production of the device. (2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free". RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption. Addendum-Page 1 Samples PACKAGE OPTION ADDENDUM www.ti.com 6-Feb-2020 Green: TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement. (3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature. (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device. (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device. (6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width. Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release. In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis. Addendum-Page 2 PACKAGE MATERIALS INFORMATION www.ti.com 16-Dec-2017 TAPE AND REEL INFORMATION *All dimensions are nominal Device INA117KU/2K5 Package Package Pins Type Drawing SOIC D 8 SPQ Reel Reel A0 Diameter Width (mm) (mm) W1 (mm) 2500 330.0 12.4 Pack Materials-Page 1 6.4 B0 (mm) K0 (mm) P1 (mm) 5.2 2.1 8.0 W Pin1 (mm) Quadrant 12.0 Q1 PACKAGE MATERIALS INFORMATION www.ti.com 16-Dec-2017 *All dimensions are nominal Device Package Type Package Drawing Pins SPQ Length (mm) Width (mm) Height (mm) INA117KU/2K5 SOIC D 8 2500 367.0 367.0 35.0 Pack Materials-Page 2 IMPORTANT NOTICE AND DISCLAIMER TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources. TI’s products are provided subject to TI’s Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI’s provision of these resources does not expand or otherwise alter TI’s applicable warranties or warranty disclaimers for TI products. Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated