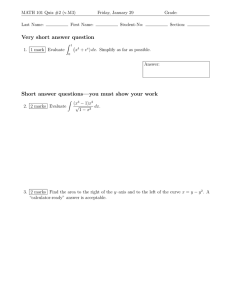

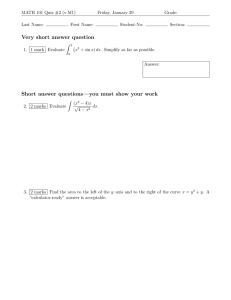

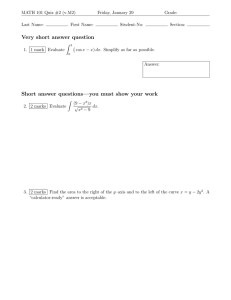

Final Exam (Take-Home) Summer - 2020 Student Name: Reg. ID: Subject: Computer Architecture & Org. Program: BS(CS) Instructor: Dr. Saad Ahmed / Ilyas Younus Max. Marks: 35 Q. No. 1 2 3 4 5 6 7 Total Marks Obtained Marks Department of Computer Science Please follow the instructions carefully: 1. Write your answers in a Word file and upload the file before the due date on LMS. 2. Write your name and registration ID on the first page of your Word file. 3. Answer scripts can be uploaded on LMS any time before its deadline. Therefore, do not wait for the last hour to avoid any unforeseen problems. 4. Submission of answer copy(ies) will be considered acceptable through LMS only. Therefore, do not submit your document through email or any other medium. 5. Use 12 pt. font size and Times New Roman font style along with 1-inch page margins. 6. Follow the requirements of the word limit and the marking criteria while writing your answers. 7. Provide relevant, original and conceptual answers, as this exam aims to test your ability to examine, explain, modify or develop concepts discussed in class. 8. Do not copy answers from the internet or other sources. The plagiarism of your answers may be checked through Turnitin. 9. Recheck your answers before the submission on LMS to correct any content or language related errors. 10. Double check your word file before uploading it on LMS to ensure that you have uploaded the correct file with your answers. ===================================================================== NOTE: Attempt ALL Questions. ===================================================================== Q # 1: Design a 16-bit memory of total capacity 8192 bits using SRAM chips of size 64 * 1 bit. This design must allow both 8-bit and 16-bit word accesses. Give the array configuration of the chips showing all required input and output signals for assigning this memory to the lowest address space. Explain your mapped memory setup. [ 6.0 Marks] Q. # 2: A system using interrupt-driven I/O that transfers data at an average of 8 KB/s on a continuous basis is connected to a storage device a. The interrupt processing time is about 100 ms (which includes the time to jump to the (ISR), execute it, and return to the main program). Consider if the interrupt is for every byte, what portion of processor time is used up by this I/O device. [ 2.0 Marks] b. Consider that the device has two buffers of 16-byte and it interrupts the microprocessor when one of the two buffers is full. Logically, interrupt takes longer to process, as 16 bytes must be transferred by the ISR. The processor takes about 8 ms for the transfer of each byte while executing the ISR,. Calculate what percentage of processor time is consumed by this I/O device in this case. [2.0 Marks] c. Assume now that a block transfer I/O instruction is available in the processor. This permits the associated ISR to transfer each byte of a block in only 2 ms. Calculate the percentage of processor time consumed by this I/O device in this case. [ 2.0 Marks] Q # 3(a): What will be the value of accumulator register if PC=900, PC=901, PC=902, PC=903, PC=904, PC=905, PC=906 and PC=907? [3.0 Marks] Partial list of operation codes 0111 _ Load AC from memory 0011 _ Store AC to memory 0110 _ Add to AC from memory 1001 _ Sub to AC from memory Memory 900 7999 901 3997 902 6998 903 9999 904 3997 905 6997 906 9996 907 9998 ._ 996 997 998 999 . 0001 0003 0004 0005 (b) A user program starts execution at t=0sec, a scanner interrupt is call at t=16 sec during interrupt handling another camera interrupt has been call at t=21 sec and returns at t=35 sec, at a same time another printer interrupt is call and return at=43sec to scanner interrupt handler. Scanner interrupt returns at t=53 sec. Calculate the total time required to process interrupt. [2.0 Marks] Q # 4: (a) With the help of six-bit unsigned adder-subtractor circuit, perform the following subtraction (also draw the circuit) [2.0 Marks] 010101- 011101 (b) Refer to the flow chart of Booth algorithm below, multiply +45 (multiplicand) by -32 (multiplier), where each number is represented using 7 bits. [2.0 Marks] (c) Given X=100010 (-30) and Y=111010 (-6) in twos complement notation compute division (-30/-6) using the follow chart of booth’s algorithm given below. [2.0 Marks] Q#5 a) Consider the contents of program counter be labelled by the symbol A1. The instruction stored in A1 has an address part A2. The operand is required to perform the instruction which is stored in the address A3 as memory word. An index register holds the value A4. Describe and show the relationship between these various quantities if the following addressing mode are used (a) direct; (b) indirect; (c) PC relative; (d) indexed? [2.0 Marks] b) What are design considerations when incorporating different cache replacement algorithms? [2.0 Marks] c) It is desired to have memory of 64Kbytes given that a 13-bit address bus is used to address memory location. Design the decoding architecture in order to access complete 64Kbytes memory also calculates address ranges for each memory chip. [2.0 Marks] Q # 6: a. Discuss basic operation of programmed I/O and Interrupt driven I/O. [2.0 Marks] b. In a computing system there are five phases of computation that is instruction fetch, Instruction decode, execute, memory access and write back. It has been recorded that is instruction fetch take 20 seconds, Instruction decode takes 40 seconds, execute takes 300 seconds, memory access takes 45 second and write back takes 25 second. Refer to the diagram above, if there are 5 instructions that need to be executed, calculate how much time can we save using pipelining also find the number of pipeline stages. [2.0 Marks] c. The Intel 8088 comprises of an execution unit (EU) and a bus interface unit (BIU) which form a two-stage pipeline. The BIU fetches instructions into a 4-byte instruction queue. The BIU also participates in address calculations, fetches operands, and writes results in memory as requested by the EU. The bus is free, If no such requests are outstanding, the BIU fills any vacancies in the instruction queue. When the EU completes execution of an instruction, it passes any results to the BIU (for memory or I/O) and proceeds to the next instruction. [2.0 Marks] 1. Assume the tasks performed by the BIU and EU take about equal time. Ignoring the effect of branch instructions, determine by what factor does pipelining improve the performance of the 8088? 2. Calculate again assuming that the EU takes twice as long as the BIU