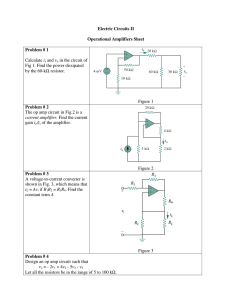

See discussions, stats, and author profiles for this publication at: https://www.researchgate.net/publication/335001568 Two Stage CMOS Operational Amplifier: Analysis and Design Article in SSRN Electronic Journal · August 2019 DOI: 10.2139/ssrn.3433181 CITATIONS READS 4 3,019 1 author: Shruti Suman K L University 28 PUBLICATIONS 113 CITATIONS SEE PROFILE Some of the authors of this publication are also working on these related projects: Temperature Sensors for ICs View project ANALOG AND MIXED SIGNAL VLSI DESIGN View project All content following this page was uploaded by Shruti Suman on 06 August 2019. The user has requested enhancement of the downloaded file. Mody University International Journal of Computing and Engineering Research 3 (1), 2019, 40-44 http://www.publishingindia.com/micer Two Stage CMOS Operational Amplifier: Analysis and Design Two Stage CMOS Operational Amplifier: Analysis and Design Shruti Amplifier: Suman Two Stage CMOS Operational Analysis and Design Shruti Suman Department of Electronics and Communication Engineering, Koneru Lakshmaiah Education Department of Electronics and Communication, Shruti Suman Foundation (Formerly: K L University), Guntur, Andhra Pradesh, India. Engineering, Koneru Lakshmaiah Education Department ofshrutisuman23@gmail.com Electronics and Communication, Email: Foundation,Koneru Guntur,Lakshmaiah Andhra Pradesh, India. Engineering, Education Email: shrutisuman23@gmail.com Foundation, Guntur, Andhra Pradesh, India. Email: shrutisuman23@gmail.com Abstract: This paper describes analysis design of 2-stage operational (Op A Amp). The Abstract: This paper describes analysis and designand of 2-stage II. TCMOS wo Stage CMOS amplifier Operational mplifier designed circuit operates at 3.3 V of supply voltage and at tsmc 0.35 μm CMOS technology. The performance CMOS operational amplifier (Op Amp). The designed circuit Abstract: This paper describes analysis and design of 2-stage CMOS operational amplifier (Op Amp). The parameters such as:gain, phase margin, GBW, ICMR, Slew Rate, Offset, CMRR, output etc. alsoof have operates at 3.3 Vcircuit of supply voltageatand 0.35 μm CMOS Op Amps are most important spine swing for analog designed operates 3.3atVtsmc of supply voltage and at tsmc 0.35 μm CMOS technology. Thedesigning performance been The analyzed simulation whichsuch isGBW, carried out using Cadence Virtuoso Tool. TheonOp-Amp is designed to DC technology. performance parameters as: ICMR, gain, circuit, andOffset, performance relies data transmission and parameters suchafter as:gain, phase margin, Slew Rate, CMRR, output swing etc. also have display aGBW, unity gain frequency of 7.85 andout exhibits a gain of Virtuoso 86.23 dB Tool. with aThe 49°Op-Amp phase Obtained phase been margin, ICMR, Slew Rate, Offset, CMRR, The symbolic representation of margin. a 2is stage Op to Amp is analyzed after simulation which is MHz carried usinggain. Cadence designed resultsaetc. also agree with theoretical predictions. outputdisplay swing also have been analyzed after unity gain frequency of 7.85 MHzsimulation and exhibits arevealed gain of by 86.23 dBFig. with using 1. a 49° phase margin. Obtained alsoout agree with theoretical predictions. whichresults is carried using Cadence Virtuoso Tool. The OpPrincipal part of Op Amp is differential amplifier which has two Scaling anda differential amplifier, of Stability, Amp isKeywords: designed to display unity gain frequency 7.85 Two stage operational amplifier. inputs i.e. upsetting and non-reversing voltages which results in MHzKeywords: and exhibitsScaling a gain of 86.23 dB with aamplifier, 49° phaseStability, margin. Two stage operational amplifier. and differential yielding of differential voltage or current [12]. Obtained results also agree with theoretical predictions. I. INTRODUCTIO N I. Scaling INTRODUCTIO Keywords: and differential amplifier, Stability, Two N stage operational amplifier. The operational amplifier (Op Amp) is surely one of the maximum beneficial gadgets in electronic industry The operational amplifier (Op Amp) is surely one of[1-4]. the OpAmps are most useful electronic devices these[1-4]. days, maximum beneficial gadgets in electronic industry I. Introduction used drastically signalelectronic conditioning, filtering OpAmps are mostfor useful devices these and days,for execution of mathematical operations [5-7]. Op Amp used drastically for signal conditioning, filtering and for is The operational amplifier (Op Amp) is surely one of the basically differential amplifier and output signal execution of mathematical operations [5-7]. Op Amp isis maximum beneficial gadgets in electronic industry [1-4]. nothing differential however difference ofand the output two input signals basically amplifier signal is Op Amps are most useful electronic devices these days, used implemented at difference the excessive terminals nothing of theimpedance twoforinput signals drastically for however signal conditioning, filtering and execution of magnified by using a steady benefit [8]. implemented at the excessive impedance terminals Fig. 1: Symbolic Diagram of a Two Stage Op Amp mathematical operations [5-7]. Op Amp is basically differential Fig. 1: Symbolic Diagram of a Two Stage Op Amp The design of Op Ampsbenefit basically supply magnified by using a steady [8]. considers, amplifier and output signal is nothing however difference of Fig. 1: Symbolic Diagram of a Two Stage Op Amp voltage and channel lengths of transistor with era of Theinput design of implemented Op Amps basically considers, supply the two signals at the excessive impedance CMOSand technology with tradeoff among velocity, energy, voltage channel lengths ofbenefit transistor era of terminals by using steady [8]. with gainmagnified and some otheratradeoff parameters which signifies CMOS technology with among velocity, energy,the performance [9-10]. The gain design of Op Amps basically considers, voltage and some other parameters whichsupply signifies the Nowadays high gain in Amp is technology for various performance [9-10]. and channel lengths of transistor withOp era of CMOS applications also optimizing has high gain inenergy, Op various Amp isparameters for with Nowadays tradeoff among velocity, gain and somevarious other become mandatory, which results in increase in slew rate applications also optimizing various[9-10]. parameters has parameters which signifies the performance for increase in current [11]. become mandatory, which results in increase in slew rate Nowadays high gain inremaining Op Amp for of various applications also the paper includes few forFramework increase inof current [11]. ispart optimizing various parameters has become mandatory, which sections: Section II of this work talks about the two-stage Framework of remaining part of the paper includes few amplifier design III for segment audits thethe 2 stage CMOS results in increase in slew increase in current [11]. sections: Section IIand ofrate this work talks about two-stage Op Ampdesign schematic plan, specifications and discussion on amplifier and III segment audits the 2 stage CMOS Framework of remaining part of the includes fewbeen sections: calculation of formula for paper designing have done. Op Amp schematic plan, specifications and discussion on SectionArea II ofIV thisexhibits work talks about the two-stage amplifier the simulation results, supported calculation of formula forthe designing have been done. design and III segment audits 2 stage CMOS Op Amp bygraphs and tables for advanced methodology. V section Area IV exhibits the simulation results, supported schematic plan, specifications and discussion on calculation includesand scaling and lastmethodology. section finishes up the bygraphs tableseffects for advanced V section of formula for designing have been done. Area IV exhibits the work with conclusion. includes scaling effects and last section finishes up the simulation results, supported bygraphs and tables for advanced Fig. 2: Stage CMOS Op-Amp work with II. Vconclusion. TWO STAGE CMOS OPERATIONAL methodology. section includes scaling effects and last section Fig. 2: Stage CMOS Op-Amp The following Fig. block is used to change the differential 2: Stage CMOS Op Amp MPLIFIER finishes up with conclusion. II.the work TA WO STAGE CMOS OPERATIONAL sign produced by the main square into a solitary finished Op Amps A areMPLIFIER most important spine for designing of The following block is used to change the differential adaptation [12]. Much of the time the increase given analog performance on data sign produced by the main square into a solitary finishedby Op Amps circuit, are mostand important spine forrelies designing of the information adequate transmission and DC gain. The symbolic representation of adaptation [12]. Muchstages of the isn't time the increase and given extra by Article can berelies accessed analog circuit, and performance on online data at http://www.publishingindia.com enhancement is stages required which is produced a 2 stage Op-Amp is revealed by using Fig. 1. the information isn't adequate and extraby transmission and DC gain. The symbolic representation of intermediate stage [13]. part of isOp Amp isbydifferential which enhancement is required which is produced by a Principal 2 stage Op-Amp revealed using Fig. amplifier 1. has two inputs i.e. upsetting and non-reversing voltages intermediate stage [13]. Principal part of Op Amp is differential amplifier which III. WORKING OF THE CIRCUIT of differential voltage voltages or current which has two results inputs in i.e.yielding upsetting and non-reversing III. WORKING OF THE CIRCUIT [12]. Two Stage CMOS Operational Amplifier: Analysis and Design 41 The following block is used to change the differential sign produced by the main square into a solitary finished adaptation [12]. Much of the time the increase given by the information stages isn’t adequate and extra enhancement is required which is produced by intermediate stage [13]. Output pole, P2 = - g m6 CL (5) Z1 = g m6 Cc (6) RHP zero, III. Working of the Circuit Fig. 2 is equivalent to typical CMOS Op Amp, includes three subsections: differential gain stage with next gain stage and bias stage [14]. CMR (Positive), 1 Ê I5ˆ 2 = V in(max) V DD Á ˜ - ÍÎV T 03˙˚ (max) + V T 1(min) Ë b 3¯ The primary phase of Op Amp is differential amplifier made up with transistors M1, M2, M3, and M4. This is basically a current mirror (CM) with active type of load utilized here has Fig. 2 is equivalent three particular preferences [15]. to typical CMOS Op Amp, includesCMR (-Ve), three subsections: differential gain stage with next gain The second stage stage used and to deliver high bias stage [14].gain to the amplifier and made up with of transistors M5 and M6. V in (max) V DD I5 3 (7) (7) 1 2 V T 03 (max) V T 1(min) 1 Ê ˆ2 CMR (-Ve),= V + I 5 V in(min) SS Á ˜ + V T 1(max) + V DS 5( sat ) Ë b 1¯ The primary phase of Op Amp is differential amplifier made up with transistors M1, M2, M3, and M4. This is The biasing circuit stage of amplifier is accomplished with basically a current mirror (CM) with active type of load transistors M5, M6, M7, and M8. utilized here has three particular preferences [15]. I5 Voltage V condition), V (Saturation The second stage used to deliver high gain to the V 1 amplifier made upCMOS with of transistors Design Methodology forand 2-Stage Op AmpM5 and M6. (8) 1 2 in (min) The biasing circuit stage of amplifier is accomplished transistors M5, M7, andthe M8.amplifier: Following are the with specifications for M6, designing V DS 5 ( sat ) T 1(max) SS Ê 2 I DS ˆ Voltage (Saturation condition), V DS ( sat ) = Á Ë b ˜¯ Process = 0.35 μmDesign Methodology for 2-Stage CMOS Op Amp Leff = 1.4 μm Following are the specifications for designing the amplifier: VDD = 3.3 V Process = 0.35 μm VSS = 0 V Leff = 1.4 μm Slew Rate = 10 V/μsec VDD = 3.3 V Product of gain and bandwidth (GB) = 10 MHz VSS =0V (8) V DS 2I DS ( sat ) 1 2 1 2 (9) (9) Slew Rate = 10 V/μsec Load capacitance Product = 2 pF of gain and bandwidth (GB) = 10 MHZ. = 2 pF ICMR + Vin (max) =Load 2.7 capacitance V ICMR+ Vin(max) = 2.7 V ICMR – Vin (min) =ICMR-)V 0.4 V in(min) = 0.4 V Equations used for designing: Equations used forSlew designing: rate, Slew rate, SR I C (1) 5 C I5 Gain for 1st stage, SR = (1) Cc A Gain for 1st stage, V1 g g ds 2 g m 2gain, AVSecond-stage 1 = g ds 2 + g ds 4 Second-stage gain, Fig. 3: Schematic of 2-Stage OpAmp ds 4 (2) AV 2 g g m6 AVGain-bandwidth, 2 = g ds 6 + g ds 7 Gain-bandwidth, (2) m2 g g ds6 (3) m6 g ds7 (3) GB gm2 GB = Output pole, Cc g C m2 (4) C 2 g C m6 (5) L RHP zero, g AC Analysis IV.phase Simulation Outcomes For this, gain and margin analysed with initial frequency 1 Hz and stopping Frequency 10 MHz. AC Analysis Results of AC analysis are: For this, gain and phase analysed with=7.85 initial frequency Product of gain margin and bandwidth (GBW) 1 Hz and stopping Frequency 10 MHz. MHz (4) P Fig. 3: Schematic of 2-Stage Op Amp IV. SIMULATION OUTCOMES (6) Phase margin = 49° Resultsof AC are: Gainanalysis = 86.23 dB 3dBof frequency = 410 Hz ∑∑ Product gain and bandwidth (GBW) = 7.85 MHz CMRR = 93 dB 42 Mody University International Journal of Computing and Engineering Research Volume 3, Issue 1, 2019 ∑∑ Phase margin = 49° DC Analysis ∑∑ Gain = 86.23 dB By the DC analysis we calculate ICMR range and input-output offset voltage. For this sweep the DC voltage from 0 to 3.3 Volt. The obtained offset and ICMR range are: ∑∑ 3 dB frequency = 410 Hz ∑∑ CMRR = 93 dB ∑∑ Input offset = 5 μV ∑∑ Output offset = 0.1 mV ∑∑ ICMR range = 0.19 V - 3.1 V Fig. 7: Analysis of Slew Rate Fig. 4: AC Analysis Fig. 4: AC Analysis Fig. 4: AC Analysis Fig. 4: AC Analysis Fig. 4: AC Analysis Fig. 7: Analysis of Slew Rate Fig. 7: Analysis of Slew Rate TABLE I: COMPARISON IN E XITING STAGE CMOS OP AMPAND MODIFIED TWO TABLE I: COMPARISON IN E XITING AND MODIFIED TWO TABLE I: COMPARISON IN E XITING M ODIFIED TWO STAGE CMOS OP AAND MP of Fig. 7: Analysis Slew Rate Parameters Existing Modified Fig. 7: Analysis of Slew Rate STAGE CMOS AMP 3.3Modified Power supply 5Existing VOPIN V MODIFIED TWO Parameters TABLE I: COMPARISON E XITING AND Parameters Load capacitance Power supply (CL) 10Existing pF 2 Modified pF 5inVE STAGE CMOS P A3.3 MP Table I: Comparison xitingOand MV odified Two Stage Gain 77.249 dB 86.23 dB Power supply Parameters 5 pF V 3.3 CMOS O p A mp Load capacitance (CL) 10 2 pF Existing V Modified Phase 53.46° 49° Load capacitance (CL) 10 pFdB 5 V 2 pFdB 3.3 V Gainmargin 77.249 86.23 Power supply Parameters Existing Modified GBW 8.6 MHz 7.85 MHz Gain dB 10 pF86.23 Phase margin 53.46° 49° dB 2 pF Load capacitance77.249 (C L) Power supply 5 410 V Hz 3.3 V 3Phase dB freq. 1.3 KHz margin 53.46° 49° GBW 8.6 MHz 77.249 7.85 MHz 86.23 dB Gain dB Load capacitance (CL) 10 pF 2 pF W1=W2 12 4.2 GBW 8.6 KHz MHz 53.46° 3 dB freq. 410 MHz Hz 86.23 49° dB GainPhase margin 1.3 77.249 7.85 dB W3=W4 23 2.8 3W1=W2 dB freq. 1.3 KHz 410 Hz 12 GBW 8.6 MHz4.2 7.8549° MHz Phase margin 53.46° W5=W8 20 14 Fig. 5: Waveforms of Transient Analysis W1=W2 12 8.6 4.2 7.85 W3=W4 23 GBW 3 dB freq. 1.3MHz KHz2.8 410 MHz Hz W6 195 19.4 3 dBW1=W2 freq. 410 W3=W4 23 1.3 KHz 2.8 W5=W8 20 12 14 4.2Hz Fig. 5: Waveforms of Transient Analysis W7 90 55 Fig. 5: Waveforms of Transient Analysis W1 = W2 12 4.2 W6 195 W5=W8 20 14 W3=W4 23 19.4 2.8 Fig. 5: Waveforms of Transient Analysis Input offset 6 mV 5 μV W4 23 2.8 W7 W3 =W5=W8 90 55 20 19.4 14 W6 195 Fig. 5: Waveforms of Transient Analysis Output offset 10 mV 0.1 mV W5 = W8 20 14 195 5 55 19.4 Input offsetW6 6 mV μV W7 90 Positive slew rate 10.4 V/μsec 10.6 V/μsec W6 195 19.4 W7 90 0.1 55 Outputoffset offset 10 mV Input 6 mV 5 μV Negative slew rate 9.4 V/μsec 9.7 W7 90 V/μsec 55 Input 6 mV Positive slew rateoffset 0.9-3.27 10.4 10.6 Output offset 10V/μsec mV 0.1V/μsec ICMR range V 0.19-3.1 VmV 5 μV Input offset 6 mV 5 μV Output mV mV Negativeslew slew rateoffset 80.895 9.4 V/μsec 9.7 Positive rate 10.4 V/μsec1010mV 10.6 V/μsec0.1 CMRR dB 93 dBV/μsec Output offset 0.1 mV Positive V/μsec ICMRdissipation range 0.9-3.27 V10.4240 0.19-3.1 V10.6 V/μsec Negative slew rate slew rate 9.4µW V/μsec 9.7 Power 480 µWV/μsec Fig. 6: Output for ICMR DC Analysis Fig. 6: Output for ICMR Positive slew rate 10.4 V/μsec 10.6 V/μsec Negative slew rate 9.4 V/μsec 9.7 V/μsec CMRRNegative 80.895 93 Settling time µs dB 0.42 µs dB V ICMR range 0.9-3.27 V V/μsec 0.19-3.1 slew rate 0.4 9.4 9.7 V/μsec ICMR range 0.9-3.27 V 0.19-3.1 Powerswing dissipation 480 240 Output V µW 0-3.13 ICMR range 0-3.28 0.9-3.27 V93VµW CMRR 80.895 dB dB 0.19-3.1VV CMRR 80.895dB dB µW CMRR 93 dB dB Settling time 0.4 µs 0.42 µs 93 Power dissipation 480 µW80.895 240 Power dissipation 480 µW 240 µW Power dissipation 480 µW 240 µW Output swing 0-3.28 0-3.13 V Settling time 0.4Vµs 0.42 µs Settling timetime 0.4 0.42 µs Settling 0.4µs µs 0.42 µs Output swing 0-3.28 V 0-3.13 V Output swing 0-3.28VV 0-3.13 Output swing 0-3.28 0-3.13 VV By the DC analysis we calculate ICMR range and inputoutput offset voltage. this sweep the DC voltage from Output for ICMR DC Analysis Fig. 6: For 0 to 3.3 Volt. The obtained offsetfor ICMR range are: Fig. 6: Output ICMR Fig. 6:and Output for ICMR Input offset = 5 μV DC Analysis By the DC analysis we calculate ICMR range and inputOutput offsetFor = 0.1 DC Analysis outputoffset voltage. thismV sweep the DC voltage from DC ICMR 0.19 V-3.1 V ICMR By analysis we=calculate ICMR range andare: input0 tothe 3.3 Volt. Therange obtained offset and range 3 inputBy the DC analysis we ICMR range output offset voltage. this sweepcalculate the DC voltage from and Input offset =For 5 μV output offset voltage. For this sweep the DC voltage from 0 to 3.3 Volt. The obtained offset and ICMR range are: Output offset = 0.1 mV 0 to 3.3 Volt. The obtained offset and ICMR range are: Input offset = 5 μV ICMR range = 0.19 V-3.1 V Input Output offset = 0.1offset mV = 5 μV 3 Output ICMR range = 0.19 offset V-3.1 =V0.1 mV ICMR range = 0.19 V-3.1 V Two Stage CMOS Operational Amplifier: Analysis and Design 43 Reference Width for all transistors is mentioned in Table III. TABLE III: REFERENCE WIDTH ALL TRANSISTORS Table III: OF Reference Width of All Transistors Name Value W1=W2 4.2 Name Value W3=W4 2.8 W5=W8 W114= W2 4.2 W6 19.6 W355= W4 2.8 W7 W5 = W8 TABLE IV: VARIATION IN OP AW6 MP PARAMETERS WITH VARIATION IN LENGTH Parameter Gain Fig. 8: Result of CMRR Fig. 8: Result of CMRR Transient Results and Analysis GBW L = 0.35 W7 L = 0.7 L = 1.05 L = 1.4 dB dB 8.77 7.85 14 19.6 55 Table IV: V75.32 ariation Op Amp P arameters With Variation in 54.31 dB dB in83.46 86.23 Length 12.39 10 MHz Parameter L = 0.35 L = 0.7 L = 1.05 L = 1.4 MHz MHz MHz The negative (inverting) port of amplifier is connected 54.31 dB 75.32 dB 83.46 dB 86.23 dB with sinusoidal input of 1 mv amplitude with 1 MHz 3 dB freq. Gain 29 KHz 1.85 635 Hz 410 Hz Transient Results and Analysis frequency for input-output waveform. GBW 12.39 10 MHz 8.77 7.85 MHz KHz MHz MHz TABLE II: VARIATION IN OP AMP PARAMETERS WITH The negative (inverting) port of amplifier is connected Phase with 61° 51° 3 dB freq. 54° 29 KHz 1.8549° KHz 635 Hz 410 Hz VARIATION IN COMPENSATION CAPACITOR sinusoidal input of 1 mv amplitude with 1 MHz frequency for margin Phase margin 61° 54° 51° 49° Cc Phase Gain GBW 3 dB freq. input-output waveform. Margin VI. CONCLUSION Table II:1.4p Variation in Op Amp Parameters With Variation in 86.23 dB 354 Hz 6.86 MHz 52° VI.2-stage Conclusion The analysis of design specifications for CMOS Compensation Capacitor Op Amp including simulation results has done in this 1.3p Cc 1.4p 1.3p 1.2p 1.1p 1.0p 51° 86.23 dB 380 Hz 86.23 dB 410 Hz 7.33 MHz work. The mentioned results and graphs also depicted in analysis of design specifications the which The estimates the limits of scaling for several for 2-stage CMOS Op Phase Gain GBW 7.853 MHz dB freq.applications Amp including simulation and devices. Designed Op Amp results has high has done in this work. 1.1p 86.23 dB 448 Hz 8.19 MHz Margin48° gain circuit The for thementioned application like comparators. results and graphs also depicted in the which 1.0p52° 46° 86.23 86.23 dB 493 9 6.86 MHz MHz dB 354Hz Hz estimates the limits of scaling for several applications and REFERENCES 51°analysis of86.23 dB connect 380 Hz input 7.33 MHz devices. Designed Op Amp has high gain circuit for the For the slew rate a pulse to nonP. Allen,application and D. Holmberg, CMOS Analog Circuit like comparators. inverting with 1dB us pulse width and pulse7.85 period 49° terminal86.23 410 Hz MHz1. Design, 2nd ed., 1998. is 2 us. The obtained slew rate (SR) isdB= 10.6 V/μsec 448 Hz 8.19 MHz2. S. Suman, “Design of efficient ring VCO using nano 48°Positive 86.23 slew rate scale double gate MOSFET,” Mody University 46°Negative86.23 slew rate = 9.7 V/μsec References dB 493 Hz 9 MHz International Journal of Computing and Engineering 1.2p 49° Output swing = 0-3.13 V Research, vol. 2, no. 1, pp. 5-10, 2018. Settling time =rate 0.42 connect µs For the analysis of slew a pulse input to 3.nonAllen, and D. Holmberg, S. Suman, [1] K. G. P. Sharma, and P. K. Ghosh, “250 MHz CMOS Analog Circuit inverting terminal with 1 ms pulse width and pulse period is multiphase delay locked2nd loop for low power Design, ed., 1998. V. SCALING AND ITS CONSEQUENCES applications,” International Journal of Electrical and 2 ms. The obtained slew rate (SR) isS. Suman, “Design of efficient ring VCO using Computer [2] Engineering, vol. 7, no. 6, pp. 3323-3331, Scaling can be characterized by power dissipation, ∑∑ Positive slewfrequency, rate = 10.6 December, 2017. nano scale double gate MOSFET,” Mody University operational cost, V/μsec transistor numbers and size, 4. S. Yellampalli, and A. Srivastava, “A comparatoretc. However, there are challenges on production, cost ∑∑ Negative slew rate = 9.7 V/μsec Journal of Computing and Engineering of CMOS analog and mixed-signal based IDDQ testingInternational power, interconnect losses, etc. th Midwest Symposium on integrated circuits,” 48 Research, vol. 2, no. 1, pp. 5-10, 2018. We assumed ∑∑ Output swinghere: = 0-3.13 V (W/L)nmos ∑∑ Settling time = 0.42=µsfRef * (W/L)1 (10) Circuits and Systems, IEEE (2005). S. Suman, K. G. Sharma, and P. K. Ghosh, “250 MHz 5. Jhon, and[3] K. Martin, Analog Integrated Circuit Design, Wiley India Pvt. Ltd, 1997. multiphase delay locked loop for low power applica6. Vaishali, S. Suman, K. G. Sharma, and P. K. Ghosh, tions,” International Journal of Electrical and Computer “Design of ring oscillator based VCO with improved performance,” Innovative Systems Design Engineering, vol. 7, no. 6,and pp. 3323-3331, December Reference channel length = 1.4 um V. Scaling and Its Consequences Reference Width for all transistors is mentioned in table III. be characterized by power dissipation, operational can Scaling frequency, cost, transistor numbers and size, etc. However, there are challenges on production, cost power, interconnect losses, etc. 2017. [4] S. Yellampalli, and A. Srivastava, “A comparator-based IDDQ testing of CMOS analog and mixed-signal integrated circuits,” 48th Midwest Symposium on Circuits and Systems, IEEE, 2005. [5] Jhon, and K. Martin, Analog Integrated Circuit Design, Wiley India Pvt. Ltd, 1997. We assumed here: (W/L)nmos = fRef * (W/L)1 Reference channel length = 1.4 mm (10) 44 Mody University International Journal of Computing and Engineering Research [6] [7] [8] [9] [10] [11] View publication stats V. S. Suman, K. G. Sharma, and P. K. Ghosh, “Design of ring oscillator based VCO with improved performance,” Innovative Systems Design and Engineering, vol. 5, no. 2, pp. 31-41, 2014. DOI: 10.1109/ACCT.2015.127 H. Saini, and S. Suman, “Analysis of different single-stage amplifiers,” Mody University International Journal of Computing and Engineering Research, vol. 1, no. 2, pp. 100-103, 2017. S. Suman, and K. G. Sharma, “An improved performance ring VCO: Analysis and design,” Ciência e Técnica Vitivinícola, vol. 33, no. 12, pp. 2-16, 2018. S. Suman, K. G. Sharma, and P. K. Ghosh, “Design of PLL using improved performance ring VCO,” in International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT), pp. 34783483, Chennai, India, March 2016. S. Suman, K. G. Sharma, and P. K. Ghosh, Voltage Controlled Ring Oscillators: Design Prospective and Applications, LAP LAMBERT Academic Publishing, January 2018. S. Suman, K. G. Sharma, and P. K. Ghosh, “Performance analysis of voltage controlled ring oscillators,” in Volume 3, Issue 1, 2019 S. Satapathy, Y. Bhatt, A. Joshi, and D. Mishra, (eds.), Proceedings of the International Congress on Information and Communication Technology (ICICT), Advances in Intelligent System and Computing (AISC), vol. 439, ch. 4, pp. 29-38, Springer, Singapore, 2016. [12] R. J. Baker, H. W. Li, and D. E. Boyce, CMOS Circuit Design, Layout and Simulation, IEEE Series on Microelectronic Systems, IEEE Press, 2003. [13] A. Yadav, “Design of two-stage CMOS Op-Amp and analyze the effect of scaling,” International Journal of Engineering Research and Applications (IJERA), vol. 2, no. 5, pp. 647-654, September-October 2012. [14] S. Suman, “Design of two stage CMOS comparator with improved accuracy in terms of different parameters,” Mody University International Journal of Computing and Engineering Research, vol. 2, no. 2, pp. 64-67, 2018. [15] P. Kakoty, “Design of a high frequency low voltage CMOS operational amplifier,” International Journal of VLSI Design & Communication Systems (VLSICS), vol. 2, no. 1, pp. 73-85, March 2011.