2012, ISSCC, 1.5W 10V-Output Class-D Amplifier Using a Boosted Supply from a Single 3.3V Input in Standard 1.8V3.3V 0.18μm CMOS

advertisement

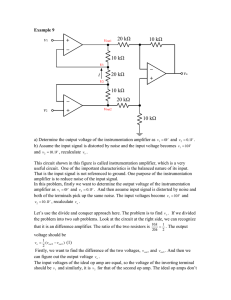

ISSCC 2012 / SESSION 5 / AUDIO AND POWER CONVERTERS / 5.2 5.2 A 1.5W 10V-Output Class-D Amplifier Using a Boosted Supply from a Single 3.3V Input in Standard 1.8V/3.3V 0.18μm CMOS Bert Serneels, Eldert Geukens, Bram De Muer, Tim Piessens ICsense, Leuven, Belgium Pressure to integrate more functionality and complexity on chip, to lower area and cost and to reduce time to market, drives IC technologies towards standard nanometer low voltage CMOS. A common practice to bridge the gap with highvoltage requiring applications, such as LED and MEMS drivers is to use costly extensions/options on the digital CMOS technology for tolerating voltages beyond the nominal supply. Solutions in mainstream CMOS were presented in the past using the principle of stacking devices [1]. The operation of these circuits, however, relies on the presence of multiples of the nominal supply voltage (e.g., 2VDD, 3VDD, …) for reliable operation. The generation of these voltages and the high supply rail itself externally will inevitably increase the bill of materials (BOM). In [2] a step-up converter has been proposed in a low-voltage CMOS technology. However, the conversion is performed by a switched-inductor stage followed by a floating capacitor configuration to handle a 10V output. This reduces the efficiency significantly and limits its use to low power applications only. For the generation of the intermediate voltages, on the other hand, solutions are reported in step-down converters. In [3] and [4] stacked regulators are used for generating the intermediate voltages. Both circuits operate directly from the high supply voltage. Extra startup circuits are thus required to ensure that devices are not overstressed during power-on. In this paper, a complete high-voltage concept is presented, designed in a lowvoltage CMOS technology, using only the nominal voltage as input. A test chip has been developed with an inductive DC-DC converter generating a 10V output from a single 3.3V input in a standard 1.8V/3.3V 0.18μm CMOS technology. The generated 10V serves as a supply for an on-chip Class-D output stage, able to deliver 1.5W. The 10V is protected by a custom high-voltage ESD clamp. Reliable operation of the low-voltage devices is guaranteed, including process, power supply and temperature variations, without the need for special startup circuits. Figure 5.2.1 shows a schematic of the asynchronous inductive DC-DC converter. Two main parts can be distinguished in the schematic: the high-voltage switch with its biasing circuitry and the control block. An on–off control scheme is used. The converter switches at a fixed clock frequency of 1MHz with a fixed duty cycle of 87.5%. The duty cycle can be cut by a soft start circuit during startup and by a current limit circuit. One clock cycle contains two phases. In one phase, the switch is closed and pulls one side of the inductor to ground. Energy is building up in the inductor. In the next phase the switch is opened and the energy is transferred to the output. Due to the diode threshold and process variations in the control block, the voltage across the switch can reach 11V. The switch can tolerate the 11V by using 5 stacked 3.3V isolated nMOS transistors. Transistor MN1 is directly driven by the control block via a tapered buffer. The switch is closed by using the 3.3V supply, which is applied to all gates via transistors MLB1, MLB2 and MLB3 in the local bias circuit. To protect the stacked nMOS transistors when the switch is opened, 5.0, 7.5 and 10V should be applied at the gates of MN3, MN4 and MN5, respectively. Multiples of 2.5V are taken to provide sufficient headroom for process and temperature variations and to catch transient voltage spikes over the 3.3V MOS terminals. However, at startup, these voltages are not present. To open the switch without any reliability issues, the intermediate voltages should follow the generated 10V supply. This process is performed by the global bias circuit. Through two matched resistor networks, nodes are generated with equally divided voltages. Mirroring these nodes to a class AB output stage, removes the MOS Vt voltage variation. The generated intermediate voltages 5 and 7.5V vary only with the temperature dependency of 94 • 2012 IEEE International Solid-State Circuits Conference the resistor network and follow relatively the voltage on the 10V supply. The transistors in the Class AB output structure are biased in the sub-threshold region for a low output impedance. Moreover, this limits the DC current of the global bias circuit to 60μA. The 10V output of the inductive converter serves as the supply for a switching output stage. Figure 5.2.2 shows a schematic representation of the Class-D amplifier with its biasing circuits. The 10V rail is protected by a high voltage, custom ESD clamp. The Class-D amplifier is comprised of 5 stacked, isolated pMOS and nMOS transistors in the pull up and pull down network respectively, to cope with process and temperature variations and fast switching transients. The local biasing scheme is based on [5] and requires the intermediate voltages 2.5, 5.0 and 7.5 for reliable operation. These voltages are generated from the 10V supply, like the global bias circuit in the inductive converter. During startup of the converter, the Class-D amplifier is set in tri-state via transistors MN1 and MP1. The 10V rail is gradually built up and the intermediate voltages follow relatively. Therefore, device reliability in the Class-D amplifier is not compromised. The 10V ESD clamp is composed of 4 stacked 3.3V nMOS ESD clamps, each covering a 2.5V rail. The advantage of using an nMOS in the active region as an ESD clamp is the low holding voltage. During an ESD event, the intermediate voltages follow the ESD pulse. These voltages are connected to the 2.5, 5.0 and 7.5V rails of the global bias blocks on the test chip via pwell-DNW diodes. An equal spread of the ESD pulse over the stacked devices is obtained in this way, improving the ESD robustness of the circuits. A test chip is fabricated in a 0.18μm 1.8V/3.3V triple-well CMOS technology. The chip passes the 2kV HBM and the 200V MM tests. Figure 5.2.3 shows the efficiency of the inductive DC-DC converter as a function of the output power for a 10% variation on the 3.3V input voltage and 3 temperatures. The peak efficiency is 81% at an output power of 732mW for a 3.3V input voltage at 25°C. The maximum output power is 1.5W. Figure 5.2.4 shows the efficiency of the ClassD amplifier in function of its switching frequency for a 66Ω load. An efficiency of 97% is achieved for the Class-D amplifier. The combined efficiency (Class-D and DC-DC) equals 74%. The efficiency roll-off occurs at a switching frequency of 1.0MHz. Measured waveforms of the 10V generated supply, the output of the Class-D amplifier and the inductor current are shown in Fig. 5.2.5. The average output voltage of the converter is 9.9V. The Class-D amplifier achieves an output voltage swing of 9.6V for a 66Ω load, resulting in an output power of 350mW. The switching frequency is 20kHz. The inductor current waveform consists of bursts of one complete clock cycle of 1μs and one cycle where the duty cycle is cut, visualizing the on-off operation of the converter. An overview of the measurement results is given in Fig. 5.2.6. A micrograph of the test chip is shown in Fig. 5.2.7. The area of the DC-DC converter, Class-D amplifier, and ESD clamp combined equals 2.081mm2. The converters high-voltage nMOS switch occupies, together with its local and global bias circuits, 0.765mm2. For a measured on-resistance of 0.606Ω this results in 0.46Ωmm2. The presented high-voltage concept is scalable towards any output voltage within the well–substrate breakdown voltage of the used technology. References: [1] A. J. Annema, G. Geelen, and P. de Jong, “5.5V I/O in a 0.25μm CMOS Technology”, IEEE J. Solid-State Circuits, vol. 36, no. 3, pp.528-538, March 2011. [2] P. Li, L. Xue, D. Bhatia, and R. Bashirullah, “Digitally Assisted Discontinuous Conduction Mode 5V /100MHz and 10V/45MHz DC-DC Boost Converters with Integrated Schottky Diodes in Standard 0.13μm CMOS,” ISSCC Dig. Tech. Papers, pp. 206-207, February 2010. [3] S. Bandyopadhyay, Y. K. Ramadass, and A. P. Chandrakasan, “20μA to 100mA DC-DC Converter with 2.8 to 4.2V Battery Supply for Portable Applications in 45nm CMOS,” ISSCC Dig. Tech. Papers, pp. 386-387, February 2011. [4] S. Rajapandian, K. Shepard, P. Hazucha, and T. Karnik, “High-Voltage Power Delivery Through Charge Recycling,” IEEE J. Solid-State Circuits, vol.41, no. 6, pp. 1400-1410, June 2006. [5] B. Serneels, M. Steyaert, and W. Dehaene, “A 237mW aDSL2+ CO Line Driver in a standard 1.2V 130nm CMOS technology,” ISSCC Dig. Tech. Papers, pp. 524525, February 2007. 978-1-4673-0377-4/12/$31.00 ©2012 IEEE ISSCC 2012 / February 20, 2012 / 2:00 PM 5 Figure 5.2.1: Schematic representation of the inductive DC-DC converter. Figure 5.2.2: Schematic representation of the high-voltage Class-D amplifier and ESD protection. Figure 5.2.3: Efficiency of the inductive DC-DC converter. Figure 5.2.4: The efficiency of the Class-D amplifier alone and combined with the DC-DC converter in function of the Class-D switching frequency. Figure 5.2.5: Measured waveforms of the 10V supply rail, the output of the Class-D amplifier and the inductor current. Figure 5.2.6: Measurement results. DIGEST OF TECHNICAL PAPERS • 95 ISSCC 2012 PAPER CONTINUATIONS Figure 5.2.7: Die micrograph. • 2012 IEEE International Solid-State Circuits Conference 978-1-4673-0377-4/12/$31.00 ©2012 IEEE