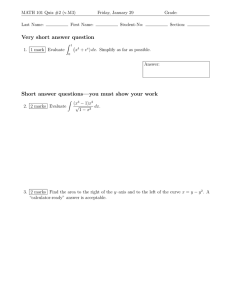

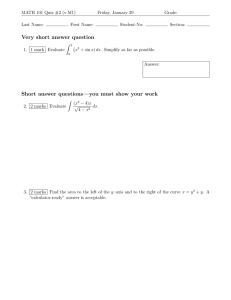

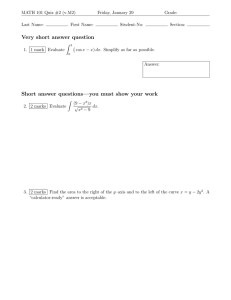

Coventry University INTI SOEAT Coursework Task Sheet Section A – To be completed by the student Family Name(s) Module Code 201CDE Forename(s) Student Card ID Number(s) Submit via Blackboard by 23:59 on Time taken (hours) (per student for group coursework) 13 November 2018 Lecturer Hand out date: Dr Lee Zhi Hou 15 October 2018 Module Code and Title Estimated Time (hours) Assignment type: No late work accepted. Extensions allowed only in extenuating circumstances. It is important that the work submitted is an individual effort. The penalties for plagiarism are severe. Full details on Faculty coursework policy and procedures are available at https://students.coventry.ac.uk/EC/Pages/Procedures.aspx % of Module Mark 15 Individual 25% 201CDE Analogue and Digital Electronics 2 Assignment No. / Title CW#2 Digital Coursework Section B – To be completed by assessor Marks breakdown (or on separate sheet) Part A: Sequential counter design and simulation Part B: VHDL counter and simulation Assessor’s signature Max 35 Awarded 15 Total 50 Total Internal moderator’s signature This section may be used for feedback or other information Learning outcomes assessed 1. Analyse and design synchronous sequential systems. 2. Model digital systems for simulation and synthesis using an HDL. Assessment criteria The work will be assessed against approved marking scheme. A perfectly correct technical solution presented to high professional standards with commentary and insights including detailed references and demonstrating additional research can expect to be awarded > 80%. Marks will be lost for errors, missing sections, poor presentation and lack of detail in analysis and commentary. Task details For this assignment you are required to design and test a sequential digital circuit with a unique specification based on your Student Identity Number (SID). Your work should be submitted to the Blackboard as a single pdf document by 23:59 on the day of the deadline. The file name should be “your SID number_your name_CW2” with the extension .pdf. Failing to follow this instruction will result in minor mark deduction. The assignment is assigned to be completed with the National Instruments Multisim simulator and Quartus II/Xilinx ISE VHDL simulator as installed in MSE labs. You may use alternative software but we are not able to support it. You should prepare your document by using this task sheet as a template which is then converted to pdf. Take care to ensure any image content is clear after conversion. Enter your student identification number (S.I.D.) in the grid below. The individual digits of this are used in the specifications that follow. In all cases if a specific digit is a ‘0’, it should be interpreted as if a ‘10’. A B C D E F G Part A: Sequential counter design and simulation [35 marks] Design a dual-mode sequential counter according to the unique specification that follows. This should be done using the classical design approach incorporating state transition diagram, state/transition tables and excitation maps as covered in the 201CDE classes. In first mode, the state machine is a binary up counter that begins at ‘0’ and proceed to count up, through all intermediate values to the maximum single digit value present in your SID. Once the counter reaches the maximum output it will wrap around to ‘0’ and begin again. The counter has an output function which is at logic ‘1’ when the current count corresponds to any single digit value that is present in your SID, else the output is ‘0’. In second mode, the state machine is a S.I.D. display that output the S.I.D. in sequence from digit A to digit G. The output function of the counter in this mode in always at logic ‘1’. The counter has a synchronous, active-low reset, which, when active, will initialize the count to the value of digit G in your SID in both modes. If digit F in your SID is an even number, you should design the counter using JK flip-flops as memory storage elements, else, you should employ D-type flip-flops. To document the design you should include the following as a minimum requirement: i. ii. iii. iv. v. State diagram [5 marks] State transition table [5 marks] Excitation Karnaugh’s maps and flip-flop input Boolean functions [12 marks] Output Karnaugh’s map and Boolean function [3 marks] Circuit implementation schematic [3 marks] Once the design is complete you should enter it in Multisim and create a simulation to confirm the functional operation. The simulation does not have to be an exhaustive test but should illustrate the main behaviour specified for the counter. You are recommended to use a word generator and logic analyser combination to produce test results that are easily documented in the report. vi. vii. Circuit showing simulation arrangements [2 marks] Simulation results [5 marks] (Note: For further clarification to using Multisim Logic Analyzer, you may refer to the website: http://www.screencast.com/t/Ca6MQqUuVo) Part B: VHDL counter design and simulation [15 marks] Create a VHDL synthesis model for the same sequential counter behavior specified in Part A above. You should copy in the VHDL source code for the design with VHDL comments to explain relevant aspects of its operation. No additional commentary is expected. i. VHDL source code [8 marks] Finally, produce a simulation of your design on the Quartus II design software or Xilinx ISE design tool, or similar, to confirm the correct operation of the VHDL design. You should include a waveform diagram from the simulation with annotations to highlight the important features of the counter in operation. ii. Simulation results [7 marks]