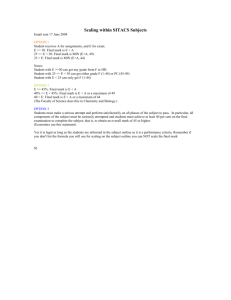

Course Academic Year 2018-2019 Technology of Integrated Systems Integrated Circuits Lesson 1 Jan Van Houdt vanhoudt@imec.be Technology of Integrated Systems - Integrated Circuits, Lesson 1 1 Prof.Dr.ir. Jan Van Houdt • Jan Van Houdt received a Ph.D. in Applied Sciences from the University of Leuven in 1994. During his PhD work, he invented the HIMOS™ Flash memory, which he transferred to several industrial production lines. In 1995 he received the title of Laureate of the Belgian Academy of Literature, Sciences and Fine Arts for his contributions to microelectronics. In 1999 he became responsible for Flash memory at imec and as such was the driving force behind the expansion of imec’s memory program. Today he is Scientific Director in the Memory Department, responsible for ferroelectrics research. He has published more than 300 papers in international journals and accumulated more than 250 conference contributions (incl. 42 invitations and 5 best paper awards). He has filed more than 70 patents and served on the program and organizing committees of 10 semiconductor conferences. In 2014 he received the title of IEEE Fellow for his contributions to Flash memory devices. In 2015 he obtained a teaching assignment as a guest professor in nanoscience and nanotechnology at the KU Leuven. His current activities are in exploratory memory devices and ferroelectric steep subthreshold slope transistors. Technology of Integrated systems IC Technology : Basic Part 1. 2. 3. 4. 5. Introduction to IC & Planar Technology Basic CMOS process steps Scaling of CMOS and issues Scaling of CMOS: from µm till 100nm (Microelectronics era) Scaling beyond 100nm (Nanoelectronics era) COURSE 2018-2019 Technology for Microelectronics MEE H09M6a 10 lessons Technologie van geintegreerde systemen MNN H05L0a Technology of integrated systems MNE + EMM H09M6a 10 lessons H06G0a 20 lessons 10 lessons o 2 lessons/week (Wednesday C300 00.81 & Thursday ELEC B91.100) o Technology of Integrated Systems/ Technologie van Geintegreerde Systemen: 20 lessons - Basics + Advanced o 10 lessons on IC technology (Prof. Van Houdt) and 10 lessons on IC stacking (Prof. Van Hoof) o First part of the IC technology course: “basics” : CMOS • H09M6a + H05L0a o Second part of the IC technology course “advanced” : memory, patterning • H06G0a + H05L0a Part 1: Lessons basics: 13/2, 14/2, 20/2, 21/2, 27/2 Part 2: Lessons advanced: 28/2, 6/3, 7/3, 13/3, (14/3) Part 3 (C. Van Hoof): remaining lessons References 1. Silicon VLSI technology, chapters 1 and 2 by Plummer, Deal and Griffin (see Toledo, in lesson IC2) 2. CMOS, Baker, Wiley-IEEE, 2011, available through imec and university library link 3. See also Springer-Verlag e-books through university library links. 4. Bits on chips, Harry Veendrick (www.bitsonchips.com) Technology of Integrated Systems, Part Integrated Circuits, Lesson 4 7 What is an IC ? In electronics, an integrated circuit (also known as IC, microcircuit, microchip, silicon chip, or chip) is a miniaturized electronic circuit (consisting mainly of semiconductor devices, as well as passive components) that has been manufactured in the surface of a thin substrate of semiconductor material. Integrated circuits are used in almost all electronic equipment in use today and have revolutionized the world of electronics. Intel Pentium4 Source: http://en.wikipedia.org/wiki/Integrated_circuit 8 Semiconductor Integrated Circuits changed our daily world • Analysis of key markets of IC’s – Wireless Networking – Cellular Phones – Digital Cameras and Audio Players – Automotive Electronics – Video Game Consoles – Digital TVs and Set-Top Boxes – DVD Players and Recorders – PCs and smartphone PDAs – RFID, Smartcards, and more 9 IC large part of microelectronics and semiconductor market Mainframe computers (1980s): ▸ 8-10% of the value consists of ICs Personal computers (1990s): ▸ 25-33% of the value consists of ICs Handheld devices (2000s) ▸ 40-50% of the value consists of ICs 10 Why studying IC technology? Very important technology : directly affects modern society Enabler of the microelectronic “Si” revolution low-cost, complex systems that have permeated nearly every aspect of everyday life Dramatic growth of integrated system size & complexity What has driven this industry? What has enabled this industry? How has it evolved? Learning : for future for other applications How will this industry further perform in the nano-age ? 11 INTRODUCTION Why Integrated Circuits ? Importance and need of Scaling ? Technology (vs lab-type experiments...) © IMEC 2013/ CONFIDENTIAL 12 WHY INTEGRATED CIRCUITS? What are the issues when making large electric/electronic systems? Take a look at the history of computers... © IMEC 2013/ CONFIDENTIAL 13 Development of computers Crucial inventions on device level (1) Micro relais 14 First computers: Harvard Mark I 1944 Harvard Mark 1 Computer Howard Aiken and Grace Hopper designed the MARK series of computers at Harvard University. The MARK series of computers began with the Mark I in 1944. Imagine a giant roomful of noisy, clicking metal parts, 55 feet long and 8 feet high. The 5-ton device contained almost 760,000 separate pieces. Used by the US Navy for gunnery and ballistic calculations, the Mark I was in operation until 1959 Harvard Mark 1 Computer http://inventors.about.com/library/blcoindex.htm 15 First computers: Harvard Mark I 1944 Harvard Mark 1 Computer The computer, controlled by pre-punched paper tape, could carry out addition, subtraction, multiplication, division and reference to previous results. It had special subroutines for logarithms and trigonometric functions and used 23 decimal place numbers. Data was stored and counted mechanically using 3000 decimal storage wheels, 1400 rotary dial switches, and 500 miles of wire. Its electromagnetic relays classified the machine as a relay computer. All output was displayed on an electric typewriter. By today's standards, the Mark I was slow, requiring 3-5 seconds for a multiplication operation. http://inventors.about.com/library/blcoindex.htm 16 Development of computers Inventions on device level (1) Micro relais (2) Vacuum tube 17 First computers: ENIAC 1948 What Was Inside The ENIAC? The ENIAC contained 17,468 vacuum tubes along with 70,000 resistors, 10,000 capacitors, 1,500 relays, 6,000 manual switches and 5 million soldered joints. It covered 1800 square feet (167 square meters) of floor space, weighed 30 tons, consumed 160 kilowatts of electrical power. There was even a rumor that when turned on the ENIAC caused the city of Philadelphia to experience brownouts, however, this was first reported incorrectly by the Philadelphia Bulletin in 1946 and since then has become an urban myth. http://inventors.about.com/library/blcoindex.htm The Eniac Computer 18 First computers: ENIAC 1948 In one second, the ENIAC (one thousand times faster than any other calculating machine to date) could perform 5,000 additions, 357 multiplications or 38 divisions. The use of vacuum tubes instead of switches and relays created the increase in speed, but it was not a quick machine to re-program. Programming changes would take the technicians weeks, and the machine always required long hours of maintenance. As a side note, research on the ENIAC led to many improvements in the vacuum tube http://inventors.about.com/library/blcoindex.htm The ENIAC, in BRL building 328 19 Development of computers Inventions on device level (1) Micro relais (2) Vacuum tube (3) Discrete transistors 20 TRANSISTOR INVENTION Bardeen Shockley Brattain 1947 first bipolar point-contact transistor 21 First Transistorized Computer:TRADIC 1954 Transistors, unfortunately, were substantially more expensive than vacuum tubes -- costing $20 as compared to $1 for a vacuum tube -- but the advantages still outweighed that one drawback. In January of 1954, supported by the military, engineers from Bell Labs built the first computer without vacuum tubes. Known as TRADIC (for TRAnsistorized DIgital Computer), the machine was a mere three cubic feet, a mindboggling size when compared with the 1000 square feet ENIAC hogged. TRADIC - The First Fully Transistorized Computer http://www.pbs.org/transistor/background1/events/sscomputer.html http://www.cedmagic.com/history/tradic-transistorized.html 22 First Transistorized Computer:TRADIC 1954 It contained almost 800 point-contact transistors and 10,000 germanium crystal rectifiers. It could perform a million logical operations every second, still not quite as fast as the vacuum tube computers of the day, but pretty close. And best of all, it operated on less than 100 watts of power. During two years of continuous operation only 17 of these devices failed, a vastly lower failure rate than Vacuum tube machines of the time. http://www.pbs.org/transistor/background1/events/sscomputer.html http://www.cedmagic.com/history/tradic-transistorized.html 23 WHY INTEGRATED CIRCUITS? What are the issues when making large electric/electronic systems? ▸ Performance ▸ Power ▸ Reliability ▸ COST WHY INTEGRATED CIRCUITS? What are the issues when making large electric/electronic systems? ▸ Performance ▸ Power ▸ Reliability ▸ COST ▸ Form factor (size) So far, only advantages on device level Micro relais Vacuum tube Discrete transistors Advantages in speed and power and (device-level) reliability, but limitations in COST reduction 26 SOME ISSUES NOT SOLVED BY CHANGING DEVICE LEVEL 27 INTEGRATED CIRCUITS Invention Key technology Transistor flavors Scaling 28 What led to the invention of the IC? “Seeing the light” Realization that all different components can be made in the same semiconductor material (transistors + passives R,C…) Realization that different devices can be made on the same substrate at same time (COST ) Realization that in-situ interconnect reduces (1) parasitics (SPEED/POWER) and (2) complexity (RELIABILITY/COST) Parellel invention of IC by : Jack Kilby (Texas Instruments, 1958) and Robert Noyce (Fairchild, 1959) (Robert Noyce later became the founder of Intel) 29 JACK KILBY’S FIRST IC It was a relatively simple device that Jack Kilby showed to a handful of co-workers gathered in TI's semiconductor lab 50 years ago -only a transistor and other components on a slice of germanium. Little did this group of onlookers know, but Kilby's invention, 7/16-by-1/16-inches in size and called an integrated circuit, was about to revolutionize the electronics industry. Texas Instruments' first IC 30 ROBERT NOYCE 1ST IC ON SI But over in California, another man had similar ideas. In January of 1959, Robert Noyce was working at the small Fairchild Semiconductor startup company. He also realized a whole circuit could be made on a single chip. While Kilby had hammered out the details of making individual components, Noyce thought of a much better way to connect the parts. That spring, Fairchild began a push to build what they called "unitary circuits" and they also applied for a patent on the idea. 31 INTEGRATED CIRCUITS Invention Key technology = PLANAR TECHNOLOGY Transistor Flavors Scaling 32 Planar technology : basic principles The fabrication of (electronic) devices to create functional structures (computing, communication, sensing...) ▸ On a planar substrate ▸ The structure is formed layer by layer ▸ For each step - a material layer is formed at some places and not at other places - where the layer will be or not is usually defined by photolithography - in most cases, the layer is uniformly formed (deposited or grown), and locally removed in a material etching step 33 Main steps Materials formation: ▸ Layer growth (e.g. oxidation of Si SiO2) ▸ Layer deposition (e.g. chemical vapor deposition or CVD) ▸ Implanting atoms (e.g. doping) ▸ Thermal steps (dopant activation/layer formation) Structure definition: ▸ Lithography : transfer of an optical pattern to a photosensitive layer (photoresist) ▸ Patterning: Etch (wet,dry), Chemical Mechanical Polishing 34 Example : diode fabrication p n Si substrate 1. Substrate (typically a Si wafer, e.g. p-type) 37 Example : diode fabrication SiO2 2. Growth of layer (e.g. SiO2 by oxidation of Si) / deposition of layer (e.g. CVD SiO2 deposition) 38 Example : diode fabrication photoresist 3. Deposition of photoresist = light sensitive layer 39 Example : diode fabrication A A’ AA’ 4. Desired pattern made on Mask (glass plate with local non-transparant metal coating) 40 5. Illumination of photoresist through mask 41 Example : diode fabrication 6. Development of resist : illuminated area’s are removed 42 Example : diode fabrication 7. Etch of active layer (wet/dry etch techniques) 43 Example : diode fabrication 8. active layer selectively removed 44 Example : diode fabrication 9. Removal photoresist 45 Example : diode fabrication Local structure formation w/o mask: Self aligned I/I 10. Ion-implant (e.g. P) 46 Example : diode fabrication n-Si SiO2 p-Si Structure so far 47 Example : diode fabrication n-Si SiO2 p-Si 11. Metal deposition 48 Example : diode fabrication n-Si SiO2 p-Si 12. Photoresist coating 49 n-Si SiO2 p-Si 13. Illumination trhough 2nd mask 50 Example : diode fabrication n-Si SiO2 p-Si 14. Develop Resist 51 Example : diode fabrication n-Si SiO2 p-Si 15. Etch metal 52 Example : diode fabrication n-Si SiO2 p-Si 16. “Final” Structure 53 PLANAR TECHNOLOGY DRIVING FACTOR: Main benefit of planar technology ▸ You can make 1 or 1E9 devices at the same time, using exactly the same steps as those to make a single device COST ! 54 Planar Technology Enabling factors: ▸ Device structure ▸ Material ▸ (Technology) 55 WHAT IS A MOSFET ? A MOSFET functions ideally as an electronically controlled SWITCH mechanical switch I current / no current MOSFET VG I Source Drain 56 How it was enabled? Typical electronic device : MOSFET ▸ Essentially a 2D (planar) device ▸ Different active layers are thin - Only upper surface layer of Si is active - Thin gate insulator - Thin gate electrodes ▸ Controlled by ▪ in-plane dimensions of the Silicon (W,L) • Control current levels ▪ normal (to plane) layer thicknesses • Control threshold voltages ▸ Process: - layer depositions (formation) thickness control - In-plane structuring lateral dimension control 57 How it was enabled? bipolar TOR is more complex but essentially similar : ▸ Thickness of layers controls voltages ▸ In plane dimensions control current levels 58 How it was enabled? Vacuum Tube : 3D device, + large (vertical) dimensions What would have been your memory stick made of w/o planar technology ? 59 THE SELECTRON TUBE Digital memory, Developed by RCA end of 1940’s The original 4096-bit Selectron was a 10-inch-long (250 mm) by 3-inch-diameter (76 mm) vacuum tube configured as 1024 by 4 bits. The smaller capacity 256-bit (128 by 2 bits) "production" device[ was in a similar vacuum tube envelope. It was built with two storage arrays of discrete "eyelets" on a rectangular plate, separated by a row of eight cathodes. The pin count was reduced from 44 for the 4096-bit device down to 31 pins and two coaxial signal output connectors. This version included visible green phosphors in each eyelet so that the bit status could also be read by eye. 256-bit Selectron tube 4096-bit Selectron tube 60 The material factor : Si Si is a “wonder” material ▸ Abundant element ▸ Can be grown in large crystals - Typically cylindrical ingots that are sawed into wafers - Flat and rigid substrates ▸ Semiconductor properties - P- and n-type by doping Si can be oxidized to become SiO2 ▸ Stable material (>< Ge) ▸ SiO2 is good dielectric - Gate dielectric - Insulating Although first working transistors were based on Ge, IC technology was built on Si SiO2 can also be deposited 61 Basic device structure essentially made of Si and SiO2 !! SiO2 PMD Silicide Poly-Si gate SiO2 spacer SiO2 isolation SiO2 gate insulator Si substrate 62 Enabling technology : Thin film deposition and lithography MOSFET = 2D “planar” device controlled by - in-plane dimensions of the Silicon (W,L) : control current levels - normal to plane layer thicknesses : control threshold voltages Enabled by advanced deposition techniques as ALD Enabled by Litho scaling resolution k1. © IMEC 2012 63 BEYOND CMOS - INTRODUCTION -2012 NA Technology vs lab science Important : what is a “technology” ▸ the strength of “planar” technology - concepts as self-alignment ▸ ”technology” vs. science - 1 working device is not yet a technology - A technology is making >1M-1B devices at the same time No longer only “classical” electronic IC ▸ MEMS (NEMS) - Optical (mirrors), Chemical (lab-on-chip), Sensors/actuators ▸ TV sets - CRT TFT flatscreen ▸ Others ! 64 INTEGRATED CIRCUITS Invention Key technology Transistor flavors Scaling 65 IC “device-type” technologies Many related technologies Bipolar, NMOS, CMOS : historic evolution CMOS is the main technology today: ▸ focus of this part of the course is on CMOS IC technology ▸ This is OK for “pure” logic IC’s ▸ (Vertical) Scaling route, also called “More Moore” But besides CMOS, also other components: - High Voltage, RF, Sensors, NVM As many functions as possible integrated on one chip = SoC (System-on-Chip) - also called horizontal scaling route, ”More than Moore” 66 Why CMOS got important ? 67 Why CMOS got important ? with resistive load Initial PMOS with depletion transistor load CMOS NMOS Driving force for change in invertor scheme ? Benefits? Drawbacks? 68 Why CMOS got important ? No static leakage in Complimentary CMOS POWER © IMEC 2010 / CONFIDENTIAL 69 INTEGRATED CIRCUITS Invention Key technology Transistor flavors Scaling © IMEC 2010 / CONFIDENTIAL 70 Continuous drive to increase the number of components in a system (or memory) What limits the number of devices (transistors) on a chip ? ▸ DIE SIZE ▸ POWER (cfr. CMOS) © IMEC 2010 / CONFIDENTIAL 71 What limits the DIE size ? ▸ Yield (number of defects/area) ▸ Interconnect length (performance (speed)... © IMEC 2010 / CONFIDENTIAL 72 Solution : SCALING SCALING of devices : making devices smaller + SCALING of die size : making die size larger ▸ e.g. by improvement of process control © IMEC 2010 / CONFIDENTIAL 73 What factors increase #TORs/Chip Device scaling © IMEC 2011 / CONFIDENTIAL Yield improvement 74 MOORE’S LAW Chip area per function : 2 every 2-3 years © IMEC 2011 / CONFIDENTIAL 75 Moore’s law dictates the scaling beat of IC industry #TORS/chip * 2 every 18 months Intel co-founder Gordon E. Moore © IMEC 2011 / CONFIDENTIAL Moore’s law has been driving this industry over time towards more complex circuits with increased performance. 76 76 TECHNOLOGY NODES ~ x0.7/node © IMEC 2011 / CONFIDENTIAL 77 Scaling of feature size (= technology node) © IMEC 2011 / CONFIDENTIAL 78 Scaling Size reduction by 1/1000 ! © IMEC 2011 / CONFIDENTIAL 79 SCALING BENEFITS 1) COST © IMEC 2011 / CONFIDENTIAL 80 It’s all about economics Average transistor price per year About 7 decades price decrease per transistor Source: WSTS/Dataquest/Intel Moore‟s Law is not (only) about scaling (shrinking); its primary objective is the economy of scale (performance and cost) © IMEC 2011 / CONFIDENTIAL 81 It’s all about economics Scaling: more at lower price Enables new markets ! Example: NAND Flash substitutes HD While cost of living increases, cost of electronic equipment in generally has decreased in absolute values despite major performance improvements © IMEC 2011 / CONFIDENTIAL 82 SCALING BENEFITS 1) COST 2) PERFORMANCE (SPEED) Cst field scaling B.Dennard 1974 3) POWER (/device) © IMEC 2011 / CONFIDENTIAL 83 MOORE’S LAW = 2 generations ! © IMEC 2011 / CONFIDENTIAL 84 © IMEC 2011 / CONFIDENTIAL Technology of Integrated Systems / GD/2009 85 The power of scaling Enormous progress made through scaling (i.e. making things smaller more and faster transistors on chip) Year 1971 2011 ratio Transistors 2.300 1.170.000.000 ~ 500.000 Speed (Hz) 10.800 3.600.000.000 ~ 360.000 Gate length (nm) 10.000 32 ~ 1/300 12 239 ~ 20 Area (mm2) 40 years of scaling Intel 4004 ▪ Minimum feature size scaled from 10mm to 32nm in 40 years © IMEC 2011 / CONFIDENTIAL Intel Core i7 86 SCALING & ROADMAPS Scaling did not come without effort Large R&D in SC industry ▸ Guided by ITRS Roadmaps © IMEC 2011 / CONFIDENTIAL 87 International Technology Roadmap for Semconductors (ITRS: www.itrs.net) The ITRS roadmap is a “guiding” vehicle used by the semiconductor industry It specifies the different device and technology parameters required to realize the scaled devices (with a pace according to Moore’s law), and by that specifies the critical issues and identifies problematic area’s that guide the technology research effort. 2010 Technology of Integrated Systems, Part I Integrated Circuits, Lesson 1 88 ITRS 2005 : example Wafer size scaling is another economic drive cost per wafer increases BUT cost per chip decreases 90 WAFER SCALING wafers larger cost/die decreases ▸ Process cost/wafer ~ cst ▸ More yielding dies/wafer but : ▸ technology for making high quality large substrates ▸ tool and fab cost increases Economy of scale.. 91 INCREASING ENTRY BARRIERS Manufacturing At each step, fab capacity is doubling and critical dimensions are shrinking R&D 3-5 B$ 0.1µ -> 32nm 25 20 R&D cost as % of revenue for each new generation 300 mm 15 1.5-2.5 B$ 0.5µ -> 0.13µ 10 200 mm 90 M$ 20µ-> 5µ 100-250 M$ 5µ-> 0.8µ Cost proportional to dimension 150 mm 100 mm 1980 5 0 1985 1990 1995 2000 2005 0.25 um 0.18 um 0.13 um 0.09 um Source : IC Insights, STMicroelectronics = annual depreciation MH, RDK - 2012 92 PRODUCTION TRENDS MH, RDK - 2012 93 Last 30 years scaling 94 SCALING ISSUES Happy microelectronic scaling days ended with advent of nanoelectronics (~100nm technology) Major scaling issues : POWER ▸ new materials replacing SiO2 and Si ▸ new device structures replacing conventional MOSFET 95 ALTERNATIVE WAYS OF SCALING Classical “Moore’s law” scaling is only 1 possibility Alternatives: ▸ More than Moore ▸ 3D ▸ Bottom Up 96 Moore ‘s Law & More More than Moore: Diversification Baseline CMOS: CPU, Memory, Logic More Moore: Miniaturization Analog/RF Passives Biochips Non-digital content System-in-package (SiP) 90nm 65nm 32nm Sensors Actuators Interacting with people and environment 130nm 45nm HV Power Embedding Functionality Information Processing Digital content System-on-chip (SoC) 22nm . . . V Scaling Beyond CMOS MH, RDK - 2012 97 NEW FUNCTIONALITIES OF IC’S Further evolution on system level scaling ON + OFF “chip” © IMEC 2011 / CONFIDENTIAL 98 3D VS 2D SCALING Going vertical solves litho scaling bottleneck - 3D stacking - True 3D (no longer “planar” processing !) © IMEC 2011 / CONFIDENTIAL 99 3D STACKING OF SI MEMORY two-layer stacked NAND Issues: •(large aspect ratio) cell penetration contacts by etching layers vertically through the upper level Si layers to the bottom active layer and their sequential filling with N-doped poly-Si and W •Good quality Si •Cost compared to chip-stacking ? © IMEC 2011 / CONFIDENTIAL Technology of Integrated Systems, Part I Integrated Circuits, Lesson 9 100 TRUE 3D BICS NAND FLASH © IMEC 2011 / CONFIDENTIAL 101 Different scaling ways in the NANO domain ▸ Traditional scaling = TOP DOWN - Deposit LARGE - Pattern FINE : litho & etch ▸ Alternative = BOTTOM UP - Build-up from nanoscale - “self-assembly” 102 The microelectronicsnanotechnology convergence Scaling down 1 mm Higher performance Microe lectron ics Nanotechnology Biolo istry , 1 nm sics y gy, Ph Chem New functions Scaling up 1960 1970 1980 1990 2000 2010 2020 2030 103 Why SC industry has been that successful? Invention of Integrated Circuit -Enabler = PLANAR technology : - Using same steps, one can generate 1 or 1B devices - Si/SiO2 is key material (Si took over from Ge!) Technology Scaling : MOORE’s LAW -Enablers: - Scaling laws : a scaled FET is still a FET (physics) - Technology: continuous litho developments ( smaller dimensions) + continuous process improvements (yield larger die sizes) - CMOS : only way for low power (U)LSI Key attributes of scaling: - Performance increase and more functions per chip - Economics: cost per TOR dramatically decreases ! We can make more things and at lower prices ! © IMEC 2011 / CONFIDENTIAL 104 Technology of Integrated systems IC Technology : Basic Part 1. 2. 3. 4. Introduction to IC & Planar Technology Basic CMOS process steps Scaling of CMOS and issues Scaling of CMOS: from um till 100nm (Microelectronics era) 5. Scaling beyond 100nm (Nanoelectronics era) Next lesson : how to build CMOS 2012 Technology of Integrated Systems, Part I Integrated Circuits, Lesson 2 106