Computer Systems I Lecture Notes - Digital Logic & Architecture

CSSE2010

Computer Systems I

Matthew Low

March 18, 2019

Abstract

Lectured by Peter Sutton.

Offered in Semester 1, 2019.

These notes are not endorsed in any way by the lecturer/lecturers, and are no substitute for lecture attendance.

Introduction to digital logic & digital systems; machine level representation of data; computer organization; memory system organization & architecture; interfacing & communication; microcontroller architecture and usage; programming of microcontroller based systems.

Contents

1 Introduction & bits, bytes & binary 2

1.1

Computer organisation . . . . . . . . . . . . . . . . . . . . . . . .

2

2 Logic gates 3

2.1

Digital logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3

3 Binary arithmetic 4

4 Combinational logic

5 Flip-flops

6 Sequential circuits 1 - shift registers 4

6.1

Combinational vs sequential circuits . . . . . . . . . . . . . . . .

4

6.2

Serial to parallel and parallel to serial conversion . . . . . . . . .

5

6.3

Bidirectional shift register . . . . . . . . . . . . . . . . . . . . . .

6

6.4

Universal shift register . . . . . . . . . . . . . . . . . . . . . . . .

7

7 Sequential circuits 2 - counters 7

7.1

Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7

7.2

State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8

4

4

1

CSSE2010 Computer Systems I Matthew Low

7.3

More counter examples . . . . . . . . . . . . . . . . . . . . . . . .

9

1 Introduction & bits, bytes & binary

1.1

Computer organisation

• Computers carry out a sequence of instructions called programs .

• Instructions are simple & represented in binary .

• We use abstraction to model how things work.

5 Problem-oriented language

4 Assembly language

3 OS machine level

2 Instruction set architecture level

1 Microarchitecture level

0 Digital logic level

Computers represent everything in binary.

Definition 1.1

(Bit) .

A bit is a 0 or 1.

Definition 1.2

(Byte) .

A byte is 8 bits.

Most computers are 64 bits.

Each position has a value, for example:

. . .

. . .

2

9

9 2

8

8

7

2 7 2

6

6

5

2 5 2

4

4 2

3

3

2

2 2 2

1

1 2

0

. . .

512 256 128 64 32 16 8 4 2 1

0

How do you convert binary to decimal? Use something like the table abe to convert the bits into powers of 2 and add them together.

Example 1.1.

Convert 1001001 to decimal.

1001001 = 2

7

+ 2

4

+ 2

1

= 128 + 16 + 1

= 145

How to convert decimal to binary?

1. Rewrite n as sum of powers of 2.

53 = 32 + 16 + 4 + 1

= 110101

2

CSSE2010 Computer Systems I Matthew Low

2. Divide n by 2, remainder of division is next bit. Repeat with n = quotient.

53 / 2 = 1 rem

26 / 2 = 0 rem

13 / 2 = 1 rem

6 / 2 = 0 rem

3 / 2 = 1 rem

1 / 2 = 1 rem

= ⇒ 110101

Definition 1.3

(Most significant and least significant bits) .

The most significant and least significant bits are defined as follows:

0

|{z}

MSB

101000 1

|{z}

LSB

Definition 1.4

(Unsigned) .

For now, unsigned means positive whole numbers. The smallest unsigned number in 8-bits is 00000000 and the largest number in 8-bits is 11111111. In decimal, this corresponds to 0 and 255 respectively.

Definition 1.5

(Radix) .

A radix-n base is a base with n unique symbols.

Bin 0 1

Oct 0 1 2 3 4 5 6 7

Dec 0 1 2 3 4 5 6 7 8 9

Hex 0 1 2 3 4 5 6 7 8 9 A B C D E F

Below are some common prefixes for different radixes:

C AVR AVR Assembly Assembly

Hex.

0x 0x h $

Oct.

0

Bin.

0b

0

?

q/@

0b q/@ b/%

2 Logic gates

2.1

Digital logic

• Only two logical levels present:

0 - small voltage (0 volts)

3

CSSE2010 Computer Systems I

1 - large voltage (1.2 - 5 volts)

• Logic gates are the building blocks of computers.

• Each gate has: one or more inputs exactly one output

• Perform operations (functions)

NOT, AND, OR, NAND, NOR

Only one possible output.

Definition 2.1

(NOT Gate) .

3 Binary arithmetic

4 Combinational logic

5 Flip-flops

6 Sequential circuits 1 - shift registers

Reminder about D Flip Flops:

Matthew Low

• D is input

• Q is output

• CLK is control input

• Q copies the value of D whenever CLK goes from 0 to 1 ( rising edge )

6.1

Combinational vs sequential circuits

Combinational circuits:

• Logic gates only

• Output is uniquely determined by the inputs

Sequential circuits:

• Include flip-flops

• Output determined by current inputs and state

• Changes when clock ticks

4

CSSE2010 Computer Systems I Matthew Low

Storage elements can only change at discrete instants of time.

We assume that we have a clock signal, and that the output of storage elements change only on the edges of control signal.

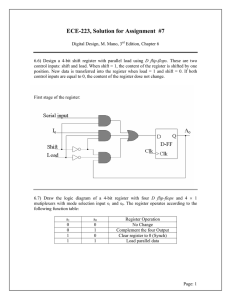

Figure 1: The bubble indicates active low signal . If the clear input is low, reset the flip-flops.

Definition 6.1

(Register) .

A register is a group of flip-flops. (As you would expect, an n -bit register consists of n flip-flops capable of storing n bits.) A register is a sequential circuit without any combinational logic

Definition 6.2

(Shift register) .

A shift register is a register which is capable of shifting its binary information in one or both directions.

6.2

Serial to parallel and parallel to serial conversion

Shift registers can be used to do serial to parallel conversion (and vice-versa).

5

CSSE2010 Computer Systems I

Example 6.1

(Serial to parallel) .

See the logic diagram below:

Matthew Low

Example 6.2

(Serial to parallel and parallel to serial) .

See the logic diagram below:

Note the following functions:

• 0 - load data in parallel.

• 1 - load/shift data in serial.

6.3

Bidirectional shift register

Definition 6.3

(Bidirectional shift register) .

A bidirectional shift register can shift both left and right.

Exercise 6.3

(Bidirectional shift register) .

Using the same multiplexer concept, draw a 3-bit shift register which allows data to be shifted in either direction.

Hint: consider this element, where DIRN will be 0 for left shift and 1 for right shift.

6

CSSE2010 Computer Systems I Matthew Low

6.4

Universal shift register

Definition 6.4

(Universal shift register) .

A universal shift register can right shift, left shift and has parallel load functionality.

Example 6.4

(8-bit wide shift register) .

Multiple bits shifted at a time. An example 4-stage 8-bit queue:

7 Sequential circuits 2 - counters

7.1

Counters

Definition 7.1

(Counter) .

A counter is a multi-bit register that goes through a determined sequence of states (values) upon the application of input pulses.

A counter which follows the binary number sequence is a binary counter. An n -bit binary counter has n flip flops, and can count from 0 to 2 n − 1.

Example 7.1.

A 2-bit binary counter will count:

00 → 01 → 10 → 11 → 00 → . . .

Definition 7.2

(One-bit counter) .

It is as follows:

7

CSSE2010 Computer Systems I Matthew Low

We can represent this using a table that shows the current state and the next state:

Q D

0 1

1 0

The timing diagram is as follows:

Note that the count sequence is the bottom line of numbers.

Note 7.1

.

The following is the 4-bit binary counter counting sequence:

1

1

1

1

0

1

0

0

1

0

1

1

Bit 3 Bit 2 Bit 1 Bit 0 Value

0 0 0 0 0

0

0

0

0

0

0

0

1

0

1

1

0

1

0

1

0

3

4

1

2

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

13

14

15

0

9

10

11

12

7

8

5

6

7.2

State

8

CSSE2010 Computer Systems I Matthew Low

Definition 7.3

(State) .

Values stored in the flip-flops can be considered the current state of the circuit. D inputs to the flip-flops are the next state .

D inputs are some function of the current state and inputs.

7.3

More counter examples

Note 7.2

.

The following key points on counters:

• The next state is a function of the previous state (and possibly inputs)

• Count sequence can be binary numbers but it does not have to be. If it is, the counter is a binary counter.

• Circuits are synchronous; all flip-flops have the same clock.

Example 7.2.

2-bit counter that counts

00 → 10 → 01 → 00 → . . .

Very easy to draw a table for this:

Q

1

0

0

1

1

Q

0

0

1

0

1

D

1

1

D

0

0

0

0

X X

0

1

Note 7.3

.

’X’ means "don’t care" - choose values to make the logic as simple as possible. In this case, it’s best to choose 1 for D

0 and 1 for D

1

(although

0 for D

1 is equally as simple).

9