418

IEEE JOURNAL

Takao Nakano

was born in Hyogo,

Japan, on

He received

the B. S.,

September

1, 1939.

M. S., and Ph.D. degrees in electronics

engineering, from Osaka University,

Osaka, Japan, in

1962, 1964, and 1968, respectively.

He joined the Central Research Laboratories,

Mitsubishi

Electric Corporation,

Tokyo,

Japan,

in April 1964.

From 1964 to 1967 he was engaged in research and development

of optoelectronics devices at the Semiconductor

Research

Institute,

Sendai, Japan, and the Central

Re-

Approximation

Ab.rtract-Two

mation.

approximation

One is analytical

The basic model

MOSFET

methods

for wiring

formulas

for

the delay

delay

is a lumped

is a distributed

at one end and a capacitive

proximated

for wiring

and the other

in MOS

CR line with

load at the other

end.

and the step response

LSI

approxia drive

Simple

ap-

of this model

are obtained.

Approximation

bination,

programs,

is found

models

the

of a distributed

which

is very

useful

is also investigated.

to

be a poor

under various

incorporated

The widely

approximation,

give satisfactory

interconnection

CR line by lumped

when

results.

line

used L ladder

while

The simplest

within

a given

R’s and C’s com-

in circuit

IT and

circuits

tolerant

simulation

circuit

model

T ladder

circuit

that approximate

error

are tabulated

drive and load conditions.

LIST

c

Capacitance

r

Resistance

OF SYMBOLS

of wiring

of wiring

L

Length

c

Total

capacitance

R

Total

resistance

C*

Load

per unit

per unit

length

of wiring

of wiring

of wiring

capacitance,

gate capacitance

(=c ~L)

(= r “ L).

including

MOS

MEMBER,

1983

LSI

IEEE

r*

Equivalent

CT

= Ctlc

RT

= rr/R

x

t

t’

The coordinate

resistance

Normalized

s

Laplace

transformed

variable

fort

s’

Laplace

transformed

variable

for t‘

rJ

v

=-s’

transformed

voltage

transformed

current

from

of drive MOS transistor

driven

point

to load

Time

time

(= t/CR)

Volt age

v

Laplace

i

Current

I

Laplace

Vcc

Supply

voltage

Relative

error

REMP

length

VOL. SC-18, NO. 4, AUGUST

Delay in MOSFET

SAKURAI,

circuit

CIRCUITS,

search Laboratories,

Mitsubishi

Electric

Corporation.

Since 1968 he

has been involved

in the research and development

of bipolar and MOS

LSI devices.

His most recent activities

have included

the development

of high speed and large capacity VLSI.

He is currently

the Manager of

the Design Technology

at the LSI Research and Development

Laboratory, Mitsubishi

Electric Corporation,

Hyogo, Japan.

Dr. Nakano is a member of the Physical Society of Japan, The Institute of Electronics

and Communication

Engineers

of Japan, and the

Institute

of Electrical

Engineers of Japan.

of Wiring

TAKAYASU

are studied.

OF SOLID-STATE

of minimum

subindex

D

Distributed

subindex

L

L ladder

circuit

subindex

n

n ladder

circuit

subindex

T

T ladder circuit,

CT

pole

line

except

for CT and R ~.

transistor

to be driven

Manuscript

received June 1, 1982; revised November

24, 1982.

The author

is with the Semiconductor

Device Engineering

Laboratory, Toshiba Corporation,

Kawasaki 210, Japan.

001 8-9200/83/0800-041

I.

I

N MOSFET

tor

in

the delay

8$01.00

LSI,

determining

induced

INTRODUCTION

a wiring

delay

becomes

total

delay

of a system.

by word

@ 1983 IEEE

an important

lines, bit lines, clock

fac-

Particularly,

lines, and bus

SAKURAI:

APPROXIMATION

OF WIRING

DELAY

IN MOSFET LSI

419

problem.

As

model

is found

of the

delay

three

c

T1

well.

tkan

3 percent

connect ed.

in reducing

examples

is a simplest

Section

of

the

is for

in memory

the

[l]

- [3]

by

partial

the

the capacitance

and the resistance

of

second

step is to

equations,

and extensive

been made to solve the differential

of this field

At

the

is given by Kumar

initial

convenient

approximated

objects

some

behavior

of this

paper

and the step response

ous external

circuit

plifying

the

delay.

The

mating

a partial

are usually

by

this

circuit

This

lines under

design.

are suitable

models

for

such as a word

time

of

of the acroughly

esti-

performance,

lumped

programs

such

is widely

clear.

of the method.

of a distributed

circuits

Then,

current

drive.

equivalent

discussions

Appendix

slowest

out

an arbitrary

A.

This endpoint

response

function

and

TD(s’ ) from

point

about

concentrated

delay time

the

2 in Fig. 2), some

O to point

and voltage

line

the system

unchanged.

on the voltage

(point

is important

decides

The same

case, due to a lin-

are essentially

of

of

discus-

rt/R <<1 corre>>1 to a constant

on the current

position

choice

in Fig. 2(b).

of the line

The

and 1/

Detailed

Conclusions

models

are mairdy

are carried

of

IV and V.

circuit.

of the endpoint

the good

the discharging

of lumped

it is the

account,

conductance)

drive and rJR

of the line is explained

and the accuracy

calculations

drain

but

into

in this paper.

in Sections

by

by a capaci-

exact,

However,

voltage

can be used for

earit y of this

for

wave-

Cr = rt = O in

because it shows the

speed.

2 is written

1

T~(s’)

lines

The transfer

as

=

(1 +S’CTRT)COSO

—.—

- (RT+CT)fl

sin-”

(see Fig.

ASTAP,

and

the accuracy

The second

object

A comparison

of

of this

between

CR line and that

is made to shed light

conductance).

to a constant

is replaced

to make the problem

the drive conditions

to be the former

Charging-up

in order

by rt is not

1/(maximum

on rr are given

discussion

the drive transistor

in Fig. 2(b),

as

in an MOS LSI can be

(1)

they are simu-

as SPICE,

used, but

drain

CR

and the

to the gates of MOSFET’s

rr and the load transistor

of taking

out

by MOSFET’s

of the wiring

replacement

sponds

form

in

line delay.

interconnection

circuits).

way

(minimum

Although

and a delay

This

rt turns

response

bounds

and

in this paper is a distributed

Then,

of rf is between

vari-

stress is put on sim-

generation,

are summarized

FOR WIRING

1) is driven

Most

resistance

Ct as is shown

simplest

sions

in

One is for a word

of the next

2) is connected

to this form.

tractable.

value

considered

in Fig. 2(a).

tance

ap-

above-mentioned

V.

Conclusions

MODEL

one end (point

end (point

shown

work has been

stage of an MOS LSI design, in order

was not

function

circuit

One of the

degradation

lumped

method

approximation

lumped

formulas

much

by equivalent

paper is an assessment

the transfer

too

the

for the delay

Some analytical

much

it is

express

CR line.

formulas

a step response

system

equivalent

CAD

which

of the interconnection

and final

substituted

SCEPTRE.

LSI’S

of the distributed

delay of a system,

a total

1 for various

however,

In this paper,

resultant

At the middle

to evaluate

MOS

is to give simple

for

have

A good review

formulas

conditions.

formulas

curacy.

lated

simple

CR lines without

distributed

studies

equations.

et al. [5] to give the upper and lower

done by Penfield

of the CR line

the re-

[4].

stage of designing

to have

calculate

CR lines are to be described

The distributed

differential

speed

as dis-

the CR line delay,

and the

sponse of the line.

to operation

lines are considered

to evaluate

In order

step is to estitnate

line

LSI are essential

interconnection

CR lines.

tributed

first

or logic

These

that

This circuit

so it is tabulated

of the

in Section

LSI memory

CMOS

The basic model

line whose

reduced

of a chip.

circuit

con-

VI.

an equivalent

lines

cost,

is less

steps are

circuit

the tolerance.

application

are presented

11. BASIC

other

lumped

within

computational

in an n-channel

the other

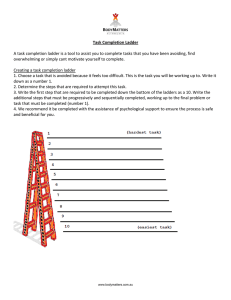

Fig. 1. Various

lumped circuits

used to approximate

a wiring.

N: no

additional

circuits; C: only one capacitor; R: only one resistor; CPL 1:

C preceding L circuit; L 1: one-step -L circuit; PI: one-step n circuit;

T1: onestep

7’ circuit; P2: two-step n ladder circuit;

T2: two-step 2’

ladder circuit; P3: three-step n ladder circuit.

of the delay

and an external

II or

CR line

case if three ladder

error

delay

hand,

the distributed

error

error

IV-B.

Two

line

there

the wiring

approximation

T2

a tolerant

circuit

even when

On the other

case, the relative

are given,

L ladder

The relative

as 30 percent,

can simulate

even in the worst

When

proximates

Section

adopted

to as much

models

In this

is useful

usually

approximatiort.

steps are concatenated.

circuit

very

dition

the

to be a poor

amounts

ladder

T ladder

a result,

of the

on this accuracy

Detailed

derivation

AS is seen

and rt,

response

but

from

the

of this

(1),

ratios

of the line.

are symmetrical

load conditions

equation

it is not

et/C

the

and rt/R

It is interesting

in (1),

and this

is given

absolute

that

of

determine

to note

indicates

are of equal importance.

in Appendix

values

C’,

B.

R, cl,

a voltage

that CT and R ~

that

the drive

and

IEEE JOURNAL

OF SOLID-STATE

CIRCUITS,

VOL. SC-18, NO. 4, AUGUST

1983

drive

MOSFET

capacmve

load

--+

R

- 0.5 –exac+

>“

<

~

>.

\

0

(a)

----m+

wwe

C1J2’

exponento

opproxlmatkon

-40~

2

{a)

t/CR

h

o

I

m-;-m

Vo (t)

“(’)

J

J

J

c

J

n“

(b)

sigle

Fig. 2. (a) Basic model for wiring in MOS LSL

(b) Equivalent

circuit

of the basic model.

The drive MOSFET

is replaced by an equivalent

resistance rt and the load MOSFET by a capacitance.

-.4

exponential

opproximrtlon

1

1

I

0

i

1

2

t/CR

111, ANALYTICAL

A.

One Exponential

~en

Function

a step voltage

the response

Approximation

is applied

at the gate of a drive transistor,

2, Vz (s’), is written

of point

as

v2(s’)=~TD(s’j,

(2)

Denoting

the absolute

~k,.”.,

in an increasing

V2 (t’)

values of the poles of (2), O, UI, U2, . . . .

order,

can be expanded

by using Heaviside’s

112(t’)

—=

vcc

the response

in multiexponential

expansion

1+ ~

k=l

Fig. 3. One exponential

function

approximation

for a step response

of an interconnection

line.

Exact waveform

is also shown as a reference. (a) RT=CT=O.

(b) RT=O,

CT=l orRT=

l, CT=O.

Approximation

is excellent at u = 0.9 vcc.

APPROXIMATION

in time

form

domain

as follows,

theorem:

(3)

Cfie-”kr’

where

c~ = (-ly’

2 {(1

@

{(1 +R$u;)(l

+R$u;)(l

+ @&)

(b)

+ C;o;)

+ (RT + CT)(1

+RTCTU,)}

“

(4)

Sigmas are the solutions

of the following

equation:

: -,,3Q~

—

1 -R TCTUK

tan fi=—

It is shown

by inspection

(5)

is given

can

be

in Appendix

solved

A.

the third

vz(t’)

infinity.

term

is equal

is found

exactly

In other

expansion

only

when

CT

=

RT = O as

cases, the solution

must

be neglected

of the step response,

to be less than

10-9

following

be

if a global

the terms

waveform

higher

than

is of interest.

zero to

the third

That

can

is, the

equation

of distributed

CR

(Cl)

in multiexCR line.

is an excellent

approximation:

V*(t’)

—=l+C1.

Vcc

(3),

at the time when

to 0.9v cc even if CT and RT vary from

This means that

Cr)

(6)

numerical.

In the multiexponential

RT(ot

Fig. 4. (a) Minimum

pole (o ~) of transfer function

line for various CT and R ~.

(b) First coefficient

ponential

expansion of step response of a distributed

of (5) that

(k-;)n<uk<(k-+)fi.

Howeverj

z

v-

(5)

(RT+CT)&_”

Fig. 3 shows

e- Olt’.

a comparison

and the approximated

UI

and

and R T.

Cl

are plotted

(7)

between

response

the exact voltage

by (7).

Numerically

in Fig. 4, respectively,

for

response

calculated

various

CT

SAKURAI:

APPROXIMATION

I 04

OF WIRING

\

I 0’

DELAY

IN MOSFET LSI

421

I

1

Parometer

C~(orR71

-

\

Iog./-=

Ix

>:

v

I(Y -

;

~

~ 0,5

z

>.

10

1 ladder

0.5

- step

RT=CT=O

L%

10

I

~o

I

I L

0.01

0.I

10

I

R~(or

o

I 00

I

CT)

2

t/CR

(a)

(a)

I

8,

>:

0.5 -

>

s

>.

0

RT (or

llEi

T

0

I

(b)

(b)

Fig. 5. Delay (tog)

of a distributed

CR line.

(a) In log scale.

linear scale. When x-axis is chosen for R ~, parameter

is CT.

x-axis

is chosen for CT, parameter

(b) In

When

is RT.

B. Delay Time

We define

point

O to

tog

as a time

the

time

delay

when

0.9 UC,.. Since the accuracy

lay t~,g (= t0.9/CR)

to a step voltage

the

node

2 in Fig.

of (7) is excellent,

is calculated

at the drive

2(b)

Fig. 6. Step responses of L, n, and T ladder circuits and distributed

CR

line for C’T = RT = O. (a) Number of ladder steps= 1. Current is also

shown.

(b) Number

of ladder steps = 3. n and T ladder circuits approximate

a distributed

CR line much better than the L ladder circuit

does. Although

only waveforms

for charging-up

case are shown, those

for discharge are easily seen if the chart is put upside down because

of the linearity

of the circuits.

reaches

normalized

de-

A. L and T Ladder Models

(8)

their

calculated

large, the delay time

Fig. 5(a).

of a MOSFET

other

hand,

when

constant,

Fig,

5(b)

limited

stants.

In fact,

relative

error

be expressed

to9/CR

both

setting

linear

form

of this

t~9 on

of

t~9 can

that

is

both

be approxi-

a, b, and c are con-

where

CT, R T <1,

in a very simple

error

the delay

so as to minimize

the delay

The

These circuits

circuit

coincide

with

are easily

a distributed

circuit

use of the

reproduce

circuit

Moreover,

must

which

is useful

LUMPED

Initially,

Transfer

it is difficult

discussions

are suited

for CAD

because

to improve

it does not

circuit

IT, and

T ladders

are obtained

in

B as

1

TL(s’)=

to

<

1

f

!

1

1.1 percent

when

TJs’)=TT(s’)=-————

cos (72{)

(11)

where

+—

)

and is less than 4 percent

MODEL

an analytical

stage of LSI

simulators.

programs

bidirec-

the approximation

to the case of Ct = rt = O.

are confined

of L,

functions

Appendix

(9)

is within

CIRCUIT

deals with

in the initial

with

a nonuni-

CR line [6].

s’

2n2

section

compatible

the number

when the line is driven

for any CT and RT.

The previous

a distributed

pa-

and the

as

CT and R T are less than unity,

IV.

here because

obtained

proposed

be restricted

response

models

the shape of

CR line when

Rajput

to approximate

the correct

circuit

from

are chosen

elements

steps goes to infinity.

ladder

tionally.

The names are derived

the

is found

+ CT +RT).

formula

blocks.

of the

of ladder

form

1.

easily.

dependence

these constants

range

= 1.02 + 2.21 (CTRT

relative

On the

by the line itself.

it is suspected

in the

by the drive capa-

of the load.

CT are small,

by a + bCT + bR T + CCTRT

mated

The

capacitance

of RT and

a nearly

CT and R ~, so that

R T and CT are

to R ~ or CT, as seen from

the delay is limited

or the

both

shows

to.9.When

of

is proportional

In this region,

bility

almost

results

in Fig.

unit

rameters

circuits

S shows

of n. T, and L ladder

Some of the examples

as follows:

are shown

Fig.

2

t/CR

CT)

are treated

Step responses

approximation

design,

Lumped

but

models

in this section.

Fig.

is not

These

which

sion

6 with

responses

theorem,

for n = 1 and 3 are shown

of these circuits

responses

of a distributed

can be calculated

similarly

uk’s are expressed

as

to

(3),

(12)

in

CR line as a reference.

through

Heaviside’s

expan-

if ok’s and Ck’s are obtained.

IEEE JOURNAL

422

OF SOLID-STATE

CIRCUITS,

1983

VOL. SC-18, NO. 4, AUGUST

.4

\

‘\

-o

Ladder

2

I

t/CR

(a)

- steps

(1)

,

I

Oistrlbuted

CR,

>:

0.5 -

:

;N

o

Ladder

0

I

- steps

2

t/CR

(b)

(b)

Fig. 7. Relative error of minimum

pole (REMP)

of L, r, and T ladder

circuits.

(a) CT=RT=

O. (b)RT=

O, C’T= 1 Or RIJ-= 1, CT= O.

REMP is almost equal to relative error of a delay as seen from Figs. 6,

8, and this figure.

Accuracy

of the model increases as the number of

ladder steps n increases, but it saturates at about 3 or 4.

Fig. 8. Step responses of L, rr, and T ladder circuits and a distributed

CR line for finite CT or R ~, namely CT (R ~) = O, RT (CT) = 1. (a)

Number

of ladder steps= 1. (b) ~umber

of ladder steps= 3. n and T

ladder circuits

approximate

a distributed

CR line much better than

the L ladder circuit does.

TABLE

1

or THRFE-SIEP

T LADIIE.R

REMP

‘~=4[nsinr=T)12

‘k=’’””) “3’

As for

the L ladder

search the poles

following

where

circuits,

of (1 O).

7’(s’)

Now,

is one of TL(s’),

an index

of the

to discuss

tively.

A relative

error

for this index

is applied

numerically

to

by the

‘EMP

= (u,

In the present

REMP

is proportional

is almost

and this

situation

is relatively

accuracy

equal

seen from

percent,

hand,

be noted

in Figs. 6-8.

The

three

2,3

2.1

1.2

-.3

-.3

2.1

1.3

-.,/

-.2

1

1.2

1.1

.9

.1

.0

2

.7

.7

.0

.1

.U

rr and T ladder

that

the accuracy

creases, but it saturates

circuit.

for

estimating

in Fig. 7(a).

model

to as much

is improved

or four

an

is of interest.

ladder

is a

as 30

I and II.

because

B.

the load

circuit

response

better,

becomes

as shown

These results

can be replaced

external

the

in

are calcu-

This improvement

capacitance

by exact models

elements

is

and the re-

become

and the

eminent

as

CT and R 1’ increase.

obtained

The

As

value,

becomes

(Bl 3) in Appendix

at the input

one more

the REMP

has a finite

approximation

of these

Because

are satisfactory.

three

the

effects

finite

steps are connected.

models

Since

constant,

used L ladder

of the models

at about

U2, so that

the

(B8)-

than

amounts

-.3

1.2

understood

For

time response

REMP

ladder

using

naturally

worse

on n is shown

2

-.3

3.1

and 8 and Tables

of the delay (tog)

it is suitable

1

1.2

0.01

or R=

CT

and

sistance

from

of a time

error

Figs. 6 and 7(a), the widely

even when

(15)

separated

to the inverse

of the REMP

When

slower

Figs. 7(b)

of the ladder

when voltage

approximation.

is chosen

lated

to the relative

easy to calculate,

The dependency

(REMP)

CR line) -1”

constant

is assured

of a model

pole

2.1

models

quantita-

circuit)

UI is quite

as a time

circuit

error

Concretely,

of a lumped

instances,

lumped

the approximation

of a distributed

it is considered

the delay

of the

2.3

1: Errors are in percent. 2: Negatwe (positive) value corresponds to

under- (over-) estimation of the delay.

and TT(s’).

of a minimum

in this paper.

(al

Tn(s’),

error

be settled

other

method

‘T

L).ul

U.1

u

LJ

formula:

should

poor

Newton’s

CZ is calculated

cr

MOIIFI. (P3)

C’T and RT,

circuit

element

by this addition

REMP

than

The result

L circuit

the normal

the

L ladder

Although

model

is much

r? and T models

the L ladder,

is worth

of C preceding

is also calculated.

than

too,

T models.

rr and

have

the improvement

the cost.

L circuit

is that

(see CPL 1 in Fig.

this CPL 1 is much

(L 1) and should

not

1)

worse

be used in any

case.

On the

It should

as n insteps.

B. Recommended

It

either

is pointed

out

the three-step

Circuit

in the previous

rr or T ladder

section

circuit

that

the REMP

of

is less than 3 percent,

SAKURAI:

APPROXIMATION

OF WIRING

DELAY

IN MOSFET LSI

423

5

TABLE 11

REMP OFTHREE-STEPT LADDER MODEL ( ~3)

CT

4

‘r

o

U.ol

2.3

2.3

.2.2

1.2

.7

~

0

:

0.01

2.1

2.1

2.1

1.1

.7

U

0

0.1

1.2

1.2

1.3

.9

.6

;

1

-.

-.3

-.2

.1

.1

2

-.3

-.3

-.2

.0

.(I

u

3

U.1

1: Errors are m percent.

under-

(over-)

2: Negative

of the delay.

estlm-atlon

/

(positive)

—

J

.01

.1

.2

.5

1

2

5

10

20

5(I

100

z

value corresponds

5

10

20

to

1

1

I

5

10

15

types are abbreviated

according

to Fig.

gether with dc chmacteristics of drive MOSFET. Approximation

by

P2 is excellent, while L2 cannot reproduce the correct response. The

line denoted by one exp. approx. is calculated by simple formula (7).

Dash-dot line in the figure represents dc characteristics of rt whose

value is chosen to fit to.9 to the correct response.

only

in ordinary

of widely

1.

V.

o .01

.1

.2

lJ

2U

50

100

—

Cucuit

types are abbreviated

but it is not

practical

5

simplest

lumped

tolerant

error

10

20

the

approximates

tolerant

error

value

1/(ma~imum

of

drain

Since

the

creases, the

safer

choice

tables,

of

the

always

circuit

This

simulator

of nodes included

has one more

that

these

node

3 percent,

rt

drain

is chosen

is because

programs

strongly

than

the fl ladder.

circuits

LSI memory

LSI memoline in an n-

design.

lines are driven

channel

model

effect,

whose

lines in the figures

equivalent

resistance

calculated

word

Fig. 10 is

by a p-channel

are also

is MOS3 of SPICE

the back-gate

parameters

bias effect,

are fitted

to real

show the characteristics

of the

For

a p.channel

conin-

It is to be emconfined

tion

it is difficult

delay induced

Broken

of 1/

drive

is because

10-20

percent.

by the word

most

of point

the

of

1 in

the time,

Fig.

conductance

drain

below.

rt

10,

of triode

this value exactly.

conductance),

which

is

For the usual poly -

constant

speed the contribution

of rt corresponds

on

the value of rt.

rt is near the value

to calculate

the CR time

For

ID depends

This

drain

to the reasoning

lines where

is about

error

the simulation.

current

region

response

is 1/(maximum

the response

to tog

a triode

as 1/(average

However,

word

in

the voltage

bad according

silicon

MOSFET,

conductance).

be chosen

An easier choice

limits

on

drive

drain

the drain

is chosen to fit the

so that it is easy to obtain

is operated

region).

not

m and

depends

should

by (9) with

MOSFET

V~~ nearly linearly,

(maximum

rt, the value of which

line delay fog

drive

as seen from

and the T ladder

are not

line delay anal-

assuming

Fig. 9 is for a word

The transistor

saturation,

respec-

as rJR

both

of the word

by SPICE,

where word

the short

MOSFET

the computational

in the circuit

recommended

a

de-

conductance).

when

ANALYSIS

ID versus V~~ plots of the drive MOSFET’S

and IV

drain

gets better

DELAY

where the gate of the word line drive MOSFET

in these figures.

an n-channel

is between

and 1/(minimum

is (1/maximum

a n ladder

circuit

and

LINE

is appropriate.

MOSFET.

Dash-dot

within

III

out

as in a dynamic

mobility

one

is met

devices.

circuit

in Tables

resistance

approximation

are candidates.

the number

phasized

equivalent

conductance)

ductance).

T ladders

are tabulated

10 percent

of the

the wiring

by only

condition

memory

and includes

cost, the

Since the simplest

This

for CMOS

and

for all of the wir-

that

circuit

50.

approximation

TO WORD

is carried

memory

does not

wires for MOS LSI, and thus the validity

design of next generation.

shown

circuit

computation

can be replaced

than

10 are two examples

Simulation

channel

1.

to reduce

is recommended.

The

In these

this

IV, a wiring

is greater

aluminum

is bootstrapped

C

case because the REMP

used one capacitance

Figs. 9 and

50 100

Table

APPLICATIONS

ysis.

to Fig.

In order

on CT and R ~, they

tively.

according

to employ

ing in an LSI design.

time

z

P3 P3 P2 P2 P1 P1 P1 PIPI

CCC

P3P3P2P.2P1P1

PIPIPI

CCC

T2 ‘T2 P2 P2;

:P1P1P1P1C

cc

T2 r2

P-2 P2

PIP IPIPI

CCC

PIP IPI

CCC

T1 T1 T1 rl

el

pl

rl

T1 T1 T1 P1 P1 P1 PIPI

CCC

C

‘r 1 T1 T1 T1 P1 P1 P1 P1 L1 L1

P1 P1 P1 PI Pl

PIPILILILICC

P1 P1 PIPIPIPILILIL1

LICC

RRRRR

RLILILILICC

RR

RRRRR

RRRCN

RR

RR

RRRR

RRNN

0

.01

.1

..2

.5

1

2

5

pends

~T

.5

input

waveform.

if rJR

capacitance

ry

r

on the input

As seen from

C

—

for

to the step voltage

depend

TABLE

IV

RECOMMENDED LUMPED CIRCUIT TO SIMULATE DISTRIBUTED CR

LINE WHEN 3 PERCENTERRORIS ADMITTED

:

(nsec)

Fig. 9. Step response of a word line in n-channel dynamic memories to-

50 1(JU

P2P2P2P1P1P1P1

Cc

ccc

P2 P2 P2 PI

P1 PIP ICC

CCC

P2P2P2P1P1P1P1

Cc

ccc

CCC

T1 T1 T1 P1 P1 PIP ICC

IPIPIPICC

CCC

rl

T1 TIP

PIP

IPIPIPIPIP1

LIC

CCC

P1 P1 P1 P1 P1 PILILIC

CCC

RRRR

RLILILI

CCC

RR

RRRRR

RC

CCC

RR

RRRRR

RCCNN

RR

RPRRRR

CNNN

RR

RRRRR

RCNNN

Circuit

rfz

I -

u-i’

:T

.5

CR

2

LINE WHEN 10 PERCENTERRORIS ADMITTED

.2

dwtrlbuted

——L2

TIME

.1

—

9

TABLE

111

RECOMMENDED LUMPED CIRCUIT TO SIMULATE DISTRIBUTED CR

o .01

one ,Xp Opprox

—

o

CT

~----

12

of the word

line

of the term

2.2 lrtC

In this case, 30 percent

estima-

to 3-6

percent

error

of the total

line.

lines in Figs. 9 and 10 show the calculated

waveform

424

IEEE JOURNAL

5

_—.

A ‘---

/“

/’”

one

—

/

exg

VOL.

SC-18,

L2

—

rrz

V(x,

t)

i (x,

t)

(t) ~

v,

Fig. 11.

to.9

1

8

1

5

10

15

TIME

The

(nsec)

=

error

of this

R ~ <1

CT,

parameters.

These

the

simple

formula

They fit the simulated

(7j.

only

discharging

charging-up

of word

lines

of the line by an n-channel

is discussed

MOSFET

here,

is similar

to

the case of Fig. 10.

An

analytical

mation

approximation

for wiring

the following

delays

points

1) The usually

proximation

2)

An

ifP3

other

hand,

P2 is enough

to achieve

situation

approximation

CR line

by

Ct and

rf play

delay.

The

CR line

namely

an important

ladder

circuit

mended

the

CR line

in practical

circuits

model

use.

For

this

are tabulated

with

circuit

a given

point

and

First,

that

error

III

IN

useful

RESPONSE

THE

solutions

CASE

(CT = O), the following

at the

end

of

R~ =O

a distributed

impedance

termin-

Under

into

two parts at

that 12 (s’ ) = O

the condition

holds

solu-

for com-

(see Appendix

B):

~2 (s),

(Al)

V(x,s)=cosh

(A2)

+Wv,(s).

Assuming

that

point

case,

1 is excited

by step voltage

from

zero to

vCC,that is,

Vo(s)=:,

(A3)

the following

expression

V(x, s)

=;

“

V(x, s) is obtained

by (Al -A3):

Cosh{+”:)}

cosh ~

wiring

The inverse

for

Laplace

“

transformation

of (A4)

yields

3)

If rt/R

is greater

ror.

This

with

[8]

can simulate

should

be em-

the

recom-

and IV under

vari(A5)

in aluminum

The

a global

the

since

of widely

the

condition

pole

of the

CR line can be

within

3 percent

used one-capacitance

rt/R >100

is usually

The current

minimum

shape

t) is calculated

as

met

i(x,

t)

/()”

;

= 2 ~

(-l)k-l

sin

k=l

[(k-w:)]

. ~-(k-W)2~2(t/W,

of voltage

one

i(x,

er-

wiring.

Consequently,

duce

50, a distributed

one capacitance

assures the validity

approximation

4)

than

only

transfer

response

exponential

step response

(A4)

steps are

ous drive and load conditions.

approximated

of

in esti-

STEP

C’T =

of the line is given only

equation

= cosh (~)

tools

FOR

OF

CR line is divided

11.

range

[7] . Here, the time-domain

position

a distributed

1.1 per-

entire

A

VOLTAGE

in Fig.

dis-

a distributed

infinite

provide

open, and characteristic

an arbitrary

x, as is shown

the

lines in MOS LSI.

by Peirson

driven

any

the

of view,

in Tables

the

in

in determining

simplest

within

The most

when

load

when

becomes

error.

Ct = r’t = O.

coincides

is less

lines where

occurs

network

of

word

capacitive

role

linear

However,

distributed

ployed

any

voltage,

as a four-port

connected.

the

3 percent

is without

a step

error

models

For conventional

short,

is less than

for

steps

of n and T

relative

circuit

ladder

difficult

directly

the

are employed.

for

for

two parts.

ap-

error

ladder

the accuracy

with

rf -0.1,

tributed

The relative

or T3 models

approximation

is a poor

even if three

Here,

as et and rt increase.

better

model

CR line.

is satisfactory.

than 3 percent

circuit

as 30 percent,

On the

models

approxi-

As a result,

AND

ation is presented

~~(S)

L ladder

a distributed

is as much

are connected.

ladder

circuit

LSI are studied.

are made.

adopted

for

delay

and a lumped

in MOS

of word

time-domain

pletion.

SUMMARY

will

EXCITATION

CR line with

tion

VI.

the

VOLTAGE

Exact

Although

formula

APPENDIX

curves

well.

simple

and 4 percent

formulas

the behavior

CURRENT

using

CR line into

1.02CR + 2.21 (ctrt + ctR + rtL’).

for

mating

the distributed

L

as

relative

cent

Fig. 10. Step response of a word line in CMOS memories together with

dc characteristics

of drive MOSFET.

Discharging

of a word line by an

n-channel MOSFET

is similar to this figure if the figure is read upside

down.

by

1983

v~(t)

I

x

Dividing

be calculated

,

4, AUGUST

I

o

0

NO.

opprox

— d,str! buted CR

‘—

/

,/

CIRCUITS,

—.

——

4*

OF SOLID-STATE

is sufficient

The wiring

(A6)

dominates

of a distributed

term

[see (7)] .

function

delay

CR line.

to

repro-

to.9 can

This can be obtained

av(x, t)

ax

—=-r”i(x,

by differentiating

f)

(AS),

and by using

(A7)

SAKUR.41:

APPROXIMATION

OF WIRING

APPENDIX

DERIVATION

Transfer

CR

line

for

a unit

are derived

in this order.

425

rt

o

FUNCTIONS

circuits

matrix

circuit

n-step

-.

and a distributed

The fundamental

of an n-step n and T ladder

block

IN MOSFET LSI

B

OF TRANSFER

of rr, T, L ladder

functions

DELAY

l.(s’)

1,(s’1

Vo(s’)

V, (s’)

Z.

cosh (g)

:,

[ Z;

1 sinh (g)

sinh (g)

cosh (g)

12[s’)-

FI

is expressed

1

2

circuit

Fig. 12.

(Bl)

Capacitance

It is difficult

ladder

where

circuit.

Ct and resistance

rr, or 7’ ladder

to obtain

the

However,

when

ths L ladder

circuit

circuit

a resistance

with

c,

V*(S’)

as [9]

FI

ladder

happens

Ft are connected

circuit.

counterpart

to either

of (B8’)

Ct = O, a transfer

to be equal

to tht

CT

zero

in (B8)

the L,

the L

for

functioo

of the

R/2n added at the input.

R= b y R ~ + ~ n and setting

I

of

T ladder

Substituting

leads

to

(B2)

1

TL(s’)=—

Z.

1

.

(for

c@-

rr ladder)

(B12)

cos (nf) - ~

(B3)

RT + &

()

1+$

@

sin (n{)

r’

r

_— 1

Since

unit

the

ladder

n times,

block

1+1

c@-

total

n and T ladder

where

is created

fundamental

is

When

circuits

by concatenating

matrix

as shown

Fn for total

the

For

a one-step

tained

ZO sinh (rig)

1 sinh (rig)

cosh (rig)

rt and capacitance

resistance

1+;

the

‘

=

[ Z;

!

(B4)

p~=

cosh (rig)

F. = (Fl)n

Tladder).

r

circuit

the

circuit

(for

4n2

1

the

transfer

+(l

1

+CT)(l

that

IT, T, and L ladder

T~l(s’)=~,

(B5)

circuit,

function

is easily

ob-

(B14)

t~T)”

“

et are added

in Fig. 12, the following

L

as

It is obvious

to the ladder

equations

hold:

distributed

CR line if infinite

be readily

confirmed

equations

which

them.

n tending

by

blocks

starting

describe

the

to infinity

circuits

from

line

coincide

are connected.

the partial

and

Laplace

in (B2) and (B3),

with

a

This can

differential

transforming

we have

(B6)

ng

(B15)

=0

Iimn+m

12(s’)=s’ctv~(s’).

Then,

the transfer

Fig. 12 is written

T(s’)=—

(B7)

function

T(s’ ) from

point

O to point

1

zo=—

2 in

as

V*(s’)

Equation

Vo(s’)

(B8).

(1)

is obtained,

1

(1+

S’CTRT)

cos (nf)

-

substituting

the

relation

(B 15) for

ACKNOWLEDGMENT

L )

‘2+

(B16)

c@- ~

CTLP

@

Sin (FZ{)

The

author

Furuyama,

(B8)

cussions.

Dr.

critical

like

T. Iizuka,

to

reading

thank

Mr.

K.

Ohuchi,

and Dr. K, Tamaru

He also expresses

encouragement

where

would

throughout

his thanks

this work

to Mr.

Mr.

for helpful

T.

dis-

Y. Uchida

for

and to Dr. K. Natori

for

of this paper,

(B9)

tan t =

REFERENCES

ml(”$)

(BIO)

@=l/fi

[1]

‘fOr”ladder)

[2]

.

l+Q

r

(for

4n2

Tladder).

(Bll)

A. E. Ruehli

and P. A. Brennan,

“Accurate

metallization

capacicitance for integrated

circuits and packages,”

IEEE -J. Solid-State

Circuits, vol. SC~8, p. 289, Aug. 1973.

T. Sakurai and K. Tamaru,

“Simple

formulas

for two- and threedimensional

capacitances,”

IEEE

~ans.

Electron

Devices,

vol.

ED-30, pp. 183-185,

Feb. 1983.

IEEE JOURNAL

426

[3]

[4]

[5]

[6]

[7]

S. T. Murarka,

“Resistivities

of thin film transition

metal sificides,”

1 Electrochem.

Sot., vol. 129, p. 293, 1982; also “Refractory

silicides

for integrated

circuit s,” J. Vat. Sci. Technol.,

vol. 17,

p. 775, 1980.

U. Kumar,

“Modeling

of distributed

lossless and lossy structures–

A review,” IEEE Trans. Circuits Syst., vol. 2, no. 3, p. 12, 1980.

P. Penfield,

Jr., “Signal delay in RC tree networ~s,”

in Proc. 18th

Design Automation

Conf., 1981, p. 613.

Y. V. Rajput, “Modeling

distributed

RC lines for transient analysis

of complex

networks,”

Znt. J. Elect~on.,

vol. 36, no. 5, p. 709,

1974.

R. C. Reirson and E. C. Bertnolli,

“Time-domain

analysis and measurement

technique

for distributed

R C structures.

II.

Impulse

OF SOLID-STATE

measurement

1969.

H. Betenan,

McGraw Hill,

S. Balabanian,

p. 459.

[8]

[9]

CIRCUITS,

techniques,”

VOL. SC-18, NO. 4, AUGUST

J. Appl.

1983

vol. 40, no. 1, p. 118,

Phys.,

Tables of Integral

Transformation

I. New

1954, p. 259.

Linear Network

Analysis.

New York: Wiley,

Takayasu

Sakurai (S ‘77-M’78),

at the time of publication.

photograph

and biography

York:

1959,

unavailable

Correspondence

A CMOS

RADIVOJE

Magnetic

S. POPOVIC

Field

V&7

Sensor

.&~D HEINRICH

I

P. BALTES

f

2

Abstract–We

made

shows

current

present

in the standard,

a sensitivity

consumption.

transistors

of

a novel,

fully

polysilicon-gate

1.2 V/T

with

The circuit

in a CMOS-differential

integrated

CMOS

technology.

10 V supply

consists

magnetic

voltage

field

2

-

1“

0s

7;

v

The circuit

1:

and 100 PA

of a pair of split-drain

amplifier-like

sensor

P

MOS

F

configuration.

&

i

Fig. 1. Schematic

I.

of the sensor.

INTRODUCTION

By incorporating

a magnetic sensitive structure

as an integral

part of a conventional

silicon

integrated

circuit,

a range of

magnetic sensitive integrated

circuits has been developed.

They

are currently

applied as position sensors (in keyboards,

machine

tool

control,

motors,

etc.), magnetic

probes, acldc current

sensors, etc.

The first magnetic-field

sensitive MOS device was the MOS

Hall element proposed by Gallagher and Corak [ 1 ] . About 103

V/AT

sensitivity y can be achieved in this way [ 2]. The splitdrain MOS transistor

configuration

of the kind proposed

by

Fry and Hoey [3] shows a much higher sensitivity,

VIZ, about

104 V/AT,

prowded

load resistors well within megaohm range

are applied.

It has the disadvantages

of requiring

high load

resistors

and having rather

poor stability

of operation

[4] .

Further information

on split-drain

MOST’s are given in [5] .

In this correspondence

we present

a stable magnetic-field

sensitive integrated

circuit

which enhances the action of the

split-drain

MOS transistor

by combining

two complementary

devices of this type in a judiciously

chosen configuration.

The

sensor

technology

is

1,2

V/T

The

circuit

CMOS

in

0018-9200/83/0800-0426$01

has

1.

two

polysilicon-gate

rules.

supply

The

voltage

and

with

it differs

field

currents

carriers

due

current

in

drain.

The

to

the

one

is connected

plementary

in

both

from

drain

drain

at the

with

conV/AT.

following

as shown

to

the

expense

increasing

are

in Fig.

2.

The

to

of the

current

features.

pairs

planar

leads

well-known

[ 6 ] as shown

transistor

transistors.

force

the

load

it in the

MOS

split-drain

Lorentz

current

1.2 X 104

of

dynamic

perpendicular

in

of

reminiscent

amplifier

complementary

A magnetic

100 #A

achieved

DESCRIPTION

replaced

by a single split-drain

device,

2) The split drains are cross-coupled.

the

CMOS

sensitivity

to a sensitivity

CIRCUIT

However,

The

standard

a structure

differential

Fig.

1)

the

design

corresponds

II.

ances

LGZ

10 V

this

in

6 Vm

at

sumption:

coupling

Manuscript

received December 10, 1982; revised March 1, 1983.

The authors

are with Zentrale

Forschung

und Entwicklung,

Landis and GYR Zug AG, CH-6 301 Zug, Switzerland.

is made

with

surface

affects

deflection

an increase

current

of

the

each

in the

one

of

of

the

other

transistor

to the drain

with

decreasing

current

of the comtransistor,

and vice versa.

Thanks

to this cross.

and

the

the

drain

usual

dynamic

currents

(which

percent/T)

lead to large variations

Fig. 3.

The salient

feature

of the

.00 @ 1983 IEEE

load

are

technique,

of

the

small

order

imbalof

a few

of the output

voltage;

see

new sensor is that the pair of