gates logic

advertisement

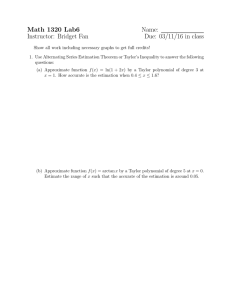

12/21/2018 Lab Lab 6 - ECE 421L Authored by Jared Hayes hayesj18@unlv.nevada.edu October 19, 2015 Lab Description: Design, layout and simulation of a CMOS NAND gate, XOR gate, and Full-Adder. Lab Report: Pre-lab Go through Cadence Tutorial 4 on how to design and layout a 2-input NAND gate here. For this lab we will be using 6u/0.6u MOSFETS. NAND2 Gate Create the schematic for a 2-input NAND gate. Below is a simple diagram of a CMOS NAND gate. Include your initials and current year/semester in your cell names. http://cmosedu.com/jbaker/courses/ee421L/f15/students/hayesj18/Lab6/lab6.htm 1/14 12/21/2018 Lab Create a symbol view for the NAND gate. It should be drawn using the shape tools to look like the actual gate. Create a schematic in order to simulate the operation of the NAND gate. Use pulse sources for the inputs with the first input having double the pulse width and period values as the second input. http://cmosedu.com/jbaker/courses/ee421L/f15/students/hayesj18/Lab6/lab6.htm 2/14 12/21/2018 Lab This should simulate having digital inputs of 00, 01, 10, and 11 for the gate. Create a layout for the 2-input NAND gate. The layout should use standard cell frames and snap together from end-to-end. Allow for extra space in the cell frames for future modification Be sure to include pins for the inputs, outputs, vdd! and gnd! All routed on the metal1 layer. http://cmosedu.com/jbaker/courses/ee421L/f15/students/hayesj18/Lab6/lab6.htm 3/14 12/21/2018 Lab DRC and LVS http://cmosedu.com/jbaker/courses/ee421L/f15/students/hayesj18/Lab6/lab6.htm 4/14 12/21/2018 Lab XOR2 Gate Create the schematic for a 2-input XOR gate. Using the inverter we created in earlier labs can save some time. Create a symbol view for the XOR gate. http://cmosedu.com/jbaker/courses/ee421L/f15/students/hayesj18/Lab6/lab6.htm 5/14 12/21/2018 Lab Create a schematic in order to simulate the operation of the XOR gate. Set it up the same way as the NAND gate. Results http://cmosedu.com/jbaker/courses/ee421L/f15/students/hayesj18/Lab6/lab6.htm 6/14 12/21/2018 Lab Create the layout for the 2-input XOR gate using standard cell frames. DRC and LVS http://cmosedu.com/jbaker/courses/ee421L/f15/students/hayesj18/Lab6/lab6.htm 7/14 12/21/2018 Lab Full Adder Create a schematic for the full-adder using the NAND and XOR gate symbols we made. http://cmosedu.com/jbaker/courses/ee421L/f15/students/hayesj18/Lab6/lab6.htm 8/14 12/21/2018 Lab Create a symbol Layout the full adder by placing the standard cells of the NAND and XOR gates side-by-side. This allows vdd! and gnd! to be routed together. http://cmosedu.com/jbaker/courses/ee421L/f15/students/hayesj18/Lab6/lab6.htm 9/14 12/21/2018 Lab DRC and LVS http://cmosedu.com/jbaker/courses/ee421L/f15/students/hayesj18/Lab6/lab6.htm 10/14 12/21/2018 Lab Create a schematic to simulate the operation of the full adder. http://cmosedu.com/jbaker/courses/ee421L/f15/students/hayesj18/Lab6/lab6.htm 11/14 12/21/2018 Lab The results should match this truth table. http://cmosedu.com/jbaker/courses/ee421L/f15/students/hayesj18/Lab6/lab6.htm 12/14 12/21/2018 Lab Backup: Cadence files and lab report are automatically backed up in my Dropbox folder. http://cmosedu.com/jbaker/courses/ee421L/f15/students/hayesj18/Lab6/lab6.htm 13/14 12/21/2018 Lab The cadence files can be found here: lab6_jh.zip Return to the directory listing of students in EE 421L, Fall 2015 Return to the EE421L Fall 2015 webpage return http://cmosedu.com/jbaker/courses/ee421L/f15/students/hayesj18/Lab6/lab6.htm 14/14